非易失性存储器及其制造方法

文献发布时间:2023-06-19 10:32:14

技术领域

本发明涉及一种存储器及其制造方法,尤其涉及一种具有选择器的非易失性存储器及其制造方法。

背景技术

近年来电阻式随机存取存储器(Resistive Random Access Memory,RRAM)、相变化存储器(Phase Change Memory,PCM)或是磁阻式随机存取存储器(Magnetic RandomAccess Memory,MRAM)的发展极为快速,是目前最受瞩目的非易失性存储器。由于这些存储器具备低功耗、高速运作、高密度、持久度高、存储时间长以及相容于互补式金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺技术的潜在优势,因此非常适合作为非易失性存储器元件。然而,晶体管多电阻(1TnR)的配置例如是一晶体管二电阻(1T2R)配置,在存储元件高密度之后所产生的潜行电流(sneak current)造成误判的问题以及的设定干扰(SET disturb)等问题亟待解决。

发明内容

本发明提供一种非易失性存储器可以避免产生潜行电流(sneak current)以及一晶体管多电阻(1TnR)的元件的设定干扰(SET disturb)等问题。

本发明实施例提出一种非易失性存储器,包括导体层、存储元件以及选择器。选择器位于所述存储元件与所述导体层之间,并与其电性连接。所述选择器包括金属填充层、阻障层以及整流层。金属填充层电性连接所述存储器。阻障层位于所述金属填充层的侧壁与底面。整流层包覆于所述阻障层周围。所述整流层包括第一部分与第二部分。所述第一部分位于所述金属填充层底面的所述阻障层与所述导体层之间。所述第二部分与所述金属填充层将所述金属填充层的侧壁上的所述阻障层夹于其间。所述第一部分比所述第二部分具有较多的金属离子的扩散路径。

依照本发明实施例所述,所述整流层包括TiO

依照本发明实施例所述,所述整流层包括介电常数例如是3.9以上的高介电常数介电材料。

依照本发明实施例所述,所述整流层的所述第一部分具有掺质,且所述第一部分的掺质浓度大于所述第二部份的掺质浓度。

依照本发明实施例所述,所述掺质包括Ar、N、B、P、As、In、Ge或其组合。

依照本发明实施例所述,所述整流层的所述第一部分比所述第二部分具有较多的结构缺陷。

本发明实施例还提出一种非易失性存储器的制造方法,包括在导体层上形成介电层。在所述介电层中形成开口。在所述开口中形成选择器,包括在所述开口中形成底材层,所述底材层包括介电材料以及对所述开口底面的底材层进行处理工艺,使所述底材层形成整流层。所述整流层包括第一部分与第二部分。第一部分位于所述开口的底面。第二部分位于所述开口的侧壁。所述第一部分比所述第二部分具有较多的金属离子的扩散路径。在所述整流层上形成阻障层。在所述开口的所述阻障层上形成金属填充层。在所述介电层上形成存储元件。

依照本发明实施例所述,所述处理工艺包括离子植入工艺。

依照本发明实施例所述,所述离子植入工艺植入的掺质包括Ar、N、B、P、As、In、Ge或其组合。

依照本发明实施例所述,所述离子植入工艺植入的能量为0.1KeV至10KeV。

本发明实施例的非易失性存储器的选择器具有整流层可以做为限流元件,避免产生潜行电流以及一晶体管多电阻(1TnR)的元件的设定干扰等问题。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

图1A至图1F是本发明实施例一种非易失性存储器的制造流程的剖面示意图;

图2A至图2B是本发明另一实施例一种非易失性存储器的制造流程的剖面示意图;

图3A是比较例的没有使用选择器的电阻式随机存取存储器的电特性曲线图;

图3B是实例1的具有选择器的电阻式随机存取存储器的电特性曲线图;

图3C是实例2的具有选择器的电阻式随机存取存储器的电特性曲线图,其中选择器的整流层具有高掺质浓度;

图3D是实例3的具有选择器的电阻式随机存取存储器的电特性曲线图,其中选择器的整流层具有较厚的厚度。

具体实施方式

图1A至图1F是本发明实施例一种非易失性存储器的制造流程的剖面示意图。

请参照图1A,在导体层102上形成介电层104,以使介电层104覆盖导体层102。接着,在介电层104上形成停止层106。导体层102可以是形成在基底上的介电层上。导体层102例如是金属内连线的第一层金属层。导体层102的材料包括金属、金属合金,例如是铜、钛、银或前述的合金。

介电层104的材料包括氧化硅、氮化硅、氮氧化硅或其他合适的绝缘材料。停止层106的材料与介电层104的材料不同。停止层106包括氧化硅、氮化硅、氮氧化硅或者是可作为研磨停止层或蚀刻停止层的其他合适的材料。

接着,请参照图1B,进行光刻蚀刻工艺,于停止层106与介电层104中形成开口108。开口108的底面108b暴露出部分导体层102。在形成开口108之后,于停止层106上以及开口108的侧壁108s与底面108b上形成底材层80。底材层80可以是共形层。底材层80包括介电材料层。介电材料层可以是介电常数例如是3.9以上的高介电常数介电材料。介电材料层可以是氧化物,例如是TiO

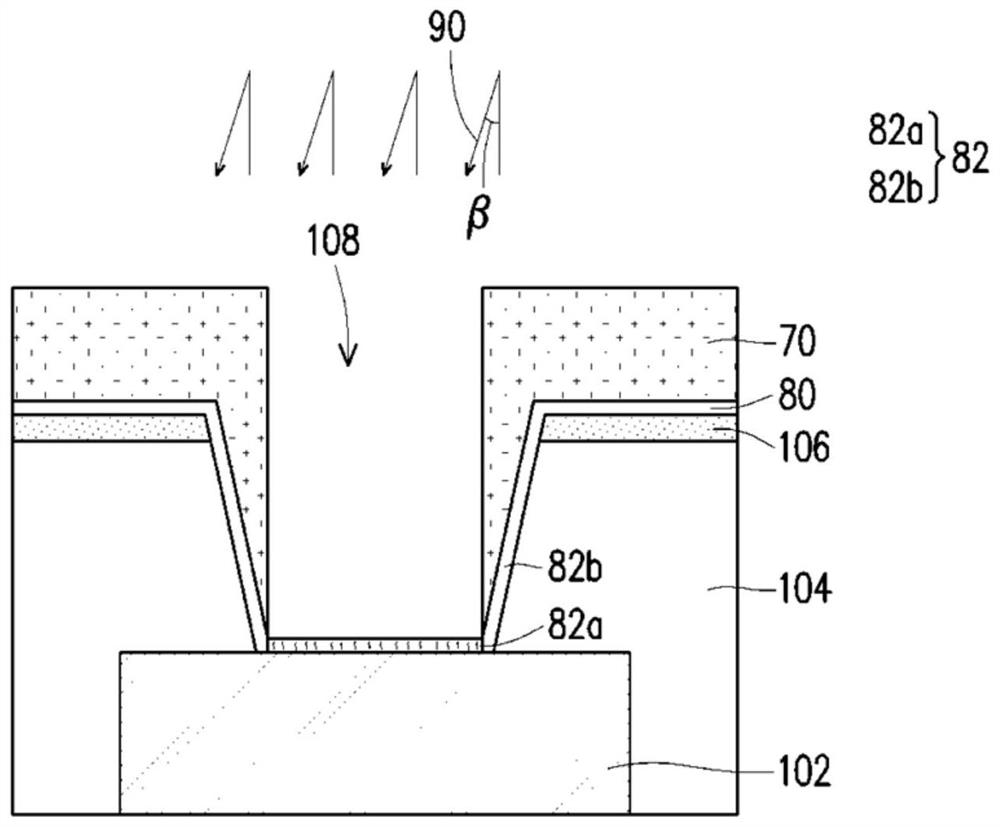

之后,请参照图1C,在底材层80上形成罩幕层70,对底材层80进行处理工艺90,以形成整流层82。罩幕层70覆盖住开口108以外的底材层80,使开口108之中的底材层80裸露出来。罩幕层70例如图案化的光阻层。

处理工艺90例如是离子植入工艺,以将掺质植入于开口108的底面108b的底材层80之中,使其具有掺质,以形成整流层(rectify layer)82的第一部分82a。在一实施例中,离子植入工艺并未将掺质植入于开口108的侧壁108s的底材层80之中,因此其不具有掺质,在开口108的侧壁108s的底材层80将做为整流层82的第二部分82b。第一部分82a比第二部分82b具有较多的结构缺陷,因此具有较多的金属离子的扩散路径。离子植入工艺所植入的掺质为氩、氮、硼、砷、磷、铟、锗或其组合。掺质的浓度例如是1E12离子/平方厘米至1E16离子/平方厘米。离子植入工艺的植入方向与导体层102的表面的法线方向的夹角β可以是0度或是小于30度。离子植入工艺的能量例如是0.1KeV至10KeV。

请参照图1C与图1D,将罩幕层70移除。之后,在底材层80以及整流层82上形成阻障层110。阻障层110的材料可以是钽、钛、氮化钽、氮化钛或其他合适的材料。阻障层110的厚度例如是30埃至150埃。

其后,在阻障层110上形成金属填充层112。金属填充层112可以填满开口108。金属填充层112的包括钨、铜或其他合适的材料。之后,请参照图1E,以停止层106为蚀刻停止层或是研磨停止层,进行回蚀刻工艺或是平坦化工艺以移除停止层106上的金属填充层112、阻障层110以及底材层80。留在开口108之中的金属填充层112a、阻障层110a以及整流层82共同组成选择器120。

请参照图1F,在停止层106上形成存储元件130。在本实施例中,以存储元件130为RRAM 130来说明之。RRAM 130包括由第一电极132、第二电极136及介于其间的可变电阻层(resistance changeable layer)134所构成的金属-绝缘层-金属(MIM)结构。第一电极132与选择器120电性连接。第一电极132与第二电极136的材料例如是氮化钛(TiN)、铂(Pt)、铱(Ir)、钌(Ru)、钛(Ti)、钨(W)、钽(Ta)、铝(Al)、锆(Zr)、铪(Hf)、镍(Ni)、铜(Cu)、钴(Co)、铁(Fe)、钆(Gd)或锰(Mo)。可变电阻层134设置于第一电极132与第二电极136之间。可变电阻层134包括介电材料,例如是氧化铪(诸如HfO或HfO

选择器120包括金属填充层112a、阻障层110a以及整流层82。在一实施例中,金属填充层112a、阻障层110a以及整流层82的顶面可以是共平面,但不限于此。阻障层110a与整流层82包覆金属填充层112a的侧壁与底面。阻障层110a与整流层82可以是共形层。整流层82可以做为限流元件。整流层82为连续层,其包括第一部分82a与第二部分82b。整流层82的第一部分82a位于开口108的底面108b,并且与导体层102物理性接触。第一部分82a位于金属填充层112a的下方,其夹在阻障层110a与导体层102之间,并与其物理性接触。整流层82的第二部分82b位于开口108的侧壁,并与介电层104、停止层106以及第一电极132物理性接触。第二部分82b位于金属填充层112a的侧壁上的阻障层110a与介电层104之间,并与其物理性接触。

在以上的实施例中,选择器120的金属填充层112a、阻障层110a以及整流层82的顶面是共平面。金属填充层112a、阻障层110a以及整流层82的顶面均与RRAM 130的第一电极132物理性接触。

在另一实施例中,金属填充层、阻障层以及整流层的顶面可以不是共平面。举例来说,请参照图2A,选择器为设置在介电层104中的插塞。金属填充层112a、阻障层110a以及整流层82均是位于介电层104中。金属填充层112a的顶面较低,而整流层82与阻障层110a可以向上延伸,而使其顶面凸出于金属填充层112a的顶面。阻障层110a的侧壁与金属填充层112a的顶面形成凹槽R。RRAM的第一电极132填入此凹槽R之中(如图2B所示)。

比较图3A与图3B的结果显示,相较于没有选择器的RRAM,本发明的具有选择器的RRAM有助于改善干扰的问题。比较图3B、图3C与图3D的结果显示,当整流层是通过离子植入工艺将掺质植入底材层(例如介电材料)来形成时,将掺质浓度提升或将整流层的厚度增加,均可以进一步改善干扰的问题。

本发明实施例的非易失性存储器的选择器具有整流层可以做为限流元件,降低选择器的操作电压。本发明实施例的选择器可避免一晶体管多电阻(1TnR)的元件产生潜行电流以及设定干扰(SET disturb)等问题。

- 非易失性存储器电路及其制造方法与操作非易失性存储器单元虚拟接地阵列的方法

- 非易失性存储器装置和制造非易失性存储器装置的方法