一种氧化镓功率器件钝化层及其钝化方法

文献发布时间:2023-06-19 10:32:14

技术领域

本发明属于半导体功率器件技术领域,涉及一种氧化镓功率器件钝化层及其钝化方法。

背景技术

近年来,β- Ga

现有垂直结构Ga

然而,现有垂直结构Ga

发明内容

针对上述现有垂直结构Ga

为解决上述技术问题,本发明采用如下技术方案:一种氧化镓功率器件钝化层,包括:

Ga

SIPOS钝化层,所述SIPOS钝化层设置在所述Ga

氧化镓功率器件钝化层,所述氧化镓功率器件钝化层设置于所述SIPOS钝化层上。

可选的,所述氧化镓功率器件钝化层和所述SIPOS钝化层为同一层。

可选的,所述SIPOS钝化层为SIPOS薄膜。

可选的,所述SIPOS钝化层的厚度为0.1~1μm。

本发明还提供了一种氧化镓功率器件钝化层的制备方法,所述方法包括:

S101.形成Ga

S102.在所述Ga

S103.在所述SIPOS钝化层上形成氧化镓功率器件钝化层。

可选的,在步骤S102中通过沉积的方式在所述Ga

可选的,在步骤S102中通过低压力化学气相沉积工艺或者等离子体增强化学的气相沉积工艺在所述Ga

可选的,步骤S103包括:

对所述SIPOS钝化层进行热退火处理后,形成热退火处理后SIPOS钝化层;

对所述热退火处理后SIPOS钝化层进行图像化处理后,形成所述氧化镓功率器件钝化层。

可选的,步骤S103包括:

采用刻蚀工艺对所述热退火处理后SIPOS钝化层进行处理后,得到持续滞留在所述Ga

利用所述剩余目标物质形成所述氧化镓功率器件钝化层。

可选的,步骤S101包括:

确定Ga

采用RCA标准清洗工艺对所述Ga

本发明的有益效果是:本发明中的一种氧化镓功率器件钝化层及其钝化方法,属于半导体功率器件技术领域,其中氧化镓功率器件钝化层的制备方法,包括:形成Ga

附图说明

图1为本发明一实施例提供的氧化镓功率器件钝化层结构示意图;

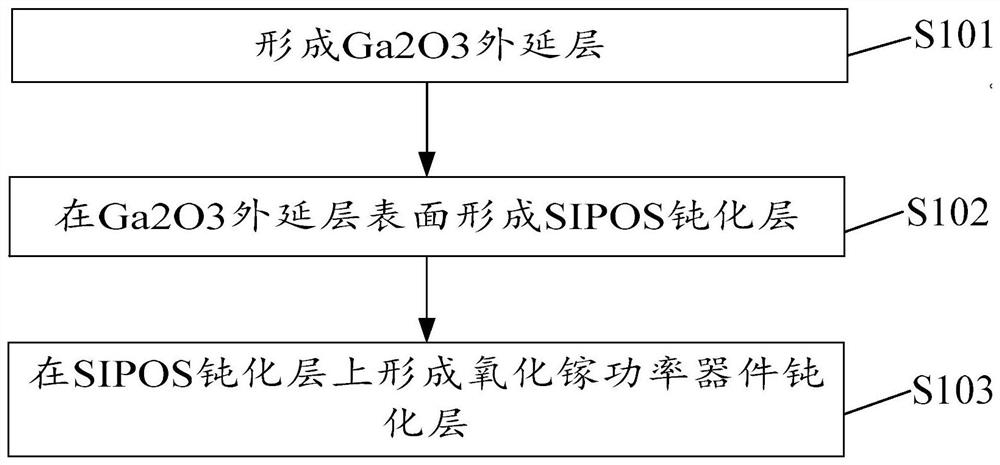

图2为本发明另一实施例提供的氧化镓功率器件钝化层的制备方法流程图;

图3为本发明又一实施例提供的氧化镓功率器件钝化层制备流程图;

其中:1. Ga

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

在本发明的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该发明产品使用时惯常摆放的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

此外,术语“水平”、“竖直”等术语并不表示要求部件绝对水平或悬垂,而是可以稍微倾斜。如“水平”仅仅是指其方向相对“竖直”而言更加水平,并不是表示该结构一定要完全水平,而是可以稍微倾斜。

在本发明的描述中,还需要说明的是,除非另有明确的规定和限定,术语“设置”、“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

首先对本发明所涉及的名词进行解释:

Ga

SBD(SchottkyBarrierDiode,SBD):SBD是肖特基势垒二极管,肖特基二极管是以其发明人肖特基博士(Schottky)命名的。SBD不是利用P型半导体与N型半导体接触形成PN结原理制作的,而是利用金属与半导体接触形成的金属-半导体结原理制作的。因此,SBD也称为金属-半导体(接触)二极管或表面势垒二极管,它是一种热载流子二极管。肖特基二极管是贵金属(金、银、铝、铂等)A为正极,以N型半导体B为负极,利用二者接触面上形成的势垒具有整流特性而制成的金属-半导体器件。

刻蚀:英文为Etch,它是半导体制造工艺,微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。是与光刻 [1] 相联系的图形化(pattern)处理的一种主要工艺。所谓刻蚀,实际上狭义理解就是光刻腐蚀,先通过光刻将光刻胶进行光刻曝光处理,然后通过其它方式实现腐蚀处理掉所需除去的部分。刻蚀是用化学或物理方法有选择地从硅片表面去除不需要的材料的过程,其基本目标是在涂胶的硅片上正确地复制掩模图形。随着微制造工艺的发展,广义上来讲,刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称,成为微加工制造的一种普适叫法。

RCA标准清洗法:RCA标准清洗法是1965年由Kern和Puotinen 等人在N.J.Princeton的RCA实验室首创的,并由此而得名。RCA是一种典型的、至今仍为最普遍使用的湿式化学清洗法。清洗的一般思路是首先去除硅片表面的有机沾污,因为有机物会遮盖部分硅片表面,从而使氧化膜和与之相关的沾污难以去除;然后溶解氧化膜,因为氧化层是“沾污陷阱”,也会引入外延缺陷;最后再去除颗粒、金属等沾污,同时使硅片表面钝化。

退火处理:退火处理主要是指将材料曝露于高温一段很长时间后,然后再慢慢冷却的热处理制程。主要目的是释放应力、增加材料延展性和韧性、产生特殊显微结构等。

当前,β- Ga

由于β- Ga

但是,现有技术中的Ga

以下将结合图1至图3,对本发明实施例所提供的氧化镓功率器件钝化层及其钝化方法进行详细说明。

本发明的实施例提供的氧化镓功率器件钝化层,如图1所示,可以包括:Ga

其中,SIPOS(半绝缘多晶硅)钝化层可以设置在Ga

可选的,氧化镓功率器件钝化层和SIPOS钝化层可以为同一层。比如氧化镓功率器件钝化层和SIPOS钝化层可以属于相同的深度范围或相同的厚度范围。

可选的,SIPOS钝化层可以为SIPOS薄膜。

可选的,SIPOS钝化层的厚度为0.1~1μm。

本发明中的一种氧化镓功率器件钝化层,包括:Ga

在另一种可行的实施例中,本发明还提供了氧化镓功率器件钝化层的制备方法,如图2所示为本发明另一实施例提供的氧化镓功率器件钝化层的制备方法流程图。下面结合图2,对该方法包括的步骤进行具体介绍。

步骤S101、形成Ga

在实际处理过程中,步骤S101可以通过以下子步骤实现:

步骤S1011、确定Ga

具体的,在形成Ga

步骤S1012、采用RCA标准清洗工艺对所述Ga

具体的,由于Ga

步骤S102、在所述Ga

在实际处理过程中,可以在Ga

可以采用低压力化学气相沉积工艺或者等离子体增强化学的气相沉积工艺将Ga

可选的,0.1-1μm的SIPOS钝化层可以为0.1-1μm的SIPOS薄膜。

在实际处理过程中,低压力化学气相沉积(Low Pressure Chemical VaporDeposition,LPCVD)的基本原理是将一种或数种气态物质,在较低压力下,用热能激活,使其发生热分解或化学反应,沉积在衬底表面形成所需的薄膜,可以广泛用于氧化硅、氮化物、多晶硅沉积,过程在管炉中执行,要求也相当高的温度。等离子体增强化学的气相沉积(Plasma Enhanced Chemical Vapor Deposition,PECVD)的基本原理是借助微波或射频等使含有薄膜成分原子的气体电离,在局部形成等离子体,而等离子体化学活性很强,很容易发生反应,在基片上沉积出所期望的薄膜。为了使化学反应能在较低的温度下进行,利用了等离子体的活性来促进反应。因而这种化学气相沉积称为等离子体增强化学的气相沉积。

步骤S103、在所述SIPOS钝化层上形成氧化镓功率器件钝化层。

在实际处理过程中,步骤S103可以通过以下子步骤实现:

步骤S1031、对所述SIPOS钝化层进行热退火处理后,形成热退火处理后SIPOS钝化层。

具体的,由于SIPOS钝化层可以是厚度为0.1-1μm的SIPOS薄膜,因此对SIPOS钝化层进行热退火处理,可以是对SIPOS薄膜进行热退火处理,使其更加致密,从而形成热退火处理后SIPOS钝化层。其中,进行热退火处理的环境中可以包括NO、NO

可选的,热退火处理后SIPOS钝化层可以是淀积有SIPOS的外延片。

步骤S1032、对所述热退火处理后SIPOS钝化层进行图像化处理后,形成所述氧化镓功率器件钝化层。

具体的,步骤S1032可以通过以下过程实现:

步骤S21、采用刻蚀工艺对所述热退火处理后SIPOS钝化层进行处理后,得到持续滞留在所述Ga2O3外延层表面上的剩余目标物质。

具体的,可以采用刻蚀工艺对热退火处理后SIPOS钝化层进行处理,比如先在热退火处理后SIPOS钝化层上进行光刻,形成待退火区域,然后对待退火区域上覆盖的SIPOS进行刻蚀处理后,得到持续滞留在Ga

步骤S22、利用所述剩余目标物质形成所述氧化镓功率器件钝化层。

具体的,可以对剩余目标物质进行清洗处理和吹干处理后,形成氧化镓功率器件钝化层。以此实现通过SIPOS替代传统二氧化硅用于Ga

可选的,氧化镓功率器件钝化层和SIPOS钝化层可以为同一层。比如氧化镓功率器件钝化层和SIPOS钝化层可以属于相同的深度范围或相同的厚度范围。

示例性的,如图3所示,可以先进行Ga

本发明实施例中,本发明的氧化镓功率器件钝化层的制备方法,包括:形成Ga

在一种可行的实施例中,本发明还提供一种电子设备,该电子设备包括前述实施例中的氧化镓功率器件钝化层,或者电子设备包括的氧化镓功率器件钝化层可以由上述任一种钝化方法制备而成。其具体实现方式和技术效果类似,这里不再赘述。

本发明实施例所提供的电子设备,氧化镓功率器件钝化层包括:Ga

优选地,本发明还提供一种计算机可读存储介质,包括程序,该程序在被处理器执行时用于执行上述方法实施例。

在本发明所提供的几个实施例中,应该理解到,所揭露的装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用硬件加软件功能单元的形式实现。

上述以软件功能单元的形式实现的集成的单元,可以存储在一个计算机可读取存储介质中。上述软件功能单元存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)或处理器(英文:processor)执行本发明各个实施例方法的部分步骤。而前述的存储介质包括:U盘、移动硬盘、只读存储器(英文:Read-Only Memory,简称:ROM)、随机存取存储器(英文:Random Access Memory,简称:RAM)、磁碟或者光盘等各种可以存储程序代码的介质。

- 一种氧化镓功率器件钝化层及其钝化方法

- 一种基于第二钝化层钝化方式的双极器件抗辐照加固方法