功率因数校正器

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及电子技术领域,特别是涉及一种功率因数校正器。

背景技术

电磁干扰(Electro Magnetic Interference,简称EMI)是电磁骚扰引起对设备、传输通道或系统性能的下降。电磁干扰包括传导干扰和辐射干扰两部分,其中传导干扰是指电子设备产生的干扰信号通过导电介质或公共电源线互相产生干扰;辐射干扰是指电子设备通过空间耦合把干扰信号传给另一个电网络或电子设备。

通常,在高频电路中会应用开关管、二极管、电感等器件,开关管开通、关断时产生的电压和电流的快速跳变,二极管关断时的反向恢复电流,都具有很宽的频谱含量,从而带来高次谐波,而高次谐波与电感的寄生电容发生震荡,就会通过电感向空间辐射干扰,从而影响电感所在的电子设备或其它电子设备的正常工作。因此,如何消除高频电路的电磁干扰,对于保证电子设备的正常工作具有重要意义。

相关技术中,通常采用屏蔽罩整体包裹电感的方式,屏蔽电感向外辐射的电磁能量,以达到消除高频电路中的电磁干扰的目的,然而这种方式,不易于电感的散热,易导致电感的温度升高过大,且屏蔽罩的成本高,另外,屏蔽层的形状复杂,绝缘处理工艺程序繁琐,因此相关技术有待改进。

发明内容

本发明旨在至少一定程度上解决相关技术中的技术问题之一。

为此,本发明提供一种功率因数校正器,用于解决相关技术中,采用屏蔽罩整体包裹电感的方式,屏蔽电感向外辐射的电磁能量,以达到消除高频电路中的电磁干扰的目的的方式,不易于电感的散热,易导致电感的温度升高过大,且屏蔽罩的成本高,屏蔽层的形状复杂,绝缘处理工艺程序繁琐的技术问题。

本发明一方面实施例提供了一种功率因数校正器,包括:

电感和用于屏蔽所述电感的电磁辐射的屏蔽层;

所述电感包括第一区域和第二区域,其中,所述第一区域的辐射强度大于所述第二区域,所述屏蔽层覆盖所述第一区域。

根据本发明的一个实施例,所述电感为在环形磁芯上绕制导线形成的环形电感,所述屏蔽层为屏蔽环,所述屏蔽环与所述环形电感的外环套接,所述屏蔽环的内部空间在第一方向上的宽度等于所述环形电感的外环直径,或者,所述屏蔽环的内部空间在第一方向上的宽度小于所述环形电感的外环直径。

根据本发明的一个实施例,所述电感为在环形磁芯上绕制导线形成的环形电感,所述屏蔽层为屏蔽环,所述屏蔽环穿设于所述环形电感的内环。

根据本发明的一个实施例,所述屏蔽层具有第一开口和第二开口,其中,所述第一开口的半径大于所述第二开口的半径。

根据本发明的一个实施例,所述屏蔽层包括金属层。

根据本发明的一个实施例,所述第一区域包括多个子区域,所述屏蔽层包括多个子屏蔽层,所述多个子屏蔽层覆盖多个子区域。

根据本发明的一个实施例,所述屏蔽层上设置有开孔。

根据本发明的一个实施例,所述屏蔽层与地连接。

根据本发明的一个实施例,所述电感为共模电感、功率因数校正电感、电抗器中的任意一种。

本发明实施例提供的功率因数校正器,包括电感和用于屏蔽电感的电磁辐射的屏蔽层,通过利用屏蔽层仅覆盖电感的辐射强度较大的区域,从而在有效降低电感向空间辐射干扰,保证电子设备的正常工作的前提下,加强了被屏蔽层屏蔽的电感的散热效果,减小了被屏蔽电感在电路运行过程中的温升,且屏蔽层的成本低,形状简单,大大简化了绝缘处理工艺程序。

附图说明

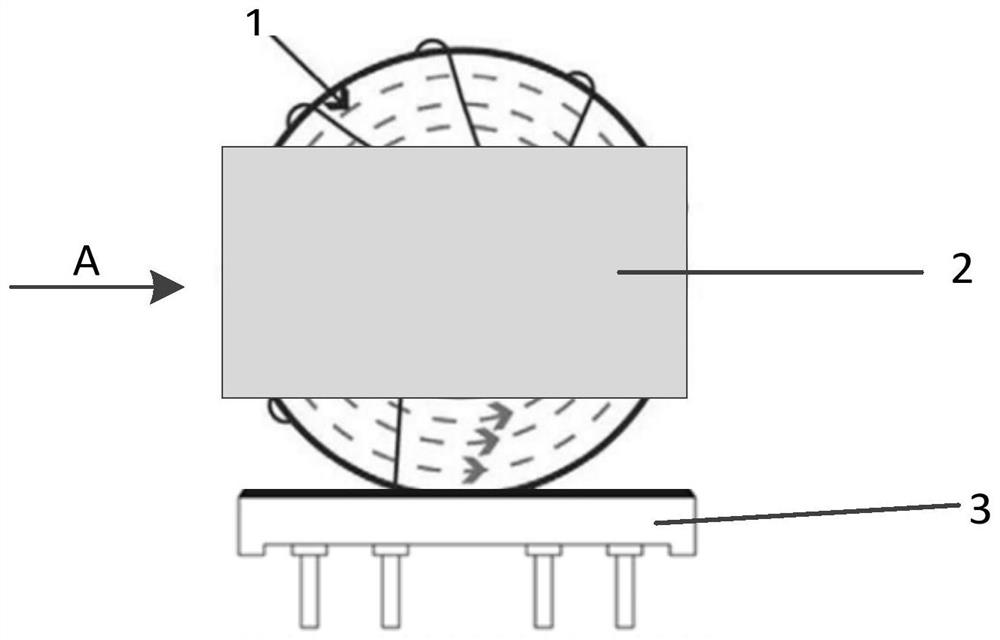

图1是本发明公开的一个实施例的功率因数校正器的部分结构示意图;

图2为本申请公开的一个实施例的功率因数校正器的部分结构的另一示意图;

图3是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图4是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图5是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图6是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图7是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图8是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图9是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图10是本发明公开的另一个实施例的功率因数校正器的部分结构示意图;

图11-14是本发明公开的一个实施例的电磁辐射屏蔽效果的测试结果示意图。

附图标记说明:

电感-1; 屏蔽层-2; 基座-3;

第一开口-21; 第二开口-22; 第一屏蔽环-23;

第二屏蔽环-24; 开孔-4 屏蔽环高度-a;

屏蔽环的内部空间在第一方向上的宽度-b。

具体实施方式

下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

可以理解的是,通常在高频电路中会应用开关管、二极管、电感等器件,开关管开通、关断时产生的电压和电流的快速跳变,二极管关断时的反向恢复电流,都具有很宽的频谱含量,从而带来高次谐波,而高次谐波与电感的寄生电容发生震荡,就会通过电感向空间辐射干扰,从而影响电感所在的电子设备或其它电子设备的正常工作。

以功率因数校正(Power Factor Correction,简称PFC)电路为例,计算机开关电源是一种电容输入型电路,其电流和电压之间的相位差会造成交换功率的损失,此时就需要功率因数校正电路提高功率因数。功率因素校正电路分为主动式PFC电路和被动式PFC电路。而无论是主动式PFC电路还是被动式PFC电路,均会应用电感,那么,PFC电路中也会存在因高次谐波与电感的寄生电容发生震荡,从而通过电感向空间辐射干扰,影响电感所在的电子设备或其它电子设备的正常工作的问题。

相关技术中,通常采用屏蔽罩整体包裹电感的方式,屏蔽电感向外辐射的电磁能量,以达到消除高频电路中的电磁干扰的目的,然而这种方式,不易于电感的散热,易导致电感的温度升高过大,且屏蔽罩的成本高,另外,屏蔽层的形状复杂,绝缘处理工艺程序繁琐。

本申请各实施例针对上述问题,提出一种功率因数校正器,功率因数校正器包括电感和用于屏蔽电感的电磁辐射的屏蔽层,电感包括第一区域和第二区域,其中,第一区域的辐射强度大于第二区域,屏蔽层覆盖第一区域,由此,通过利用屏蔽层仅覆盖电感的辐射强度较大的区域,从而在有效降低电感向空间辐射干扰,保证电子设备的正常工作的前提下,加强了被屏蔽层屏蔽的电感的散热效果,减小了被屏蔽电感在电路运行过程中的温升,且屏蔽层的成本低,形状简单,大大简化了绝缘处理工艺程序。

下面参考附图描述本申请实施例的功率因数校正器。

图1为本申请公开的一个实施例的功率因数校正器的部分结构示意图。图2为本申请公开的一个实施例的功率因数校正器的部分结构的另一示意图。其中,图1为前视图,图2为与图1对应的俯视图。如图1和图2所示,本申请实施例的功率因数校正器,包括:

电感1和用于屏蔽电感1的电磁辐射的屏蔽层2;

电感1包括第一区域和第二区域,第一区域的辐射强度大于第二区域,屏蔽层2覆盖第一区域。

其中,电感1可以是共模电感、PFC电感、电抗器等任意作为EMI干扰源的电感,本申请对此不作限制。从外形来说,电感1可以为在环形磁芯上绕制导线形成的环形电感、E形电感、棒性电感等,图1和图2以电感1为环形电感为例进行示意。

在某些实施例中,屏蔽层2可以包括金属层,其中,金属层可以由任意能够屏蔽电感1的电磁辐射的金属材料,比如,铜箔或其它任意低阻抗金属材料制成,本申请对此不作限制。另外,屏蔽层2还可以包括绝缘层等其它层,本申请对此不作限制。

具体的,功率因数校正器的电感1向外辐射的干扰能够在屏蔽层2上引起很大的涡流,由于涡流的去磁作用,因此屏蔽层2处的磁场大大减弱,从而电感1向外辐射的干扰无法穿出屏蔽层2外,从而能够抑制电感1向空间辐射干扰。同样道理,屏蔽层2外的干扰也不能穿入屏蔽层2内,从而可以保证功率因数校正器所在的电子设备和其它电子设备的正常工作。

具体实现时,本申请实施例提供的功率因数校正器可以采用现有技术中的任意主动式功率因数校正电路或被动式功率因数校正电路,本申请对此不作限制。也就是说,本申请不对功率因数校正器中,电感及其它元器件的类型、数量、连接关系等进行限制。本申请中仅是通过在功率因数校正器的电感1的辐射强度较大的区域上覆盖屏蔽层2,从而对电感1进行局部屏蔽,以有效降低电感向空间辐射干扰,保证电子设备的正常工作。

可以理解的是,屏蔽层2对电感1进行整体屏蔽时,屏蔽层2将电感1进行整体包裹,会形成密闭空间,电流在电感1上损耗产生的热量难以向外传递,会引起电感1发热严重,导致电感1温度升高过大,且屏蔽层2整体覆盖电感1,覆盖面积大,还会导致屏蔽层2的成本较高,另外,屏蔽层面积大,形状复杂,还会导致绝缘处理工艺程序繁琐。

而电感1向空间辐射干扰时,并不是所有的区域的辐射强度都很大,而是有的区域的辐射强度大,有的区域的辐射强度小,那么,在本申请实施例中,可以设置一个电磁辐射阈值,并将电感1的辐射强度大于电磁辐射阈值的区域划为第一区域,将辐射强度不大于电磁辐射阈值的区域划为第二区域,从而在对电感1进行电磁屏蔽时,仅对辐射强度大于电磁辐射阈值的第一区域覆盖屏蔽层,从而在降低电感1向空间辐射干扰的同时,增加电感1与外部空间直接接触的面积,加强被屏蔽层2屏蔽的电感1的散热效果。

其中,电磁辐射阈值可以根据需要设置。

可以理解的是,电磁辐射阈值设置的越小,第一区域的面积越大,即屏蔽层需要覆盖的面积越大,对电感1的屏蔽效果越好,但是屏蔽层的成本更高,且更不利于电感的散热,那么,在实际应用中,可以根据对屏蔽层的成本的要求、电感的屏蔽效果的要求及电感的散热要求,灵活设置电磁辐射阈值的大小,由于第一区域的大小随电磁辐射阈值的大小相应变化,因此屏蔽电感1所需的屏蔽层的面积也可以进行灵活设置。

本申请实施例中,通过利用屏蔽层2对电感1的电磁辐射强度较大的第一区域进行局部屏蔽,在不影响屏蔽层2对电感1的屏蔽性能的前提下,增加了电感1与外部空间直接接触的面积,加强了被屏蔽层2屏蔽的电感1的散热效果,减小了被屏蔽电感1在电路运行过程中的温升,且屏蔽层2的使用成本相较于将电感1进行全屏蔽时大大降低,且屏蔽层2面积小,形状简单,大大简化了绝缘处理工艺程序,优化了对电感1进行全屏蔽时的散热效果差、成本高、工艺程序繁琐的问题。

下面以电感1为在环形磁芯上绕制导线形成的环形电感为例,对本申请实施例中屏蔽层2的设置方式进行说明。

可以理解的是,环行电感是通过在环形磁芯上绕制导线形成的,由于环形磁芯上绕制的导线向外发射电磁能量,而导线在环形磁芯的内环的绕制密度大于外环的绕制密度,因此,环形电感的辐射强度由环形电感的内环开始向外环方向逐渐降低。那么本申请实施例中,对于环形电感来说,辐射强度大于电磁辐射阈值的第一区域位于环形电感的内环附近,且第一区域的面积随电磁辐射阈值的设置大小而变化。

那么,在本申请实施例中,屏蔽层2可以为屏蔽环,屏蔽环能够覆盖环形电感1的内环附近的区域,以对电感1的强干扰部位进行局部屏蔽。

具体实现时,如图1和图2所示,屏蔽环可以与环形电感1的外环套接,屏蔽环的内部空间在第一方向上的宽度等于环形电感的外环直径。

其中,第一方向为环形电感的内环或外环的水平对称轴所在方向,即图1和图2所示的A方向。

可以理解的是,本申请实施例中,如图1、图3和图4所示,功率因数校正器的电感1可以配置在基座3上(图2未示出)(本申请以基座3为水平设置为例进行说明),屏蔽环与环形电感的外环套接时,套接方向可以是任意方向,比如,如图1、图3和图4所示的屏蔽环的横切面方向与基座所在平面方向平行,或者,也可以是屏蔽环的横切面方向与基座所在平面的方向呈一定夹角,等等。在实际应用中,为了方便将屏蔽层2安装到环形电感1上,可以采用屏蔽环的横切面方向与基座所在平面方向平行的方式,将屏蔽环套接在环形电感1的外环上。

本申请实施例中,第一方向为环形电感的内环或外环的水平对称轴所在方向,是基于屏蔽环的横切面方向与基座所在平面方向平行时的情况限定的,在其它实施例中,第一方向可以为环形电感的内环或外环的其它对称轴所在的方向。也就是说,第一方向为环形电感的内环或外环的任一对称轴所在的方向,第一方向具体为哪个方向,与屏蔽环套接在环形电感的外环上时的套接方向有关,若屏蔽环与环形电感的外环套接时,屏蔽环的横切面方向与基座所在平面的方向平行,则第一方向为环形电感的水平对称轴所在的方向,若屏蔽环与环形电感的外环套接时,屏蔽环的横切面方向与基座所在平面的方向垂直,则第一方向为环形电感的竖直对称轴所在的方向。

本申请实施例中,屏蔽环与环形电感1的外环套接时,通过将屏蔽环的内部空间在第一方向上的宽度设置为等于环形电感的外环直径,从而屏蔽环能够如图1所示,套接在环形电感的中部,实现对环形电感的辐射强度较大的第一区域的屏蔽。

值得注意的是,屏蔽环与环形电感1的外环套接时,屏蔽环的横切面的形状可以如图2所示,为矩形,或者,屏蔽环的横切面的形状还可以为椭圆形或其它形状。在实际应用中,可以根据环形电感的磁芯的尺寸等参数根据需要灵活设置屏蔽环的横切面形状,本申请对此不作限制。

需要说明的是,屏蔽环与环形电感的外环套接,且屏蔽环的内部空间在第一方向上的宽度等于环形电感的外环直径时,屏蔽环的高度可以根据需要设置。比如,如图1所示,屏蔽环的高度可以等于环形电感的内环直径,从而屏蔽环能够覆盖环形电感的内环附近区域,或者,如图3所示,屏蔽环的高度可以小于环形电感的内环直径,此时,屏蔽环仅覆盖环形电感的内环附近的部分区域。

相比图1所示的屏蔽环的设置方式,图3所示的设置方式能够达到更好的散热效果,更好的减小被屏蔽电感1在电路运行过程中的温升,且屏蔽层2的使用成本相较于图1所示的方式更低,但是由于未对第一区域进行全部覆盖,因此相比图1所示的屏蔽环的设置方式,屏蔽效果稍差。在实际应用中,可以根据需要,灵活设置屏蔽环的高度,以满足不同的需求。比如,在对电感的屏蔽效果要求较低,对电感的散热效果要求高时,可以将屏蔽环的高度设置为小于环形电感内环直径的值,以提高散热效果,当对电感的屏蔽效果要求较高,对电感的散热效果要求较低时,可以将屏蔽环的高度设置为大于环形电感内环直径的值,以提高屏蔽效果。

在某些实施例中,如图4所示,屏蔽环与环形电感的外环套接时,屏蔽环的内部空间在第一方向上的宽度也可以小于环形电感的外环直径,此时屏蔽环套接在环形电感的一侧,屏蔽环仅覆盖环形电感内环附近的部分区域,因此相比图1所示的屏蔽环的设置方式,图3所示的屏蔽环的设置方式的屏蔽效果稍差。

在某些实施例中,电感1为环形电感时,屏蔽层2可以如图5所示,具有第一开口21和第二开口22,且屏蔽层2可以设置为如图1-4所示的上下等宽的环形,即,第一开口21和第二开口22的半径相等。或者,如图5所示,屏蔽层2可以设置为上窄下宽的喇叭形,即,第一开口21的半径大于第二开口22的半径,从而方便将屏蔽层2安装到环形电感1上。

在某些实施例中,屏蔽环还可以如图6所示,穿设于环形电感的内环,即屏蔽环从环形电感的内环穿过,包裹在环形电感的部分磁芯上。需要说明的是,屏蔽环穿设环形电感的内环时,屏蔽环的高度(图6中的a)、屏蔽环的内部空间在第一方向上的宽度(图6中的b)可以根据环形电感内环、外环、磁芯的尺寸等参数进行适应性调整。

另外,屏蔽环还可以如图7所示,为扇形环,从而使得屏蔽环与环形电感的尺寸更匹配,以减小屏蔽环所占的空间。其中,扇形环的大扇形的半径、小扇形的半径、扇形环的圆形切面的内径等尺寸可以根据环形电感的内环、外环、磁性的尺寸进行设置。

需要说明的是,屏蔽环穿设于环形电感的内环时,屏蔽环可以设置在内环的任意部位,比如如图6或7所示,屏蔽环设置在环形电感的左侧,或者,屏蔽环还可以设置在环形电感的上侧,右侧等等部位,屏蔽环覆盖环形电感的面积也可以根据实际应用中对散热和屏蔽效果的要求进行适应性调整,本申请对屏蔽环的设置部位和屏蔽环覆盖环形电感的面积不作限制。

可以理解的是,本申请实施例中,可以如上述实施例所述,利用一块屏蔽材料,覆盖电感1的电磁辐射强度较高的区域。在某些实施例中,还可以将电磁辐射强度较高的第一区域划分为多个子区域,利用多块屏蔽材料,对电感1的多个电磁辐射强度较高的子区域分别进行覆盖。即,在本申请实施例中,第一区域包括多个子区域时,屏蔽层2包括多个子屏蔽层,多个子屏蔽层覆盖多个子区域。从而相比利用一整块屏蔽材料覆盖电感的多个电磁辐射较高的区域,在不影响屏蔽层2对电感1的屏蔽性能的前提下,进一步增加电感1与外部空间直接接触的面积,加强被屏蔽层2屏蔽的电感1的散热效果,减小被屏蔽电感1在电路运行过程中的温升,且进一步节省屏蔽层2的使用成本,简化绝缘处理工艺程序。

相应的,电感为环形电感时,可以将环形电感的辐射强度较高的内环附近的区域分为多个子区域,进而通过多个屏蔽环,对多个子区域分别进行屏蔽。

比如,如图8所示,可以利用两个屏蔽环,即图8所示的第一屏蔽环23和第二屏蔽环24,对环形电感1的电磁辐射强度较高的区域进行覆盖。

其中,第一屏蔽环23与环形电感的外环的上部套接,第二屏蔽环24与环形电感的外环的下部套接。第一屏蔽环23和第二屏蔽环24的内部空间在第一方向上的宽度可以等于环形电感的外环直径,或者小于环形电感的外环直径,第一屏蔽环23和第二屏蔽环24的高度可以根据需要设置。相比图1所示的利用一块屏蔽层屏蔽环形电感的方式,图8所示的屏蔽方式能够达到更好的散热效果。

需要说明的是,利用多个屏蔽环屏蔽环形电感时,多个屏蔽环可以与利用一个屏蔽环屏蔽环形电感时的方式类似,屏蔽环的套接方向为任意方向,比如,如图8所示的屏蔽环的横切面方向与基座所在平面方向平行,或者,也可以是屏蔽环的横切面方向与基座所在平面的方向呈一定夹角,等等。在实际应用中,为了方便将屏蔽层2安装到环形电感1上,可以采用屏蔽环的横切面方向与基座所在平面方向平行的方式,将屏蔽环套接在环形电感1的外环上。

另外,利用多个屏蔽环分别与环形电感的外环套接时,多个屏蔽环的两个开口的半径可以相同,也可以不同,本申请对此不作限制。

或者,如图9所示,可以利用两个屏蔽环,即图9所示的第一屏蔽环23和第二屏蔽环24,对环形电感1的电磁辐射强度较高的区域进行覆盖。其中,第一屏蔽环23与第二屏蔽环24均穿设于环形电感的内环,第一屏蔽环23设置在环形电感的左侧,第二屏蔽环24设置在环形电感的右侧。相比图6所示的利用一块屏蔽层屏蔽环形电感的方式,图9所示的屏蔽方式能够达到更好的屏蔽效果。

需要说明的是,利用图9所示的两个屏蔽环穿设于环形电感的内环的方式屏蔽环形电感时,与图6所示的屏蔽方式类似,屏蔽环的高度、屏蔽环的内部空间在第一方向上的宽度等参数可以根据环形电感内环、外环、磁芯的尺寸等参数进行适应性调整。另外,屏蔽环可以设置在环形电感的任意部位,比如如图9所示,两个屏蔽环分别设置在环形电感的左侧及右侧,或者,两个屏蔽环还可以设置在环形电感的上侧及下侧,等等,本申请对此不作限制。

需要说明的是,本申请上述实施例所示的屏蔽环屏蔽环形电感的方式,仅是示意性说明,不能作为对本申请技术方案的限制,本领域技术人员在此基础上,可以根据需要任意设置屏蔽层屏蔽电感的方式,此处对此不作限定。

在某些实施例中,还可以如图10所示,在屏蔽层2上设置开孔4,从而在不影响屏蔽层2对电感1的屏蔽效果的前提下,进一步增强被屏蔽电感1的散热效果,节省屏蔽层2的使用成本。

其中,开孔的形状可以如图10所示,为椭圆形,或者,也可以为其它任意形状,开孔的位置和数量也可以根据需要任意设置,本申请对此不作限制,只要开孔的形状、位置和数量不影响电感1的干扰信号在屏蔽层2上形成涡流即可。

在某些实施例中,屏蔽层2可以与地连接,从而通过地球的自由电荷中和屏蔽层2上的正电荷或负电荷,达到电场屏蔽的目的。

下面以设置在空调中的功率因数校正器为例,对本申请实施例提供的功率因数校正器的电磁辐射屏蔽效果进行说明。

可以理解的是,针对空调中的功率因数校正器,其传导干扰的发射主要由PFC电感向外辐射干扰,耦合至敏感导线。若不对PFC电感进行屏蔽,仅处理敏感线体,比如在空调的电源线上、内外机互联线上绕入3个磁环,则其传导干扰测试结果如图11和图12所示。

由图11和图12的测试结果可知,空调的传导干扰的裕量仅为3.80分贝(dB),此时空调受PFC电感向外辐射的干扰影响较大,存在较大安全风险,且此时空调运行时,电感温度为78℃。

若不对敏感线体进行处理,而采用屏蔽层对电感进行全部屏蔽的方式,则空调的传导干扰可以被大幅度抑制,但是空调运行时的电感温度为115℃。即采用屏蔽层将电感全部覆盖的方式,能够降低电感向空间辐射干扰,但是会导致电感升温过大。

而若采用屏蔽层对电感进行局部屏蔽的方式,如图1所示,在电感的局部覆盖铜箔,则空调的传导干扰的测试结果如图13和图14所示。

由图13和图14的测试结果可知,采用本申请实施例提供的对电感进行局部屏蔽的方式后,空调的传导干扰裕量在11dB以上,且此时空调运行时,电感温度为80℃,与对敏感线体进行处理时的电感温度相差不大。即采用屏蔽层将电感进行局部覆盖,大幅度的降低了空调传导干扰的发射幅值,且优化了对电感进行全部屏蔽时的电感温升过大的问题。

在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

在本发明中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

- 空调功率因数校正器控制方法、控制器及功率因数校正器

- 用于功率因数校正器中的过压保护电路及功率因数校正器