气体传感器

文献发布时间:2023-06-19 11:27:38

技术领域

本公开涉及气体传感器,特别地但不限制于微机械加工的金属氧化物气体传感器。

背景技术

金属氧化物(MOX)气体传感器通常基于将金属氧化物膜沉积到限定在合适的衬底上或合适衬底内的感测电极上。微加工的MOX气体传感器通常包含膜、膜内的加热器元件,以及直接接触金属氧化物(MOX)层的电极。图1中示出了MOX气体传感器的可能结构,其中,MOX层沉积在膜上,与通过深反应离子蚀刻(DRIE)或湿法蚀刻(参见例如:D.Briand等,“Design and fabrication of high temperature micro-hotplates for drop-coatedgas sensors”,Sensors and Actuators B,68,pp.223-233,2000)所形成的腔体相对。图1中所描绘的特定示例示出了能够通过湿法蚀刻实现的倾斜壁。垂直壁能够通过DRIE实现。加热器将感测层加热到与气体发生化学或物理反应所需的特定温度。在存在气体的情况下,感测层(即MOX层)改变了其电阻/电导率。测量可以以叉指状构造来布置的电极两端的电阻。该膜用于热隔离MOX层和加热器以显著地降低功耗。能够通过使用多种技术来沉积MOX层,诸如滴涂、喷墨、化学气相沉积(CVD)或丝网印刷,前两种是最常用的。该膜能够由电介质诸如氮化硅或氧化硅形成。衬底通常为硅,但其他半导体材料也是可以的。

在现有技术中已经表明可以使用金电极或铂电极。金或铂的这种额外的沉积增加了工艺复杂性,并且增加了装置的生产成本。此外,金和铂都不是CMOS兼容的(由于在半导体带隙中可能会形成深阱),并且这种层后CMOS的工艺集成的问题在成本和供应链角度上存在挑战。

发明内容

本公开一般涉及微加热板,所述微加热板包括膜、膜内的加热器元件以及与金属氧化物(MOX)层直接接触的多晶硅(例如叉指状)电极。

根据一个实施例,气体感测装置包括衬底,该衬底包括蚀刻腔体部分和衬底部分。

根据一个实施例,该气体感测装置包括设置在衬底上的电介质层。

根据气体感测装置的一个实施例,电介质层包括电介质膜,其中该电介质膜与衬底的蚀刻腔体部分相邻。

根据一个实施例,气体感测装置包括位于电介质层内的加热器。

根据一个实施例,气体感测装置包括用于感测气体的材料。

根据一个实施例,气体感测装置包括与用于感测气体的材料相联接的一个或更多个多晶硅电极。

根据本公开内容的一个方面,设置了一种气体感测装置,该气体感测装置包括衬底、电介质层、加热器、材料,以及一个或多个多晶硅电极;所述衬底包括蚀刻腔体部分和衬底部分;所述电介质层被设置在衬底上,其中,该电介质层包括电介质膜,其中,所述电介质膜与衬底的蚀刻腔体部分相邻;所述加热器位于电介质层内;所述材料用于感测气体;所述一个或多个多晶硅电极与用于感测气体的材料耦合。

特别地,术语“气体传感器”和“气体感测装置”当前指示同一主题。结合气体传感器公开的特征和实施例也能够结合气体感测装置来实施,反之亦然。

多晶硅电极可以配置为测量用于感测气体的材料的电阻。

多晶硅电极可以是高掺杂的。换句话说,该电极可以包括掺杂浓度等于或大于10

多晶硅电极可以包括多个叉指状结构,或指状物。

至少一些叉指状结构的宽度和/或所述多个叉指状结构内的相邻叉指状结构之间的距离可以具有亚微米尺寸。

多晶硅电极可以用CMOS兼容工艺形成。

术语“CMOS兼容工艺”涵盖了CMOS工艺内所使用的处理步骤,以及涵盖了与CMOS工艺分开地执行、但利用了可用于CMOS处理步骤中的处理工具的某些处理步骤。

互补金属氧化物半导体(CMOS)被用于制造集成电路。CMOS术语是指用于制造集成电路的硅技术。CMOS工艺确保了在不同级上(晶圆级、晶圆间、批次间)处理相同晶体管(高至数十亿)的高精度、大规模制造、非常低的成本和高再现性。CMOS在质量和可靠性上都具有高标准。CMOS特征尺寸小于2微米,并且可以低至10nm。

并非所有的硅技术都是CMOS技术。非CMOS技术的示例包含:实验室技术(与铸造技术不同)、丝网印刷技术、例如制成流体通道所采用的生物技术、MEMS技术、超高压垂直功率装置技术、使用不与CMOS兼容的材料(诸如金、铂或放射性材料)的技术。例如,使用非CMOS步骤(诸如电镀电极)或通过使用后CMOS步骤(诸如剥离)来限定电极具有以下缺点,即电极指的尺寸和节距在规格方面要大得多(例如2微米以上)。

至少一个多晶硅电极可以与用于感测气体的材料直接接触。多晶硅层可以在CMOS序列内形成而不是在CMOS之后或CMOS之前或者使用非CMOS工艺形成。因此,可以实现电极宽度和节距的小得多的尺寸,以及可以实现这种尺寸的好的多的再现性。

装置可以包括倒装芯片配置。该装置可以用倒装芯片配置封装。在现有技术的装置中,金和铂的沉积会伴随显著的产量减少以及增加的工艺复杂性。在倒装芯片配置中,使用多晶硅作为叉指状电极导致制造工艺的主要简化、成本降低以及较高的产量。

倒装芯片配置还允许在硅衬底顶部上的可渗透膜的晶圆级放置,以保护金属氧化物气体感测层。这也减小了湿度和中毒的影响。倒装芯片配置还使得能够经由焊球、焊点或铜柱来连接电子电路(ASIC)。有利地,这降低了形状因子并消除了键合线。这种配置还可以允许晶圆级或芯片级封装。

含有驱动、读取、转换和处理电路系统的ASIC可以通过倒装芯片配置中的焊球(或焊点)或者通过使用标准配置中的硅通孔来附接到传感器。ASIC可以包含温度和/或湿度传感器。

加热器可以包括CMOS材料。可选地,CMOS材料可以是多晶硅、铂、钛、钨中的任一种或这些的组合。

加热器可以形成在多晶硅电极下面(或下方)。

电介质膜可以包括蚀刻凹部,并且用于感测气体的的材料可以位于电介质膜的蚀刻凹槽部分内。凹槽可以形成在膜内、膜的表面之一的下方,并且气体感测(或MOX)层可以限制在凹槽内,以与叉指状多晶硅电极形成电接触和物理接触。MOX可以沉积在膜的蚀刻凹部内,并且放置在加热器上方/下方,但不与加热器进行物理连接。为了控制凹槽的深度,可以使用蚀刻停止层(诸如氮化硅层)。该氮化硅层还可以将加热器与金属氧化物(MOX)分隔,并且可以另外用作膜内的应力消除层。

MOX层可以完全嵌入膜中,以使得将MOX层完全限制在蚀刻凹槽和腔体内。MOX层表面因此低于或远远低于膜的表面。这允许了更好的限制,这可以提高装置的可再现性和可靠性。限制MOX层减少了MOX层在膜表面上的扩展。在现有技术的装置中,这种扩展会导致可靠性和可再现性问题,并且还增加了热损失,并因此增加了功耗。

有利地,本公开设置了较小尺寸的MOX层,并因此设置了较小尺寸的微热板。将MOX层限制在腔体中还导致:

i)较好的可再现性;

ii)可靠性(因为MOX层将暴露于较小的温度梯度);以及

iii)较低的功耗。

该气体感测装置还可以包括位于电介质膜顶部表面上的多个第一蚀刻停止层,每个第一蚀刻停止层位于多个电极上方。这种蚀刻停止层可以横向地限定凹槽,并且可以将MOX层定位并限制在加热器上方。与膜层中的其余电介质相比,蚀刻停止层对所使用的蚀刻剂具有较高的电阻。

每个第一蚀刻停止层可以彼此横向地间隔,或者可以在表面处形成环形或封闭形状。这有助于将凹槽横向地限定在电介质膜内,以避免MOX层朝向膜的边缘扩展。蚀刻停止层还可以帮助将腔体限定在衬底内。

蚀刻凹部可以由多个第一蚀刻停止层横向地限定或限制。

气体感测装置还可以包括位于电介质层内的至少一个第二蚀刻停止层,每个第二蚀刻停止层都位于多个电极以下。第二蚀刻停止层可以垂直地限定气体感测材料的深度并且可以优选地将MOX层与加热器隔离。

电极下方的至少一个第二蚀刻停止层可以横向地延伸穿过整个电介质膜区域。蚀刻停止层可以提供应力消除,并且因此横向延伸通过整个膜的蚀刻停止层能够强化该膜。第二蚀刻停止层可以延伸通过电介质层的整个宽度,提供应力消除并通过电介质层强化。

这种蚀刻停止层所使用的材料可以例如是氮化硅。形成该蚀刻停止层的优选方式是LPCVD(低压化学气相沉积)。

电介质膜的蚀刻凹部可以形成在电介质层的前侧上。这允许了非倒装芯片配置中的蚀刻凹槽。电介质膜的蚀刻凹部可以形成在衬底的蚀刻腔体部分之上。

电介质膜的蚀刻凹部可以形成在电介质层的背侧上。这允许在倒装芯片配置中的蚀刻凹槽。电介质膜的蚀刻凹部可以形成在衬底的蚀刻腔体部分内。

可以通过使用至少一个蚀刻停止层来对电介质膜的一部分进行湿法蚀刻来形成蚀刻凹部,以防止进一步的横向或垂直蚀刻。

替代地,可以通过使用至少一个蚀刻停止层来对电介质膜的一部分进行干法蚀刻或干法蚀刻和湿法蚀刻的组合来形成蚀刻凹部,以防止进一步的横向或垂直蚀刻。

在通过对电介质膜使用附加湿法蚀刻来进行腔体蚀刻期间,蚀刻凹部可以与膜同时(在同一步骤中)形成。湿法蚀刻将不使用任何的蚀刻停止层或电极。这种形成凹部的方法的优点在于,蚀刻腔体(以限定膜)和蚀刻凹部(在其中限制了气体感测层)在同一步骤内形成。

蚀刻凹部可以在多晶硅电极下面延伸。这允许气体感测材料与电极之间更多的接触,并且能够提高器件的灵敏度。

蚀刻凹部不可以直接接触加热器,以避免用于感测气体的材料与加热器的电连接。

用于感测气体的材料可以在多晶硅电极下面延伸。换句话说,气体感测材料(MOX)的主要部分被放置在电极下方。这允许电极更接近气体感测材料的表面。这增加了装置的灵敏度。将气体感测材料部分地或全部地嵌入膜中的特征的优点在于,电极更接近气体感测材料的表面,并且更好地控制在气体感测材料的膜中的尺寸、形状以及位置。

用于感测气体的材料可以不在电介质膜的上表面上方延伸。替代地,用于感测气体的材料可以完全限制在电介质膜的上表面下方。

用于感测气体的材料可以嵌入在电介质膜中。换句话说,用于感测气体的材料不会延伸超过电介质膜的表面,并且可以完全嵌入电介质膜中。

用于感测气体的材料可以不在多晶硅电极下面形成。换句话说,用于感测气体的材料不直接在电极下面或下方形成,并且可以仅形成在电极上方并在电极之间的间隙中向下延伸。这能够使加工工艺更简单,并为电极提供机械支撑。

多晶硅电极可以包括第一多晶硅层,并且加热器可以包括第二多晶硅层。

多晶硅电极可以包括第一多晶硅层和第二多晶硅层。

多晶硅电极可以包括第一对电极和第二对电极,所述第一对电极包括叉指状电极,所述第二对电极在第一对电极之间交错。所述第一对电极可以配置为使得在它们两端施加电流偏置,并且第二对电极可以配置为测量它们之间的电压。

优选地,这种四路电极配置可以包括两组叉指状电极和在两个叉指状电极的指状物之间交错的两个电极。可以跨两个叉指状电极施加电流偏置,并且可以测量跨两个交错电极的电压。在这种布置中使用多晶硅是优选的,因为多晶硅图案化技术允许指状物的良好分辨率,并且能够将电极封装在小的空间中。

替代地,也可以使用其他电极配置,包括具有四个矩形平行电极,其中,电流偏置被施加到最外电极,而在内侧两个电极上测量电压。几种其他电极设计也是可以的。

CMOS技术提供多晶硅宽度(其通常限定了CMOS晶体管的MOS栅极的长度)作为制造工艺中可控的最小尺寸。因此,能够制造具有亚微米尺寸宽度的多晶硅电极。电极相邻指状物之间的距离也可以为亚微米量级。该纵横比导致电极的密集得多的结构,这进一步降低了气体感测层的电阻。这在MOX层的电阻非常高(MΩ范围)的情况下是特别有用的,并且高纵横比允许所以所述电阻被降低至1MΩ以下。

第一对电极可以包括用于电流流过MOX气体感测层的两个连接以及用于气体感测层的电阻或电压测量的另两个连接。这允许去除接触电阻的不期望影响。这种接触电阻能够引入产量损失和器件与器件间或批次与批次间的不均匀性。接触层也能够随着时间漂移。此外,其电阻不受化学反应的影响,并且因此对特定气体的灵敏度和选择性可能会降低或恶化。

有利地,这种四路测量导致了去除接触电阻,并因此增加了灵敏度、选择性并增强可靠性,因为接触电阻能够随着时间退化。这还降低了感测电阻,以使测量电路不太复杂。

至少一些多晶硅电极的宽度可以为亚微米尺寸。多晶硅电极的长度可以基本上大于多晶硅电极的宽度,以使得多晶硅电极具有高的纵横比。

根据本公开的另一实施例,设置了一种气体传感器阵列组件,其包括如上所述的多个气体感测装置的阵列,其中,多个气体感测装置可以形成在同一芯片上。与气体感测装置组合来公开的特征和实施例也能够结合气体传感器阵列组件来实施,反之亦然。

感测装置可以具有相同的气体感测材料或不同的气体感测材料,并且可以在不同温度的驱动条件下操作。这允许气体传感器阵列组件选择性地对不同的气体感测,或者提供二重或差分输出。

根据本公开内容的另一方面,提供了一种制造气体感测装置的方法,该方法包括:形成衬底;形成设置在衬底上的电介质层;在电介质层内形成加热器;在衬底内形成蚀刻腔体部分;形成用于感测气体的材料;以及形成与用于感测气体的材料耦合的一个或更多个多晶硅电极。

结合气体感测装置公开的特征和实施例也能够结合该方法来实施,反之亦然。

形成一个或更多个多晶硅电极可以包括:在CMOS兼容工艺中形成场阻氧化(或栅极氧化)层;在该场阻氧化层上或上方形成一个或更多个多晶硅电极;以及蚀刻该场阻氧化层。

形成一个或多个多晶硅电极可以包括:在CMOS兼容工艺中形成包括第一对电极的第一多晶硅层;以及在CMOS兼容工艺中形成包括第二对电极的第二多晶硅层。

与现有技术的气体传感器相比,所公开的感测装置具有提供CMOS兼容性的多晶硅电极,并且可以具有以下特征:

i)使用附加对电极对MOX层进行四路测量,该附加对电极可以由多晶硅或诸如钨的另一材料制成;

ii)限制MOX层的凹部;

iii)至少一个蚀刻停止层,其用于控制凹槽的形状和位置,并且优选地将MOX与加热器进行物理地和电气地分隔;以及

iv)将MOX部分地或全部地嵌入在膜内形成的凹槽中。

与现有技术的感测装置相比,所公开的气体感测装置可以具有以下优点:

i)使用多晶硅电极,以使得除了膜蚀刻和封装之外不需要后CMOS处理;

ii)多晶硅电极能够在亚微米尺度上以高纵横比制造,因此增加了装置的灵敏度;

iii)将MOX层限制在凹部内,以减少MOX层在膜的表面上的扩展;

iv)使用至少一个蚀刻停止层,以可再现的方式限定凹槽,并且可能避免金属氧化物(MOX)与加热器层物理或电接触。这种蚀刻停止层可以是形成在大量制造的二氧化硅膜内的氮化硅层。这种氮化层也可以用作膜内的应力消除层;

v)由于MOX层扩展的减少而提高的可靠性和可再现性,以及减少的热损失和功率;

vi)较小的形状因子,因为该限制将MOX层的斑点尺寸最小化,并因此使膜尺寸最小化;

vii)优选地降低封装成本,因为ASIC将经由焊球或TSV进行键合,并且不需要键合线。封装可能也可以在晶圆级完成。

在下文中,以编号方式给出了气体感测装置、气体传感器阵列组件和制造气体感测装置的方法的多个方面。

方面1.一种气体感测装置,包括:

衬底,其包括蚀刻腔体部分和衬底部分;

电介质层,其设置在衬底上,其中,该电介质层包括电介质膜,其中,该电介质膜与衬底的蚀刻腔体部分相邻;

加热器,其位于电介质层内;

用于感测气体的材料;以及

一个或多个多晶硅电极,其与该用于感测气体的材料耦合。

方面2.根据方面1所述的气体感测装置,其中,多晶硅电极配置为测量该用于感测气体的材料的电阻。

方面3.根据方面1所述的气体感测装置,其中,多晶硅电极是高掺杂的。

方面4.根据方面1所述的气体感测装置,其中,多晶硅电极包括多个叉指状结构。

方面5.根据方面4所述的气体感测装置,其中,叉指状结构中的至少一些的宽度和/或多个叉指状结构内的相邻叉指状结构之间的距离具有亚微米尺寸。

方面6.根据方面1所述的气体感测装置,其中,多晶硅电极在CMOS兼容工艺中形成。

方面7.根据方面1所述的气体感测装置,其中,多晶硅电极中的至少一个与用于感测气体的材料直接接触。

方面8.根据方面1所述的气体感测装置,其中,该装置包括倒装芯片配置。

方面9.根据方面1所述的气体感测装置,其中,加热器包括CMOS材料,并且可选地,其中,CMOS材料是多晶硅、铂、钛、钨中的任一个或这些的组合。

方面10.根据方面1所述的气体感测装置,其中,加热器形成在多晶硅电极下面。

方面11.根据方面1所述的气体感测装置,

其中,电介质膜包括蚀刻凹部,以及

其中,用于感测气体的材料位于电介质膜的蚀刻凹部内。

方面12.根据方面1所述的气体感测装置,其中,多晶硅电极包括第一多晶硅层,并且其中,加热器包括第二多晶硅层。

方面13.根据方面1所述的气体感测装置,其中,多晶硅电极包括第一多晶硅层和第二多晶硅层。

方面14.根据方面1所述的气体感测装置,其中,多晶硅电极包括:

第一对电极,其包括叉指状电极,以及

第二对电极,其在所述第一对电极之间交错。

方面15.根据方面14所述的气体感测装置,其中,第一对电极配置为使得在其两端施加电流偏置,并且其中,第二对电极配置为测量第二对电极之间的电压。

方面16.一种气体传感器阵列组件,其包括根据方面1的多个气体感测装置的阵列,其中,所述多个装置形成在同一芯片上。

方面17.一种制造气体感测装置的方法,该方法包括:

形成衬底;

形成设置在衬底上的电介质层;

在电介质层内形成加热器;

在衬底内形成蚀刻腔体部分;

形成用于感测气体的材料;以及

形成与该用于感测气体的材料耦合的一个或更多个多晶硅电极。

方面18.根据方面17所述的制造气体感测装置的方法,其中形成一个或多个多晶硅电极包括:

在CMOS兼容工艺中形成场阻氧化层;

在该场阻氧化层上或上方形成一个或多个多晶硅电极;以及

蚀刻场阻氧化层。

方面19.根据方面17所述的制造气体感测装置的方法,其中,形成一个或更多个多晶硅电极包括:

在CMOS兼容工艺中形成包括第一对电极的第一多晶硅层;以及

在CMOS兼容工艺中形成包括第二对电极的第二多晶硅层。

附图说明

现在将仅通过举例的方式并参照附图来公开本公开的一些优选实施例,其中:

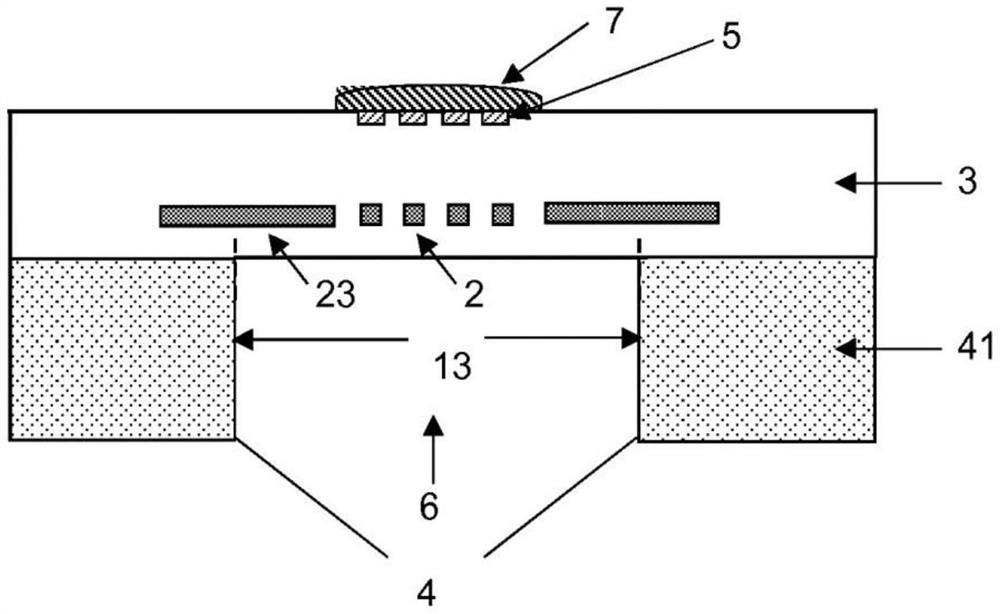

图1示出了根据现有技术的气体感测装置;

图2示出了根据一个实施例的基于微热板的气体传感器的示意性截面图;

图3示出了根据一个实施例的倒置的气体传感器的示意性截面图,其中,在电介质膜内形成凹槽;

图4示出了根据一个实施例的倒置的气体传感器的示意性截面图,其中,多晶硅电极在感测层内而非在感测层底部处;

图5示出了根据一个实施例的连接到诸如ASIC的另一芯片的倒置气体传感器倒装芯片的示意性截面图;

图6示出了根据一个实施例的连接到ASIC形式的另一芯片的倒置气体传感器倒装芯片的替代结构;

图7示出了连接到另一芯片的倒置气体传感器倒装芯片的阵列的示意性截面图;

图8示出了根据一个实施例的替代气体传感器的示意性截面图,其中膜凹槽存在于膜的顶侧而非底侧上;

图9示出了带有环形金属加热器的替代气体传感器的示意性截面图;

图10示出了根据一个实施例的多晶硅电极的顶视图;

图11示出了根据一个实施例的表示与金属氧化物形成欧姆接触的多晶硅电极的测量结果;

图12示出了概述气体传感器的制造方法的示例性流程图;以及图13A-C示出了根据一个实施例的气体传感器的示例性制造步骤,其中:

图13A示出了具有多晶硅电极、蚀刻停止层和嵌入在膜内的加热器的电介质膜;

图13B示出了图13A的装置,其随后已从背侧暴露于蚀刻剂以在电介质膜内形成凹槽;以及

图13C示出了图13B的装置,其随后已上下翻转,其中,感测材料被限制在蚀刻凹槽内。

图14示出了可以使用的另外的电极布置。

具体实施方式

在附图中给出器件的一些示例。

图2示出了示例性气体传感器1的截面。气体传感器1包括由具有蚀刻部分6和衬底部分4的半导体衬底41支撑的电介质层3。在一个示例中,半导体衬底41能够由硅或碳化硅制成。该电介质层3具有电介质膜区或区域13,该电介质膜区或区域定位为紧接或直接地邻近或靠近衬底41的蚀刻部分或腔体6。在一个示例中,电介质层3能够由诸如氧化硅、氮化硅或其组合物的材料制成。电介质膜区域13对应于电介质层3的(直接)在蚀刻部分6上方或下方的区域。通过DRIE蚀刻衬底41以形成蚀刻部分或腔体6。

气体感测材料7沉积或生长在电介质膜13上。气体感测材料7与形成在电介质层3内的一对叉指状多晶硅电极5电接触。多晶硅电极配置为测量气体感测材料7的电阻和/或电容。加热器2和加热器轨道23嵌入在电介质层3内,其在通电时升高气体感测MOX层7的温度。加热器2形成在电介质膜区域13内。在该实施例中,加热器2是微加热器,并且能够由金属(诸如钨、铂、金或钛)制成。

在一个示例中,气体感测材料7能够是金属氧化物,诸如氧化锡、氧化钨、氧化铝、氧化锌、氧化铜、这些金属氧化物的组合物或其他金属氧化物。在另外的示例中,气体感测材料7能够是未掺杂的或者掺杂有诸如铂(Pt)或钯(Pd)的元素。替代地,气体感测材料可以为聚合物或纳米材料,诸如碳纳米管或金属氧化物纳米线。

使用多晶硅作为电极允许使用CMOS兼容工艺来制造整个气体感测装置。多晶硅电极能够制造为亚微米尺寸,允许以较高的纵横比来将更大长度的电极封装到较小的区域中。多个多晶硅电极可以由第一多晶硅层形成,并且加热器可以由第二多晶硅层形成。

图3示出了一种替代的气体传感器,其中,传感器具有倒置的配置。电介质膜区13被图案化或蚀刻,使得在电介质膜区13中存在凹槽50,以在感测MOX材料7从电介质膜区13的一侧(例如从背侧)沉积时被定位或限制。在电介质膜区13内、多晶硅电极5下方形成蚀刻停止层8。除了待形成气体感测材料7的区域以外的区域处,在电介质膜区13的顶部上形成另一蚀刻停止层12。蚀刻停止层8、12可以是氮化硅或对用于蚀刻半导体衬底4和/或电介质膜13的蚀刻剂具有高电阻的任何其他材料。氮化硅层8、12用作蚀刻停止层,以允许在膜13中蚀刻凹槽50。氮化硅层8、12还提供应力消除并限定腔体6。气体感测材料7形成在蚀刻凹槽50内、电介质膜区13上。应当理解,蚀刻停止层8、12可以由氮化硅形成,或者可以由与膜的其余部分具有不同蚀刻选择性的其他材料形成。

气体感测材料7在电介质膜13的凹槽50中的衬底腔体6内沉积或生长。多晶硅电极5与气体感测材料7直接接触。加热器在多晶硅电极下方或下面形成。在制造工艺中,使用高温以用于沉积多晶硅电极。这种倒置传感器配置允许在不损坏下面的金属加热器的情况下通过使用高温形成多晶硅电极。这是因为在倒置配置中,多晶硅感测电极在金属加热器之前沉积,并且因此多晶硅的高沉积温度不会损坏加热器。由于在制造后装置被倒置,因此多晶硅电极就处于加热器上方。

气体传感器1以倒装芯片配置形成。气体传感器能够使用用于连接的焊球、焊点、铜柱或螺柱凸点9放置在电路(例如专用集成电路(ASIC)或印刷电路板(PCB))上方。焊球9通常放置在可焊垫10上,并且能够在CMOS工艺或后CMOS中以晶圆级或芯片级在IR装置和ASIC两者上形成。

图4示出了一种替代的气体传感器,其中,多晶硅电极5垂直定位在MOX感测层7内。换句话说,多晶硅电极5从MOX感测层7的每个侧壁的中间部分横向延伸。图4的气体传感器的许多特征与图3中的那些相同,并且因此具有相同的附图标记。在该实施例中,氮化硅层8在电介质层3中形成得比多晶硅电极5深。这允许蚀刻进一步继续到电介质膜区域13中,并且意味着部分MOX气体感测材料7在多晶硅电极5下方。这允许气体感测材料7与感测电极5之间的更多的接触。在该实施例中,氮化硅层12延伸跨过电介质3或气体传感器1的整个宽度。氮化硅层8、12有助于消除器件内的应力。

图5示出了一种替代气体传感器,其中,气体传感器通过倒装芯片附接到第二芯片,诸如ASIC。图5的气体传感器的许多特征与图4中那些的相同,并且因此具有相同的附图标记。在该实施例中,气体传感器1通过焊球9和可焊垫10附接到ASIC芯片11。该芯片具有驱动、读取、转换和处理电路。该芯片可以包含模拟、数字、或混合信号模拟和数字电路。该芯片还可以包括湿度和/或温度和/或压力传感器。该芯片可以包括内存块和状态机。

在该实施例中,气体感测MOX材料7的主要部分在多晶硅电极5的下面或下方,这意味着多晶硅电极5更靠近MOX材料7的表面。与较厚的MOX层相比,薄的气体感测MOX层具有增加的灵敏度。在无腔体的平坦表面上使用常规的喷射或滴涂技术,导致了MOX层7的相对厚和不可控的尺寸。在这种气体传感器中,MOX部分或全部地嵌入在膜内的效果具有MOX层的等效的较薄层(其多晶硅电极更靠近暴露于气体的MOX表面)和更受控的尺寸的优点。

图6示出了一种替代气体传感器,其中,气体感测材料仅形成在多晶硅电极之间的间隔中,并且不在多晶硅电极之下。图6气体传感器的许多特征与图5中所示的那些相同,并且因此具有相同的附图标记。

图7示出了根据一个实施例的倒装芯片配置中的气体传感器的阵列。图7的许多特征与图6所示那些的相同,并且因此具有相同的附图标记。其能够有任意数量的传感器1、21,每个传感器都具有相同的MOX气体感测7、27材料或者不同的MOX气体感测材料,并且可以在不同温度和不同驱动条件下操作。气体传感器形成在同一电介质层3内,在分隔的电介质膜13、33上。膜13、33在阵列内也能够具有不同的尺寸。

图8示出了一种具有非倒装芯片配置的替代气体传感器。图8的许多特征与图5中所示的那些相同,并且因此具有相同的附图标记。在该实施例中,电介质膜区13的前侧被蚀刻以在电介质膜中形成凹槽50。气体感测MOX材料7形成为部分或全部地嵌入电介质膜中。气体传感器能够使用接线接合或硅通孔(未示出)连接到ASIC。

图9示出了一种替代气体传感器,其中,电极5具有环形结构。该实施例不是以倒装芯片配置形成,并且因此能够以常规方式封装。在这种配置中,在金属加热器之前沉积多晶硅。因此,在多晶硅沉积期间所需的高温不会影响金属加热器。

图10示出了根据一个实施例的多晶硅电极的顶视图。第一对叉指状多晶硅电极120、121配置为使得在它们两端施加电流偏置,并且第二对交错电极122、123配置为测量电压。第一对电极120、121具有叉指状(指状物)结构。第二对电极122、123在第一对电极120、121的指状物之间交错。叉指状或交错电极结构中的每个的宽度和/或相邻电极结构之间的距离优选地具有亚微米尺寸。用于多晶硅的图案化技术允许叉指状电极结构的这种分辨率,意味着电极能够被封装或容纳进小区域内。

CMOS技术提供多晶硅宽度(其通常限定了CMOS晶体管的MOS栅极的长度)作为制造工艺中的最小可控尺寸。因此,能够形成具有亚微米宽度的多晶硅电极。电极对的相邻指状物之间的距离也可以为亚微米。这种高纵横比导致电极的密集得多的结构,这进一步降低了气体感测层的电阻。这在MOX层的电阻非常高(MΩ范围)的情况下是特别有用的并且高纵横比允许它们被降低到1MΩ以下。

这种四线测量配置允许在消除了接触电阻的影响的同时,测量气体感测材料7的电阻。这导致气体感测装置的灵敏度提高。这也降低了感测电阻,因此使测量电路不太复杂。

图11示出了当使用单对多晶硅叉指状电极时,金属氧化物的测量的电流-电压(I-V)特性。测量结果示出多晶硅与MOX之间的欧姆接触。

图12示出了概述气体传感器的制造方法的示例性流程图。下面描述通常所执行的步骤。应当理解,以下步骤可以是顺序的或非顺序的:

步骤1(S1):从衬底开始。

步骤2(S2):沉积具有嵌入式加热器和多晶硅电极的电介质层。也可以形成蚀刻停止层。

步骤3(S3):蚀刻衬底以形成腔体。

步骤4(S4):在凹槽内沉积金属氧化物感测层。

在膜具有蚀刻凹槽的实施例中,该方法还可以包括蚀刻电介质层的步骤。因为蚀刻剂不会蚀刻停止层或电极,所以这可以使用蚀刻停止层来完成。这可以通过使用用于腔体蚀刻的深反应离子蚀刻、然后通过用于凹槽的湿法氧化物蚀刻,在步骤2的单个步骤中执行。

图13A-C示出了根据本公开一个实施例的形成凹槽并暴露感测电极的一些示例步骤。

图13A示出了电介质膜13,其中,多晶硅电极5和加热器2嵌入在膜13内。层8和12由蚀刻性能与电介质层3的蚀刻性能不同的材料制成。

图13B示出了图13A的装置,其随后已从背侧暴露于对膜的蚀刻速率高而对层8和12的蚀刻速率低的蚀刻剂。其对蚀刻停止层8、12下方的电介质层蚀刻以形成凹槽。

图13C示出了图13B的装置,其然后被上下翻转。沉积传感材料7以使得其被限制在凹槽内。

图14的部分(a)表示了具有四个矩形平行电极的电极配置。在这种布置中,电流偏置被施加到两个最外部电极,并且在两个内部电极上测量电压。

图14的部分(b)和图14的部分(c)表示了可以使用的电极的其他布置。

上述说明书中所使用的参考标记的说明如下:

1 气体传感器

2 嵌入在电介质膜中的嵌入微加热器

23 加热器轨道

3 电介质层

13 电介质膜区域

4 半导体衬底

41 衬底部分

5 多晶硅叉指状电极

6 衬底内的腔体

7 金属氧化物感测层

8 氮化硅层(多晶硅电极下方)

9 焊球、焊点、铜柱或螺柱凸点

10 可焊垫

11 ASIC

12 氮化硅层(电介质膜的表面上)

50 电介质膜内的凹槽

21 气体传感器

22 嵌入在电介质膜中的嵌入式微加热器

24 半导体衬底

25 多晶硅叉指状电极

26 衬底内的腔体

27 金属氧化物感测层

28 氮化硅层(多晶硅电极下方)

32 氮化硅层(电介质膜的表面上)

120 叉指状多晶硅电极120

121 叉指状多晶硅电极

122 交错电极

123 交错电极

技术人员将理解,在前面的说明书和所附权利要求书中,诸如“上方”、“交叠”、“以下”、“横向”、“垂直”等位置术语是参考感测装置的概念性表示做出的,诸如示出标准横截面透视图的那些和在附图中示出的那些。使用这些术语是便于参考,而并非旨在限制。因此,这些术语被理解为是指在如附图所示的定向上的感测装置。

尽管在如以上所阐述的优选实施例方面来描述了本发明,但应当理解,这些实施例仅是说明性的,并且权利要求不限于那些实施例。本领域技术人员将能够根据根据本公开内容作出落在所附权利要求范围内的修改和替代。在本说明书中所公开或示出的每个特征可以单独地或以与本文所公开或所示出的任何其他特征适当的任何适当组合的形式合并在本发明中。

本申请要求US 16/186,843的优先权。该申请的公开内容都全部并入在本文中。

- 气体传感器用接触构件、气体传感器、限制构件、气体传感器的传感器元件和接触构件的连接方法、以及气体传感器的制造方法

- 气体传感器用加热线圈、气体传感器用检测元件、接触燃烧式气体传感器及接触燃烧式气体传感器的制造方法