一种参考时钟信号注入锁相环电路及消除失调方法

文献发布时间:2023-06-19 11:27:38

技术领域

本发明涉及电子电路的技术领域,特别是涉及一种参考时钟信号注入锁相环电路及消除失调方法。

背景技术

如图1所示,现有技术中参考时钟信号注入锁相环电路包括脉冲生成器(SlotGen)、鉴相器(Phase Detector)、滤波器(Filter)、压控振荡器(Voltage ControlledOscillator,VCO)和锁频环(Frequency Lock Loop,FLL)。其中,由于参考注入锁相环是在不断开环形振荡器的情况下,直接注入参考时钟信号,参考脉冲PUL_REFP与注入参考脉冲之前的压控振荡器的输出信号之间存在相位差tos,会导致参考脉冲PUL_REFP注入后的压控信号VCO_NEW的时钟杂散非常大。

图2示出了现有技术中的参考时钟信号注入相位误差引起时钟杂散的时序示意图。对于锁定后的参考时钟信号注入锁相环:

其中N为压控振荡器VCO信号的平均频率与参考时钟信号的时钟频率之比,T

可以推导得出,

因此,压控振荡器VCO信号的周期序列可得:

对上述因相位差t

因此,需要提供一种能够参考时钟信号注入锁相环电路及消除失调方法。

发明内容

鉴于以上所述现有技术的缺点,本发明的目的在于提供一种参考时钟信号注入锁相环电路及消除失调方法,将参考时钟信号注入通路和锁相环鉴相通路合并成一个通路,并预先将鉴相器的失调清零,解决了参考时钟信号注入环路的相位失配问题。

为实现上述目的及其他相关目的,本发明提供一种参考时钟信号注入锁相环电路,包括第一脉冲生成器、第二脉冲生成器、状态机、脉冲选择放大电路、压控延迟线、零失配鉴相器和滤波器,用于组成一个失调消除环路、一个锁相环路、一个压控振荡环路和一个注入锁相环路;所述失调消除环路包括所述所述第一脉冲生成器、所述状态机、所述零失配鉴相器和所述脉冲选择放大电路;所述压控振荡环路包括所述第二脉冲生成器、所述脉冲选择放大电路和所述压控延迟线;所述锁相环路包括所述第一脉冲生成器、所述第二脉冲生成器、所述零失配鉴相器、所述滤波器、所述压控延迟线所述脉冲选择放大电路;所述注入锁相环路包括所述脉冲选择放大电路、所述第一脉冲生成器、所述第二脉冲生成器、所述状态机、所述零失配鉴相器、所述滤波器和所述压控延迟线;所述状态机断开所述锁相环路和所述压控振荡环路,启用所述失调消除环路以采用所述第一脉冲生成器生成的第一脉冲信号来校正所述零失配鉴相器;所述状态机启用所述锁相环路和所述压控振荡环路,用校正后的所述零失配鉴相器来锁定所述第二脉冲生成器生成的第二脉冲信号;所述状态机将所述锁相环路切换到所述注入锁相环路,启用所述注入锁相环路,用于注入所述第一脉冲生成器生成的第一脉冲信号。

于本发明一实施例中,所述失调消除环路采用所述第一脉冲生成器生成的第一脉冲信号来校正所述零失配鉴相器时,所述脉冲选择放大电路用于在所述状态机的控制下,将参考时钟信号分为两路输入所述零失配鉴相器。

于本发明一实施例中,用校正后的所述零失配鉴相器来锁定所述第二脉冲生成器生成的第二脉冲信号时,所述脉冲选择放大电路用于在所述状态机的控制下,将所述压控延迟线输出的压控信号输入至所述压控延迟线和所述零失配鉴相器,将参考时钟信号输入所述零失配鉴相器;所述滤波器用于根据所述零失配鉴相器的输出值调节所述压控延迟线输出的压控信号频率;所述状态机用于当所述零失配鉴相器输出的相差均值为零时进行锁频。

于本发明一实施例中,注入所述第一脉冲生成器的信号时,所述脉冲选择放大电路用于当所述状态机检测到参考时钟信号时,选取所述参考时钟信号输入所述压控延迟线,所述压控延迟线输出的压控信号和所述参考时钟信号输入所述零失配鉴相器。

于本发明一实施例中,所述脉冲选择放大电路包括第一脉冲选择放大电路和第二脉冲选择放大电路;

参考时钟信号和所述压控延迟线输出的压控信号均输入至所述第一脉冲选择放大电路和所述第二脉冲选择放大电路,所述第一脉冲选择放大电路用于输出所述压控信号或所述参考时钟信号至所述压控延迟线和所述零失配鉴相器;所述第二脉冲选择放大电路用于输出所述压控信号或所述参考时钟信号至所述零失配鉴相器;

所述状态机用于通过发送选择信号至所述第一脉冲选择放大电路和所述第二脉冲选择放大电路来实现所述参考时钟信号和所述压控信号的输出选择。

于本发明一实施例中,所述压控振荡环路包括环形连接的所述第二脉冲生成器、所述第二脉冲选择放大电路和所述压控延迟线。

于本发明一实施例中,所述第二脉冲生成器用于将所述压控延迟线输出的压控信号转换为窄脉冲信号,所述脉冲选择放大电路用于在状态机的控制下将选取所述窄脉冲信号,并脉宽放大转换为宽脉冲信号。

于本发明一实施例中,所述第一脉冲生成器用于将参考时钟信号转换为窄脉冲信号,所述脉冲选择放大电路用于用于在状态机的控制下将选取所述窄脉冲信号,并脉宽放大转换为宽脉冲信号。

于本发明一实施例中,所述零失配鉴相器包括第一数字时间转换器、第二数字时间转换器和相位检测器/时间数字转换器;所述第一数字时间转换器和所述第二数字时间转换器均与所述相位检测器/时间数字转换器相连。

于本发明一实施例中,所述状态机有锁频功能,通过所述参考时钟信号来计算所述压控延迟线输出的压控信号的频率误差,并输出所述频率误差至所述滤波器。

于本发明一实施例中,切换到所述注入锁相环路时,所述状态机还用于调节所述零失配鉴相器的失调-符号控制端使得所述零失配鉴相器输出的鉴相结果信号反相。

于本发明一实施例中,所述滤波器根据所述零失配鉴相器的鉴相结果信号的均值和频率误差的均值通过所述滤波器施加的电压调节所述压控延迟线输出的压控信号的相位和频率,直至所述所述鉴相结果信号的均值为零并且所述频率误差的均值也为0时,所述压控信号的频率和相位被锁定,即所述锁相环路和所述压控振荡环路被锁定。

本发明提供一种参考时钟信号注入锁相环的消除失调方法,应用于参考时钟信号注入锁相环电路,所述参考时钟信号注入锁相环电路包括第一脉冲生成器、第二脉冲生成器、状态机、脉冲选择放大电路、压控延迟线、零失配鉴相器和滤波器,用于组成一个失调消除环路、一个锁相环路、一个压控振荡环路和一个注入锁相环路;所述失调消除环路包括所述所述第一脉冲生成器、所述状态机、所述零失配鉴相器和所述脉冲选择放大电路;所述压控振荡环路包括所述第二脉冲生成器、所述脉冲选择放大电路和所述压控延迟线;所述锁相环路包括所述第一脉冲生成器、所述第二脉冲生成器、所述零失配鉴相器、所述滤波器、所述压控延迟线所述脉冲选择放大电路;所述注入锁相环路包括所述脉冲选择放大电路、所述第一脉冲生成器、所述第二脉冲生成器、所述状态机、所述零失配鉴相器、所述滤波器和所述压控延迟线;

所述参考时钟信号注入锁相环的消除失调方法包括以下步骤:

通过状态机断开所述锁相环路和所述压控振荡环路,启用所述失调消除环路以采用所述第一脉冲生成器生成的第一脉冲信号来校正所述零失配鉴相器;

通过状态机启用所述锁相环路和所述压控振荡环路,用校正后的所述零失配鉴相器来锁定所述第二脉冲生成器生成的第二脉冲信号;

通过状态机将所述锁相环路切换到所述注入锁相环路,启用所述注入锁相环路,用于注入所述第一脉冲生成器生成的第一脉冲信号。

于本发明一实施例中,所述失调消除环路采用所述第一脉冲生成器生成的第一脉冲信号来校正所述零失配鉴相器时,所述脉冲选择放大电路在所述状态机的控制下,将参考时钟信号分为两路输入所述零失配鉴相器。

于本发明一实施例中,用校正后的所述零失配鉴相器来锁定所述第二脉冲生成器生成的第二脉冲信号时,所述脉冲选择放大电路在所述状态机的控制下,将所述压控延迟线输出的压控信号输入至所述压控延迟线和所述零失配鉴相器,将参考时钟信号输入所述零失配鉴相器;所述滤波器根据所述零失配鉴相器的输出值调节所述压控延迟线输出的压控信号频率;所述状态机当所述零失配鉴相器输出的相差均值为零时进行锁频。

于本发明一实施例中,注入所述第一脉冲生成器的信号时,当所述状态机检测到参考时钟信号时,所述脉冲选择放大电路选取所述参考时钟信号输入所述压控延迟线,所述压控延迟线输出的压控信号和所述参考时钟信号输入所述零失配鉴相器。

于本发明一实施例中,所述脉冲选择放大电路包括第一脉冲选择放大电路和第二脉冲选择放大电路;

参考时钟信号和所述压控延迟线输出的压控信号均输入至所述第一脉冲选择放大电路和所述第二脉冲选择放大电路,所述第一脉冲选择放大电路输出所述压控信号或所述参考时钟信号至所述压控延迟线和所述零失配鉴相器;所述第二脉冲选择放大电路输出所述压控信号或所述参考时钟信号至所述零失配鉴相器;

所述状态机通过发送选择信号至所述第一脉冲选择放大电路和所述第二脉冲选择放大电路来实现所述参考时钟信号和所述压控信号的输出选择。

于本发明一实施例中,所述压控振荡环路包括环形连接的所述第二脉冲生成器、所述第二脉冲选择放大电路和所述压控延迟线。

于本发明一实施例中,所述第二脉冲生成器用于将所述压控延迟线输出的压控信号转换为窄脉冲信号,所述脉冲选择放大电路用于在状态机的控制下将选取所述窄脉冲信号,并脉宽放大转换为宽脉冲信号。

于本发明一实施例中,所述第一脉冲生成器用于将参考时钟信号转换为窄脉冲信号,所述脉冲选择放大电路用于用于在状态机的控制下将选取所述窄脉冲信号,并脉宽放大转换为宽脉冲信号。

于本发明一实施例中,所述零失配鉴相器包括第一数字时间转换器、第二数字时间转换器和相位检测器/时间数字转换器;所述第一数字时间转换器和所述第二数字时间转换器均与所述相位检测器/时间数字转换器相连。

于本发明一实施例中,所述状态机有锁频功能,通过所述参考时钟信号来计算所述压控延迟线输出的压控信号的频率误差,并输出所述频率误差至所述滤波器。

于本发明一实施例中,切换到所述注入锁相环路时,所述状态机调节所述零失配鉴相器的失调-符号控制端使得所述零失配鉴相器输出的鉴相结果信号反相。

于本发明一实施例中,所述滤波器根据所述零失配鉴相器的鉴相结果信号的均值和频率误差的均值通过所述滤波器施加的电压调节所述压控延迟线输出的压控信号的相位和频率,直至所述所述鉴相结果信号的均值为零并且所述频率误差的均值也为0时,所述压控信号的频率和相位被锁定,即所述锁相环路和所述压控振荡环路被锁定。

如上所述,本发明的参考时钟信号注入锁相环电路及消除失调方法,具有以下有益效果:

(1)将参考时钟信号注入通路和锁相环鉴相通路合并成一个通路,并预先将鉴相器的失调清零,解决了参考时钟信号注入环路的相位失配问题;

(2)消除了锁相环输出的时钟杂散;

(3)可应用于一般时钟生成器、倍频器、锁相环、时钟数据恢复(Clock DataRecovery,CDR)等电子电路或系统中。

附图说明

图1显示为现有技术中参考时钟信号注入锁相环电路于一实施例中的框架结构示意图;

图2显示为现有技术中的参考时钟信号注入相位误差引起时钟杂散的时序示意图;

图3显示为本发明的参考时钟信号注入锁相环电路于一实施例中的框架结构示意图;

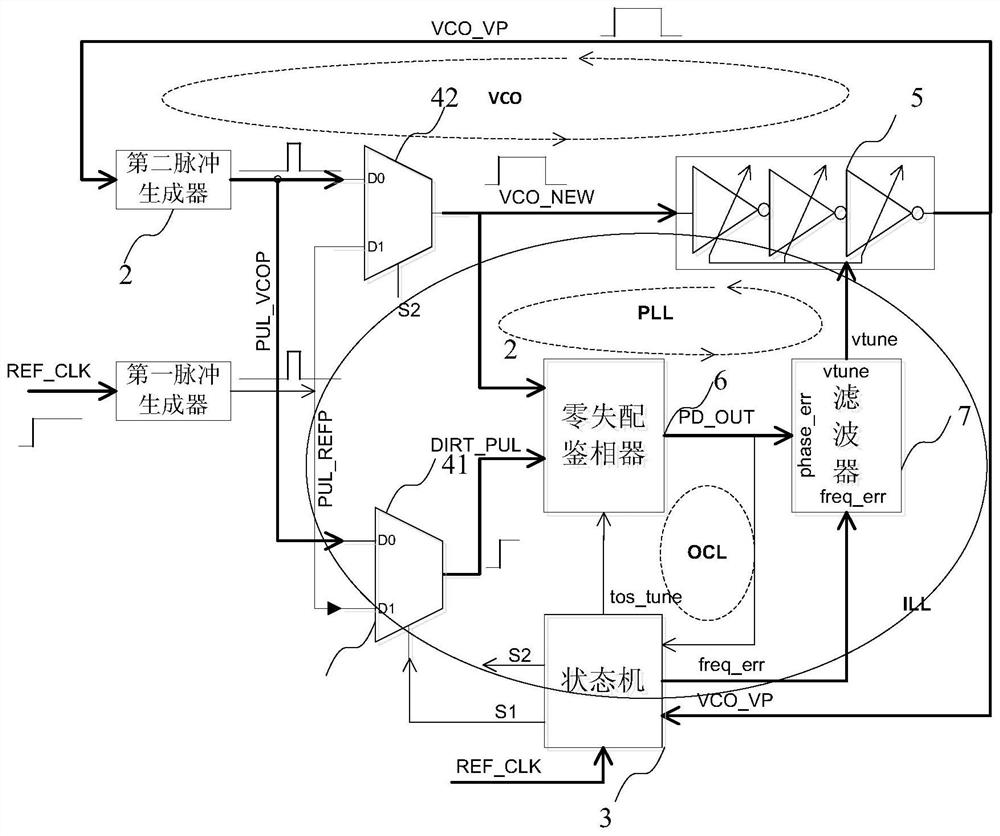

图4显示为本发明的参考时钟信号注入锁相环电路于一实施例中的电路结构示意图;

图5显示为图4的参考时钟信号注入锁相环电路工作在失调消除环路的模式下的等效电路图;

图6显示为图4的参考时钟信号注入锁相环电路工作锁相环(含锁频锁相)模式下的等效电路图;

图7显示为图4的参考时钟信号注入锁相环电路在注入状态下的等效电路图;

图8显示为本发明的参考时钟信号注入锁相环电路在参考时钟信号注入时的信号时序图;

图9显示为本发明的零失配鉴相器于一实施例中的结构示意图;

图10显示为本发明的参考时钟信号注入锁相环的消除失调方法于一实施例中的流程图。

元件标号说明

1 第一脉冲生成器

2 第二脉冲生成器

3 状态机

4 脉冲选择放大电路

41 第一脉冲选择放大电路

42 第二脉冲选择放大电路

5 压控延迟线

6 零失配鉴相器

61 第一数字时间转换器

62 第二数字时间转换器

63 相位检测器/时间数字转换器

7 滤波器

具体实施方式

以下由特定的具体实施例说明本发明的实施方式,熟悉此技术的人士可由本说明书所揭露的内容轻易地了解本发明的其他优点及功效。

须知,本说明书所附图式所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“下”、“左”、“右”、“中间”及“一”等的用语,亦仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

本发明的参考时钟信号注入锁相环电路及消除失调方法中,将参考时钟信号注入通过的环路路径与相位误差检测的环路路径重合,即将参考时钟信号注入的相位误差就等效成鉴相器的失调,并预先将鉴相器的失调清零,使得参考时钟信号注入相位误差,也即环路锁定后鉴相误差)为零,从而消除锁相环输出的时钟杂散,解决了参考时钟信号注入引发的相位失配的问题。

如图3和图4所示,于一实施例中,本发明的参考时钟信号注入锁相环电路包括第一脉冲生成器1、第二脉冲生成器2、状态机(State Machine)3、脉冲选择放大电路((PulseWidth Select and Amplitude Circuit,PWSAC)4、压控延迟线(Voltage ControlledDelay Lines,VCDL)5、零失配鉴相器(Zero Offset Phase Detector,ZOPD)6和滤波器(Filter)7。所述脉冲选择放大电路4连接至所述第一脉冲生成器1和所述第二脉冲生成器2的输出端均连接至的输入端,所述状态机3与所述脉冲选择放大电路4、所述零失配鉴相器6、所述滤波器7均相连,所述脉冲选择放大电路4的输出与所述压控延迟线5和所述零失配鉴相器6分别相连,所述零失配鉴相器6再与所述状态机3和所述滤波器7分别相连,所述滤波器7与所述状态机3与所述压控延迟线5分别相连,所述压控延迟线5再与所述第二脉冲生成器2相连。

优选地,所述第一脉冲生成器1和第二脉冲生成器2为窄脉冲生成器,所述第一脉冲生成器1用于接收参考时钟信号REF_CLK并生成第一窄脉冲信号PUL_REFP,所述第二脉冲生成器2用于接收压控延迟线输出信号VCO_VP并生成第二窄脉冲信号PUL_VCOP。所述脉冲选择放大电路4用于在状态机的控制下选取窄脉冲信号并将其脉宽放大转换成宽脉冲信号,其包括第一脉冲选择放大电路41和第二脉冲选择放大电路42,所述第一脉冲选择放大电路41和第二脉冲选择放大电路42分别用于选择所述第一脉冲生成器1和第二脉冲生成器2输出的第一窄脉冲信号PUL_REFP和第二窄脉冲信号PUL_VCOP中的一个作为输入并将其分别转换成第一宽脉冲信号DIRT_PUL和第二宽脉冲信号VCO_NEW输出。所述零失配鉴相器6对所述第一脉冲选择放大电路41和第二脉冲选择放大电路42输出的第一宽脉冲信号DIRT_PUL和第二宽脉冲信号VCO_NEW进行鉴相并输出鉴相结果信号PD_OUT。所述压控延迟线5连接至所述第一脉冲选择放大电路42的输出端,用于接收所述第二宽脉冲信号VCO_NEW并由所述滤波器7控制其延迟时间(即,控制VCO_VP的频率)。所述状态机3连接至所述脉冲选择放大电路4的控制端,以控制所述脉冲选择放大电路4的信号选取。例如,当状态机的输出的S1和S2为高电平时选通所述脉冲选择放大电路4相应的D1端口;当S1和S2为低电平时选通所述脉冲选择放大电路4相应的D0端口。

其中,本发明的参考时钟信号注入锁相环电路共包含有以下四个环路:

(1)一个失调消除环路(Offset Calibration Loop,OCL)

所述失调消除环路包括所述第一脉冲生成器1、所述状态机3、所述零失配鉴相器6和所述脉冲选择放大电路4。

(2)一个压控振荡环路(Voltage Controlled Oscillator Loop,VCO)

所述压控振荡环路包括所述第二脉冲生成器2、所述脉冲选择放大电路4和所述压控延迟线5。

(3)一个锁相环路(Phase Lock LOOP,PLL)

所述锁相环路包括第一脉冲生成器1、第二脉冲生成器2、所述零失配鉴相器6、所述滤波器7、所述压控延迟线5和所述脉冲选择放大电路4。

(4)一个注入锁相环路(Inject Lock Loop,ILL)

所述注入锁相环路包括所述第一脉冲生成器1、所述第二脉冲生成器2、所述状态机3、所述脉冲选择放大电路4、所述压控延迟线5、所述零失配鉴相器6和所述滤波器7。

为了消除参考时钟信号注入带来的时钟杂散,需要消除注入的参考时钟信号相位和对应的压控振荡器VCO信号之间的相位差。本发明的参考时钟信号注入锁相环电路的工作原理如下:

首先,如图5所示,所述状态机3将锁相环切换到所述注入锁相环路和所述压控振荡环路,启用所述失调消除环路以采用所述第一脉冲生成器1生成的第一脉冲信号来校正所述零失配鉴相器6。具体地,所述状态机3将锁相环切换到所述注入锁相环路和所述压控振荡环路,并设置选择信号S1和S2的值,以控制所述第一脉冲选择放大电路41和第二脉冲选择放大电路42均选择第一窄脉冲信号PUL_REFP作为输入并将其脉宽放大输出至鉴相器零失配鉴相器6的第一和第二输入端。所述状态机3根据零失配鉴相器6的鉴相结果信号对所述零失配鉴相器6进行调节,以对零失配鉴相器6的失调进行校正。具体地,所述状态机3通过增大或减小输入至所述零失配鉴相器6的失调-符号控制端tos_tune的值来调节所述零失配鉴相器6的控制位直至其输出的鉴相结果信号PD_OUT均值为零,从而实现了所述零失配鉴相器6的零相位失调。其中,所述失调-符号控制端tos_tune具有双重功能:第一个功能是状态机通过其校正鉴相器内部的失调;第二个功能是状态机通过其根据流程改变鉴相器输出信号PD_OUT的极性。

如图6所示,所述状态机3启用所述锁相环路和所述压控振荡环路,用校正后的所述零失配鉴相器来锁定所述第二脉冲生成器生成的第二脉冲信号PUL_VCOP的相位。具体而言,所述状态机3设置选择信号S1和S2的值,以控制所述第一脉冲选择放大电路41和第二脉冲选择放大电路42分别选择第一窄脉冲信号PUL_REFP和第二窄脉冲信号PUL_VCOP作为输入并转换成相应的第一宽脉冲信号DIRT_PUL和第二宽脉冲信号VCO_NEW输出至鉴相器零失配鉴相器6的第一和第二输入端。所述零失配鉴相器6将鉴相结果信号PD_OUT输入至所述滤波器7的相位误差控制端phase_err,作为所述滤波器7的相位误差phase_err。同时所述数字状态机3有锁频功能,即用所述参考时钟信号REF_CLK来计算所述压控延迟线输出信号VCO_VP的频率误差,输出频率误差freq_err至所述滤波器7的频率误差控制端freq_err。所述滤波器7根据所述鉴相结果信号PD_OUT的均值和频率误差freq_err的均值通过滤波器施加的电压Vtune调节所述压控延迟线5输出的所述压控延迟线输出信号VCO_VP的相位和频率,直至相差PD_OUT均值为零并且所述频率误差freq_err均值也为0时,所述压控延迟线输出信号VCO_VP的频率和相位被锁定,即所述锁相环路和所述压控振荡环路被锁定。

最后,如图7所示,所述状态机3将所述锁相环路切换成注入锁相环路,以完成所述第一脉冲生成器1生成的第一脉冲信号PUL_REFP的周期性注入。具体地,当所述状态机3检测到锁相环路相位被锁定时(即,鉴相结果信PD_OUT的均值和频率误差freq_err的均值都等于0)时,所述状态机3将所述锁相环路切换成注入锁相环路。所述状态机3设置选择信号S1和S2的值,以控制所述第一脉冲选择放大电路41和第二脉冲选择放大电路42分别选择第二窄脉冲信号PUL_VCOP和第一窄脉冲信号PUL_REFP作为输入并转换成相应的第一宽脉冲信号DIRT_PUL和第二宽脉冲信号VCO_NEW输出至鉴相器零失配鉴相器6的第一和第二输入端,从而实现所述注入锁相环路的参考时钟信号的相位周期性注入。这相当于将以上所述的锁频锁相操作中所述第一窄脉冲信号PUL_REFP和所述第二窄脉冲信号PUL_VCOP进行了交换,使得第二脉冲选择放大电路42输出的当前第二宽脉冲信号VCO_NEW的沿降变成了以上锁频锁相操作中的第一宽脉冲信号DIRT_PUL信号,使得第一脉冲选择放大电路41输出的当前第一宽脉冲信号DIRT_PUL的沿降变成了锁频锁相操作中的第二宽脉冲信号VCO_NEW。而在锁频锁相操作中所述锁相环路和所述压控振荡环路被锁定时,第一宽脉冲信号DIRT_PUL与第二宽脉冲信号VCO_NEW上升沿是对齐的,那么在所述参考时钟信号注入时,所述参考时钟信号REF_CLK和所述压控延迟线输出信号VCO_VP对应的所述当前第二宽脉冲信号VCO_NEW与当前第一宽脉冲信号DIRT_PUL的上升沿也是对齐的,从而有效消除了时钟杂散。

值得注意的是,将锁频锁相操作中的第一窄脉冲信号PUL_REFP和第二窄脉冲信号PUL_VCOP进行了交换也意味着输入至零失配鉴相器6的第一端和第二端信号进行了交换(相应地,相位也交换)。因此,在切换成注入锁相环路时,状态机应调节其失调符号控制端tos_tune的值,使得所述零失配鉴相器6输出的鉴相结果信号PD_OUT反相,以维持锁相环路稳定的负反馈。

具体地,参考时钟信号注入的信号时序图如图8所示,在所述参考时钟信号REF_CLK注入之前,所述锁相环路的频率和相位均已锁定。在第一选择信号S1为高电平期间,交换所述第一脉冲信号PUL_REFP和所述第二脉冲信号PUL_VCOP。交换之后,VCO_NEW信号的沿降变成所述DIRT_PUL信号。所述DIRT_PUL信号与所述VCO_NEW信号进入所述零失调鉴相器6。由于环路锁定时所述DIRT_PUL信号与所述VCO_NEW信号的上升沿对齐,故不存在相位差tos的影响,从而消除了锁相环输出的时钟杂散。

值得注意的是,由于可能存在有较大的温漂,或者某些外部因素对锁相环的冲激影响(例如,电压的波动),使相位误差偏离了参考时钟信号注入锁相环的工作范围,则状态机需要根据实际情况在锁频锁相操作和参考时钟信号的注入操作之间来回切换。而且每次切换时,鉴相器输出信号PD_OUT的极性也要相应的改变,以维持锁相环路的负反馈特性。

如图9所示,于本发明一实施例中,所述零失配鉴相器6包括第一数字时间转换器61、第二数字时间转换器62和相位检测器/时间数字转换器63;所述第一数字时间转换器61和所述第二数字时间转换器62均与所述相位检测器/时间数字转换器63相连。其中,所述第一数字时间转换器1和所述第二数字时间转换器2的输入端分别作为所述零失配鉴相器6的两个输入端,所述相位检测器/时间数字转换器63作为所述零失配鉴相器6的输出端。所述状态机3连接至所述第一数字时间转换器1和所述第二数字时间转换器2的控制端,通过调节第一数字时间转换器61和/或第二数字时间转换器62来校正所述零失配鉴相器的相位失配。

如图10所示,本发明的参考时钟信号注入锁相环的消除失调方法应用于参考时钟信号注入锁相环电路包括第一脉冲生成器、第二脉冲生成器、状态机、脉冲选择放大电路、压控延迟线、零失配鉴相器和滤波器。所述脉冲选择放大电路连接至所述第一脉冲生成器和所述第二脉冲生成器的输出端均连接至的输入端,所述状态机与所述脉冲选择放大电路、所述零失配鉴相器、所述滤波器均相连,所述脉冲选择放大电路的输出与所述压控延迟线和所述零失配鉴相器分别相连,所述零失配鉴相器再与所述状态机和所述滤波器分别相连,所述滤波器与所述状态机与所述压控延迟线分别相连,所述压控延迟线再与所述第二脉冲生成器相连。

其中,本发明的参考时钟信号注入锁相环电路共包含有以下四个环路:

(1)一个失调消除环路(Offset Calibration Loop,OCL)

所述失调消除环路包括所述第一脉冲生成器、所述状态机、所述零失配鉴相器和所述脉冲选择放大电路。

(2)一个压控振荡环路(Voltage Controlled Oscillator Loop,VCO)

所述压控延迟线包括所述第二脉冲生成器、所述脉冲选择放大电路和所述压控延迟线。

(3)一个锁相环路(Phase Lock LOOP,PLL)

所述锁相环路包括第一脉冲生成器、第二脉冲生成器、所述零失配鉴相器、所述滤波器、所述压控延迟线和所述脉冲选择放大电路。

(4)一个注入锁相环路(Inject Lock Loop,ILL)

所述注入锁相环路包括所述第一脉冲生成器、所述第二脉冲生成器、所述状态机、所述脉冲选择放大电路、所述压控延迟线、所述零失配鉴相器和所述滤波器。

所述参考时钟信号注入锁相环的消除失调方法包括以下步骤:

步骤S1、通过状态机断开所述锁相环路和所述压控振荡环路,启用所述失调消除环路以采用所述第一脉冲生成器生成的第一脉冲信号来校正所述零失配鉴相器。

具体地,将锁相环切换到所述注入锁相环路和所述压控振荡环路,将所述参考时钟信号REF_CLK输入所述第一脉冲生成器以生成第一窄脉冲信号PUL_REFP。所述第一窄脉冲信号PUL_REFP经由所述脉冲选择放大电路输入所述压控延迟线,并分为两路输入所述零失配鉴相器。根据所述鉴相结果信号PD_OUT,所述状态机调节通过控制线tos_tune调节所述零失调鉴相器,直到所述鉴相结果信号PD_OUT的平均值为零,从而实现消除失调。

步骤S2、通过状态机启用所述锁相环路和所述压控振荡环路,用校正后的所述零失配鉴相器来锁定所述第二脉冲生成器生成的第二脉冲信号。

具体地,启用所述锁相环路和所述压控振荡环路,将所述参考时钟信号REF_CLK输入所述第一脉冲生成器以生成第一窄脉冲信号PUL_REFP,将压控延迟线输出信号VCO_VP输入所述第二脉冲生成器以生成第二窄脉冲信号PUL_VCOP。所述第二窄脉冲信号PUL_VCOP经由所述第二窄脉冲选择放大电路变更为第二宽脉冲信号DIRT_PUL输入所述压控延迟线和所述零失配鉴相器的一端;所述第一窄脉冲信号PUL_REFP经由所述第一脉冲选择放大电路变更为第一宽脉冲信号VCO_NEW输入所述零失配鉴相器的另一端。所述滤波器根据所述零失配鉴相器输出的相差PD_OUT调节所述压控延迟线输出的压控延迟线输出信号VCO_VP的均值,进而反过来调节所述零失配鉴相器输出的相差PD_OUT,直至所述相差PD_OUT均值为零,则实现了锁频。此时,所述参考时钟信号REF_CLK和所述压控延迟线输出信号VCO_VP的频率相同。

步骤S3、通过状态机将所述锁相环路切换到所述注入锁相环路,启用所述注入锁相环路以注入所述第一脉冲生成器生成的第一脉冲信号。

具体地,将锁相环路切换到所述注入锁相环路,启用所述注入锁相环路,将所述将所述参考时钟信号REF_CLK输入所述第一脉冲生成器以生成第一窄脉冲信号PUL_REFP,将压控延迟线输出信号VCO_VP输入所述第二脉冲生成器以生成第二窄脉冲信号PUL_VCOP。所述第一窄脉冲信号PUL_REFP经由所述第二脉冲选择放大电路变更为第第一宽脉冲信号VCO_NEW输入所述压控延迟线和所述零失配鉴相器的一端;所述第二脉冲信号PUL_VCOP经由所述第一脉冲选择放大电路变更为第二宽脉冲信号DIRT_PUL输入所述零失配鉴相器的另一端,从而实现所述注入锁相环路的参考时钟信号的注入。

需要说明的是,步骤S2和步骤S3可能会来回切换。其中,步骤S2切换为步骤S3的条件是:锁相环路锁定第二窄脉冲信号,锁定后的相位误差小于预设特定值时,锁相环路切换到注入锁相环路;步骤S3切换为步骤S2的条件是:当锁定后的相位误差大于所述预设特定值时,注入锁相环路将切回到锁相环路,重新锁定第二窄脉冲信号。

综上所述,本发明的参考时钟信号参考时钟信号注入锁相环电路及消除失调方法将参考时钟信号注入通路和锁相环鉴相通路合并成一个通路,并预先将鉴相器的失调清零,解决了参考时钟信号注入环路的相位失配问题参考时钟信号;消除了锁相环输出的时钟杂散;可应用于一般时钟生成器、倍频器、锁相环、CDR等电子电路或系统中。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

- 一种参考时钟信号注入锁相环电路及消除失调方法

- 一种参考时钟信号注入锁相环电路及消除失调方法