半导体集成电路及半导体集成电路的控制方法

文献发布时间:2023-06-19 11:27:38

相关申请

本申请享受以日本专利申请2019-227532号(申请日:2019年12月17日)作为基础申请的优先权。本申请通过参考该基础申请而包括基础申请的全部内容。

技术领域

实施方式涉及半导体集成电路及其控制方法。

背景技术

近年来,在将MOSFET作为开关元件而构成电源电路的半导体集成电路中,使用新的连接器的标准USB的Type-C,也能够进行与到最大100W的输出对应的电源供给。在处理这样的大功率的基础上,需要经由体二极管(body diode)对即使在MOSFET截止时也流过的逆流电流进行抑制。因此,开发出了被称为共漏(共漏)的、在硅上共用漏极的MOSFET。由此,能够抑制导通电阻的增大,并且也能够防止体二极管的逆流。

在共漏结构的MOSFET中,没有漏极端子、取而代之地成为源极端子为2个(源极S1、源极S2)、而且栅极端子也为2个(栅极G1、栅极G2)的基本4端子构成。因此,输入从微机等发送的控制信号的输入端子也需要2个,半导体集成电路的电路规模增加。

发明内容

实施方式提供能够抑制电路规模的增加的半导体集成电路及其控制方法。

根据本实施方式,半导体集成电路是驱动具有第一场效应晶体管和与第一场效应晶体管反向串联连接的第二场效应晶体管的开关元件的半导体集成电路,具备驱动电路和控制电路。驱动电路使第一场效应晶体管和第二场效应晶体管成为导通状态或截止状态。控制电路根据从一个信号输入端子输入的控制信号来控制驱动电路。

附图说明

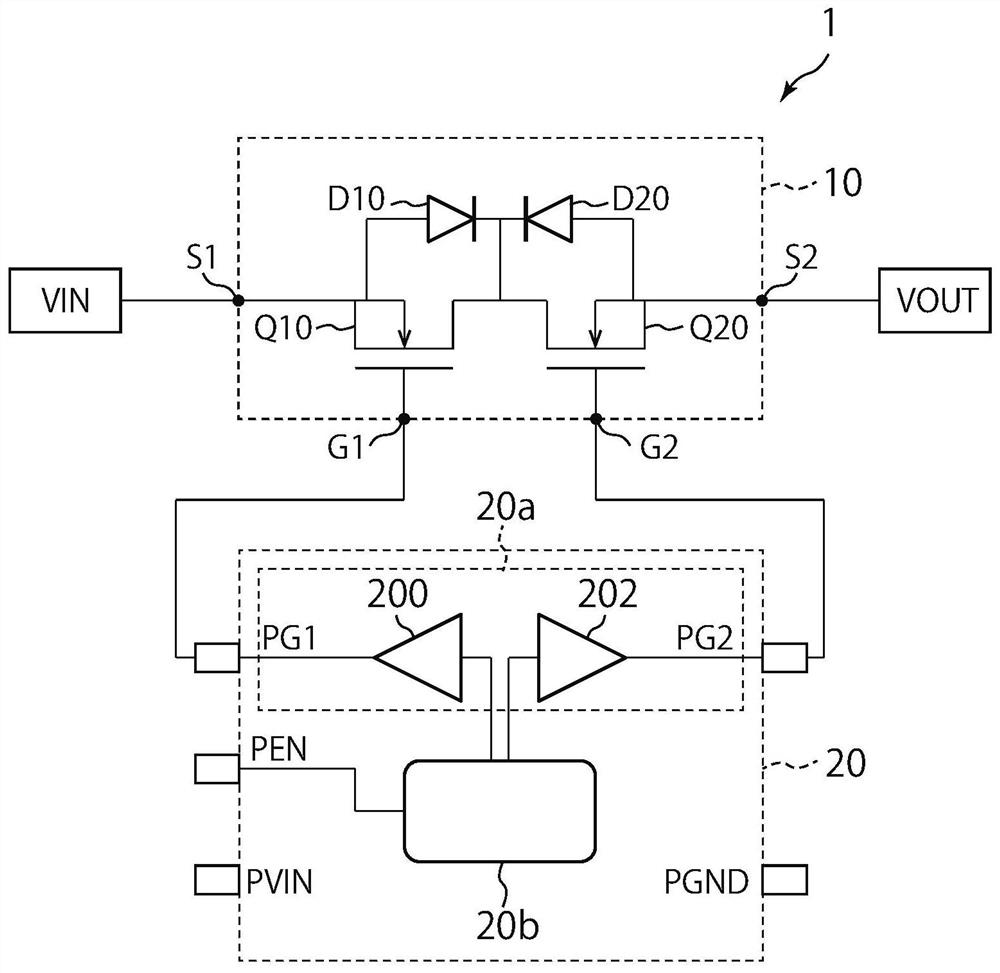

图1是表示第一实施方式的电源电路的结构的一例的框图。

图2是作为比较例的电源电路的结构的一例的框图。

图3是表示第二实施方式的电源电路的结构的图。

图4是表示第二实施方式的电源电路的比较例结构的图。

图5是表示第三实施方式的电源电路的结构的图。

图6是驱动控制电路真值表。

图7是表示控制信号为低电平信号的情况下的电流的流动的图。

图8是驱动控制电路的时序图。

图9是表示第四实施方式的电源电路的结构的图。

图10是第四实施方式的驱动控制电路的真值表。

图11是第四实施方式的驱动控制电路的时序图。

图12是表示时间电路的结构例的图。

图13是内部电路的电压波形图。

图14是表示时间电路的另一结构例的图。

图15是图14的时间电路的各节点的电压波形图。

图16是表示设置有时间电路的电源电路的结构例的图。

图17是表示时间电路中的振荡电路的结构例的图。

图18是图17的振荡电路的各节点的电压波形图。

具体实施方式

以下,参照附图对本发明的实施方式的半导体装置、数字控制振荡器、频率合成器以及半导体装置的控制方法进行详细说明。此外,以下所示的实施方式是本发明的实施方式的一例,本发明并不限定于这些实施方式来解释。另外,在本实施方式所参照的附图中,对相同部分或者具有相同功能的部分,标注相同的附图标记或者类似的附图标记,有时省略其重复的说明。另外,附图的尺寸比率为了便于说明而存在与实际的比率不同的情况、结构的一部分从附图中省略的情况。

(第一实施方式)

图1是表示第一实施方式的电源电路的结构的一例的框图。电源电路1是根据控制信号Cntr经由输出端子VOUT向负载供给来自电源端子VIN的电力的半导体集成电路。电源电路1具备输出电路10和驱动控制电路20。此外,输出电路10和驱动控制电路20是由2个半导体芯片构成的模块,但也可以由一个半导体芯片构成。

输出电路10是在电源端子VIN与输出端子VOUT之间具有第一场效应晶体管Q10和与第一场效应晶体管Q10反向串联连接的第二场效应晶体管Q20的开关元件。第一场效应晶体管Q10及第二场效应晶体管Q20例如是n沟道型的MOSFET(metal-oxide-semiconductorfield-effect transistor:金属氧化物半导体场效应晶体管)。即,在输出电路10中,第一场效应晶体管Q10的漏极与第二场效应晶体管Q20的漏极电连接。由此,寄生地形成于第一场效应晶体管Q10的体二极管D10的阴极和寄生地形成于第二场效应晶体管Q20的体二极管D20的阴极被电连接。将这样的连接称为共漏。在共漏结构的MOSFET中,没有漏极端子,取而代之地成为源极端子成为2个(源极S1、源极S2)、而且栅极端子也成为2个(栅极G1、栅极G2)的基本4端子构成。

第一场效应晶体管Q10导通、并且第二场效应晶体管Q20导通,由此能够使电流从电源端子VIN流向输出端子VOUT。在要使电流停止时,使第一场效应晶体管Q10截止、并且使第二场效应晶体管Q20截止。此时,该第二场效应晶体管Q20截止,并且电流的流动方向相对于体二极管D20的正向成为反方向。因此,通过该第二场效应晶体管Q20,电流的流动被阻止。

驱动控制电路20具有驱动电路20a和控制电路20b。

驱动电路20a将第一场效应晶体管Q10及第二场效应晶体管Q20设为导通状态或截止状态。该驱动电路20a具有第一驱动器200和第二驱动器202。第一驱动器200经由端子PG1与第一场效应晶体管Q10的栅极G1连接。同样地,第二驱动器202经由端子PG2与第二场效应晶体管Q20的栅极G2连接。

控制电路20b根据从一个端子PEN输入的控制信号Cntr来控制驱动电路20a。即,根据输入至端子PEN的信号的状态来决定驱动电路20a的使能(enable)或失能(disable)。在此,在控制信号Cntr为高电平的信号的情况下,驱动电路20a的第一驱动器200以及第二驱动器202成为使能状态。处于使能状态的第一驱动器200以及第二驱动器202向端子PG1以及端子PG2输出栅极电压,使第一场效应晶体管Q10以及第二场效应晶体管Q20成为导通状态。另一方面,在控制信号Cntr为低电平的情况下,停止栅极电压的输出,使第一场效应晶体管Q10以及第二场效应晶体管Q20成为截止状态。

控制电路20b的端子PGND与外部的接地或规定电位连接。控制电路20b的端子PVIN与使驱动控制电路20动作的电源连接。

图2是表示作为比较例的电源电路1a的结构的一例的框图。电源电路1a与图1所示的电源电路1的不同点在于,控制电路20b根据从端子PEN1、PEN2输入的不同的第一控制信号Cntr1、第二控制信号Cntr2来控制驱动电路20a。控制电路20b根据从端子PEN输入的第一控制信号Cntr1来控制驱动电路20a的第一驱动器200。即,在第一控制信号Cntr1为高电平的信号的情况下,第一驱动器200成为使能状态,向端子PG1输出栅极电压,使第一场效应晶体管Q10成为导通状态。另一方面,在第一控制信号Cntr1为低电平的情况下,停止栅极电压的输出,使第一场效应晶体管Q10成为截止状态。

同样地,在第二控制信号Cntr2为高电平的信号的情况下,第二驱动器202成为使能状态,向端子PG2输出栅极电压,使第二场效应晶体管Q20成为导通状态。另一方面,在第二控制信号Cntr2为低电平的情况下,停止栅极电压的输出,使第二场效应晶体管Q20成为截止状态。

这样,在驱动共漏的MOSFET的情况下,与栅极连接的端子需要为端子PG1和端子PG2这两个端子。在分别驱动第一场效应晶体管Q10、第二场效应晶体管Q20的情况下,输入信号的端子也需要为PEN1、PEN2这两个端子。另一方面,在以相同的控制信号驱动第一场效应晶体管Q10、第二场效应晶体管Q20的栅极的情况下,输入信号的端子也是PEN1、PEN2中的任意一个端子即可。在考虑端子数(管脚数)的情况下,在比较例中,需要端子PG1、端子PG2、端子PEN1、端子PEN2、端子PVIN、以及端子PGND这六个引脚。

如以上说明的那样,在本实施方式中,设为以相同的控制信号Cntr来驱动第一场效应晶体管Q10、第二场效应晶体管Q20的栅极。由此,控制信号Cntr的输入端子为一个,因此能够为5端子(5引脚)结构。

(第二实施方式)

第二实施方式的电源电路通过进一步具备电荷排出电路,而与第一实施方式的电源电路不同。以下,关于与第一实施方式的电源电路不同的点,以下进行说明。

图3是表示第二实施方式的电源电路1b的结构的图。如图3所示,本实施方式的电源电路1b还具备电荷排出电路22。本实施方式的电源电路1b通过将图1所示的电源电路1的5端子(5引脚)结构设为6端子结构而不同。即,增设了端子POUT。

电荷排出电路22的一端经由端子POUT与输出电路10的输出端子VOUT连接,另一端与地线连接。此外,虽然未图示,但被接地及与地线连接是指经由端子PGND而与地线或规定的电位连接。电荷排出电路22例如排出与输出电路10的输出端子VOUT连接的负载的电荷。

图4是表示第二实施方式的电源电路的比较例结构的图。如图4所示,本实施方式的比较例的电源电路1c还具备电荷排出电路22。本实施方式的比较例的电源电路1c的不同点在于,将图2所示的6端子(6引脚)结构设为8端子结构。即,增设了端子POUT和端子PNC。在输入信号的端子为端子PEN1、PEN2这两个的情况下,为了施加端子POUT,需要将电源电路设为7引脚。但是,在量产中的一般的封装中,在封装的两侧设置相同数量的引脚,因此没有7引脚类型的封装,如图4所示,一般使用通用且廉价的8引脚封装。这样,在比较例的电源电路1c中,为了追加1引脚,需要采用从6引脚增加了2引脚的8引脚封装,封装外尺寸也变大,因此基板空间也变大。

如以上那样,在本实施方式中,以相同的控制信号Cntr驱动第一场效应晶体管Q10、第二场效应晶体管Q20的栅极,因此仅将5引脚增加1引脚成为6引脚即可,在使用5引脚的插座(SOT)封装的情况下,即使设为6引脚也能够搭载于相同封装外尺寸的6引脚的插座(SOT),能够避免基板安装空间的增加。

(第三实施方式)

第三实施方式的电源电路通过进一步具备减压电路,而与第一实施方式的电源电路不同。以下,关于与第一实施方式的电源电路不同的点,以下进行说明。

图5是表示第三实施方式的电源电路1d的结构的图。如图5所示,本实施方式的电源电路1d还具备第一减压回路20c和第二减压回路20d。另外,驱动电路20a具有电荷泵电路204。

电荷泵电路204与第一驱动器200和第二驱动器202连接,将对电源电压Vin进行升压而得到的升压电压提供给第一驱动器200和第二驱动器202。由此,在输入至控制电路20b的控制信号Cntr为高电平的信号的情况下,升压后的栅极电压Vg1、Vg2经由第一驱动器200以及第二驱动器202分别被输出至端子PG1以及端子PG2。然后,第一场效应晶体管Q10和第二场效应晶体管Q20导通。栅极电压Vg1和Vg2是分别施加到第一场效应晶体管Q10的栅极G1和第二场效应晶体管Q20的栅极G2的电压。

另一方面,在控制信号Cntr为低电平的信号的情况下,停止升压后的电压向端子PG1以及端子PG2的输出。由此,第一场效应晶体管Q10及第二场效应晶体管Q20截止。

第一减压电路20c在第一场效应晶体管Q10截止的情况下,使第一场效应晶体管Q10的源极S1与栅极G1之间的电位差为第一场效应晶体管Q10的耐压以下。该第一减压回路20c具有第一减压开关元件Q1、第一接地开关元件Q3、第一电阻R1和第二电阻R2。

在第一场效应晶体管Q10截止的情况下,第一减压开关元件Q1使第一场效应晶体管Q10的源极S1与栅极G1之间短路。第一减压开关元件Q1例如是P沟道型MOS晶体管。更具体而言,第一减压开关元件Q1的源极经由端子PG1与第一场效应晶体管Q10的栅极G1连接。另外,第一减压开关元件Q1的漏极经由端子PVIN与第一场效应晶体管Q10的源极S1连接。当第一减压开关元件Q1导通时,端子PG1与端子PVIN短路,端子PG1的电压与端子PVIN的电压相等。由此,第一场效应晶体管Q10的源极S1与栅极G1间的电位差成为第一场效应晶体管Q10的耐压以下。

第一接地开关元件Q3连接在端子PG1与端子PGND之间。第一接地开关元件Q3在第一场效应晶体管Q10截止的情况下导通。由此,在第一场效应晶体管Q10截止时,将在端子PG1和端子PVIN积存的电荷导出到地线。

更详细而言,第一接地开关元件Q3例如是N沟道型MOS晶体管。第一接地开关元件Q3的漏极经由第二电阻R2与第一减压开关元件Q1的栅极连接,源极与地线连接,栅极与控制电路20b连接。另外,第一电阻R1的一端与第一减压开关元件Q1的栅极和第二电阻R2之间的节点n1连接,另一端与端子PG1连接。

第二减压回路20d也是与第一减压回路20c相同的结构。即,第二减压电路20d在第二场效应晶体管Q20截止的情况下,使第二场效应晶体管Q20的源极与栅极间的电位差为第二场效应晶体管Q20的耐压以下。该第二减压回路20d具有第二减压开关元件Q2、第二接地开关元件Q4、第三电阻R3以及第四电阻R4。

在第二场效应晶体管Q20截止的情况下,第二减压开关元件Q2使第二场效应晶体管Q20的源极S2与栅极G2之间短路。第二减压开关元件Q2例如是P沟道型MOS晶体管。更具体而言,第二减压开关元件Q2的源极经由端子PG2与第二场效应晶体管Q20的栅极G2连接。另外,第二减压开关元件Q2的漏极经由端子POUT与第二场效应晶体管Q20的源极S2连接。当第二减压开关元件Q2导通时,端子PG2与端子POUT被短路,端子PG2的电压与端子POUT的电压相等。由此,第二场效应晶体管Q20的源极S2与栅极G2之间的电位差成为第二场效应晶体管Q20的耐压以下。

第二接地开关元件Q4连接在端子PG2与端子PGND之间。在第二场效应晶体管Q20截止的情况下,第二接地开关元件Q4导通。由此,在第二场效应晶体管Q20截止时,将在端子PG2和端子POUT积存的电荷导出到地线。

第二接地开关元件Q4例如是N沟道型MOS晶体管。更详细而言,第二接地开关元件Q4的漏极经由第四电阻R4与第二减压开关元件Q2的栅极连接,源极与端子PGND连接,栅极与控制电路20b连接。另外,第三电阻R3的一端与第二减压开关元件Q4的栅极与第四电阻之间的节点n2连接,另一端与端子PG2连接。

以上是第三实施方式的电源电路1的结构的说明,以下使用图6至图9对动作例进行说明。图6是驱动控制电路20的真值表。在本实施方式中,高电平信号用H表示,低电平信号用L表示。

图7是表示控制信号Cntr为低电平信号(L)的情况下的电流的流动的图。电流Ivin是从电源端子VIN流向第一减压开关元件Q1的电流,电流Iout是从输出端子VOUT流向第二减压开关元件Q2的电流。电源电压Vin是电源端子VIN的电压。电压Vout是输出端子VOUT的电压。

图8是驱动控制电路20的时序图。图8的(a)~(h)分别是控制信号Cntr、控制信号en、第一场效应晶体管Q10的栅极电压Vg1、第一场效应晶体管Q10的栅极源极间电压Vgs1、电流Ivin、第二场效应晶体管Q20的栅极电压Vg2、第二场效应晶体管Q20的栅极源极间电压Vgs2、电流Iout。横轴为时间。期间1表示控制信号Cntr为高电平信号(H)的期间,期间2及期间3表示控制信号Cntr为低电平信号(L)的期间。

首先,对向端子PEN输入的控制信号Cntr为高电平信号(H)的情况下的动作例进行说明。控制信号en是输入至端子PEN的控制信号Cntr的反转信号,当控制信号Cntr成为高电平(H)时,控制信号en成为低电平(L)。即,在期间1中,输入至控制电路20b的控制信号Cntr是高电平信号(H),从控制电路20b输出的控制信号en是低电平信号(L)。由此,升压后的栅极电压Vg1、Vg2经由第一驱动器200以及第二驱动器202分别输出至端子PG1以及端子PG2。

栅极电压Vg1为Vg1=Vin+Vgs1。栅极电压Vg2为Vg2=Vin+Vgs2。

栅极电压Vg1、Vg2具有Vg1的(=Vg2)≥Vin+Vth的关系。这里,Vth是第一场效应晶体管Q10及第二场效应晶体管Q20的阈值电压。因此,第一场效应晶体管Q10及第二场效应晶体管Q20导通。

控制电路20b根据被输入的控制信号Cntr输出控制信号en。如上所述,控制信号en是控制信号Cntr的反转信号。当控制信号en变为低电平信号(L)时,第一接地开关元件Q3及第二接地开关元件Q4截止。由此,第一减压开关元件Q1及第二减压开关元件Q2的栅极和源极分别被电阻R1、R3短路而截止。然后,电流Ivin、Iout成为0。

在此,第一减压开关元件Q1、第二减压开关元件Q2、第一接地开关元件Q3以及第二接地开关元件Q4,从源极或者漏极的高电位侧向低电位侧的方向与体二极管的正向的朝向相反,因此不易从栅极G1以及栅极G2泄漏电荷。进而,电阻R1、R2、R3、R4通过电阻分割,防止对第一减压开关元件Q1、第二减压开关元件Q2、第一接地开关元件Q3及第二接地开关元件Q4施加大的电压。

接下来,将图6作为参考,使用图7及图8对控制信号Cntr为低电平信号(L)的情况下的动作例进行说明。

在期间2的开始,向端子PEN输入的控制信号Cntr切换为低电平信号(L),控制信号en成为高电平信号(H)。当控制信号en变为高电平信号(H)并且第一驱动器200和第二驱动器202的输出截止时,开关元件Q1至Q4导通。

在此,首先关注第一减压开关元件Q1、第一接地开关元件Q3时,第一接地开关元件Q3导通。由此,从端子PG1经由电阻R1、R2在接地(端子PGND)产生电流路径。由电阻R1、R2分压后的电压成为第一减压开关元件Q1的栅极源极间电压,第一减压开关元件Q1导通。此时,蓄积于端子PG1的电荷经由第一减压开关元件Q1、电阻R1、R2,通过第一接地开关元件Q3与接地(端子PGND)接地而被放电。期间2表示该动作。

在期间2中,端子PG1的电位Vg1接近PVIN端子的电压Vin。在此,第一减压开关元件Q1的导通电阻(RonQ1)为RonQ1<<R1、R2。另外,在期间2中来自端子PG1的放电电流向端子PVIN流出,因此电流Ivin被测定为负的电流。

第一场效应晶体管Q10的栅极源极间电压Vgs1在期间1被施加电压(Vg1-Vin)。在第一驱动器200及第二驱动器202的输出截止的期间2中,第一场效应晶体管Q10的栅极电荷被放电,栅极源极间电压Vgs1逐渐接近0V,栅极电压Vg1如上所述,与电源电压Vin相等。这样,在第一驱动器200及第二驱动器202的输出截止时,该驱动控制电路20通过使第一场效应晶体管Q10的栅极G1电位和源极S1电位为相同电位,从而避免第一场效应晶体管Q10的栅极、源极间的耐压超过。对第一场效应晶体管Q10进行了说明,但关于第二场效应晶体管Q20也是同样的。

接着,在栅极电压Vg1变得与电源电压Vin相等之后的期间3中,端子PG1与端子PVIN之间的电流不存在,仅产生端子PVIN与接地(端子PGND)间的电流。该电流Ivin作为在控制信号Cntr为L的期间稳定地持续流动的DC电流而被消耗。关于端子PG2、端子POUT也同样地动作。

如以上说明的那样,根据本实施方式,在第一场效应晶体管Q10、第二场效应晶体管Q20截止的情况下,第一减压电路20c及第二减压电路20d分别使第一场效应晶体管Q10及第二场效应晶体管Q20的栅极G1、G2、源极S1、S2间成为相同电位。由此,能够防止第一场效应晶体管Q10及第二场效应晶体管Q20的栅极G1、G2、源极S1、S2间的耐压超过。

(第四实施方式)

第四实施方式的电源电路通过进一步具备时间电路,而与第三实施方式的电源电路不同。以下,关于与第三实施方式的电源电路不同的点,以下进行说明。

图9是表示第四实施方式的电源电路1e的结构的图。如图9所示,本实施方式的电源电路1e还具备时间电路20e。另外,在图9中,还图示了电流Ivin、Iout。

时间电路20e配置在将控制电路20b与第一接地开关元件Q3及第二接地开关元件Q4的栅极之间连接的信号线的中途。即,该时间电路20e的一端与控制电路20b连接,另一端与第一接地开关元件Q3的栅极以及第二接地开关元件Q4的栅极连接。另外,时间电路20e在控制信号en成为高电平信号(H)时成为高电平信号(H),在经过规定时间后将成为低电平信号(L)的控制信号sn3输出至第一接地开关元件Q3以及第二接地开关元件Q4的栅极。

图10是本实施方式的驱动控制电路20的真值表。图11是本实施方式的驱动控制电路20的时序图。图11的(a)~(i)分别是控制信号Cntr、控制信号en、时间电路20e输出的控制信号sn3、第一场效应晶体管Q10的栅极源极间电压Vgs1、第一场效应晶体管Q10的栅极电压Vg1、电流Ivin、第二场效应晶体管Q20的栅极源极间电压Vgs2、第二场效应晶体管Q20的栅极电压Vg2、电流Iout。横轴为时间。

使用图10、图11,对本实施方式的驱动控制电路20的动作例进行说明。第一期间、第二期间以及第三期间与第三实施方式的驱动控制电路20的动作相同。

时间电路20e的控制信号sn3在控制信号en从低电平(L)切换为高电平(H)的定时从低电平(L)变为高电平(H)。然后,当经过所设定的时间时,控制信号sn3成为低电平(L)。在第一接地开关元件Q3和第二接地开关元件Q4导通的期间2和期间3中生成电流路径,电流持续流过。时间电路20e通过将控制信号sn3设为低电平(L)信号,从而在规定时间后、即经过期间3后的期间4使第一接地开关元件Q3以及第二接地开关元件Q4截止。由此,能够使在第三期间中稳定地流过第一场效应晶体管Q10的电流Ivin、稳定地流过第二场效应晶体管Q20的电流Iout在期间4为零。

在此,使用图12、图13,对时间电路20e的结构例进行说明。

图12是表示时间电路20e的结构例的图。另外,图13是其内部电路的电压波形图。即,示出了图12的时间电路20e的各节点的电压波形的示意图。图13的(a)~(d)分别是输入至控制信号en、节点n31的信号sn31、输入至节点n32的信号sn32、输入至节点n3的信号sn3。横轴为时间。另外,t0对应于期间1的(图11),t1对应于期间2(图11)+期间3的(图11),t2对应于期间4(图11)。

如图12所示,时间电路20e由2个逆变器电路(INV)、电阻R、电容C、2输入逻辑和电路(NOR)构成。NOR电路的一个输入被输入经由反相器电路(INV)的控制电路20b(图3)的控制信号en的反转信号。该控制信号en是输入至端子PEN的控制信号Cntr的反转信号,当控制信号Cntr成为低电平(L)时,控制信号en成为高电平(H)。

在另一个输入中,被输入进一步经由逆变器电路(INV)的反转信号、即控制信号en,但在INV电路的输出与NOR电路的输入之间配置由电阻R和电容C构成的RC延迟电路,在延迟了由电阻值和电容值的常数决定的时间后被输入。

时间电路20e利用该延迟时间生成以期望的期间将电路设为使能的控制信号。NOR电路的输出(sn3)驱动第一接地开关元件Q3及第二接地开关元件Q4各自的栅极。更具体而言,在控制信号en为低电平(L)的期间(t0),向NOR电路的一个输入输入高电平(H)的信号,向另一个节点n32输入低电平(L)的信号sn32,NOR电路的输出成为低电平(L)。

接着,当控制信号en从低电平(L)切换为高电平(H)时,NOR电路的一个输入切换为低电平(L)。作为另一个输入的节点n31的信号sn31,INV电路的输出从低电平(L)瞬间切换为高电平(H)。但是,节点n32的信号sn32通过由RC构成的延迟电路,产生从低电平(L)向高电平(H)、切换延的迟期间(t1)。在该期间,NOR电路的2输入均被输入低电平(L),因此输出(sn3)成为高电平(H)。之后,如果信号sn32达到高电平(H),则NOR电路的输出成为低电平(L)。在该期间(t2),控制信号Cntr为低电平(L),但NOR电路的输出sn3为低电平(L),第一接地开关元件Q3以及第二接地开关元件Q4均截止。

接着,使用图14、图15,对时间电路20e的另一结构例进行说明。

图14是表示时间电路20e的另一结构例的图。图15是图14的时间电路20e的各节点的电压波形图。图15的(a)~(l)分别是POR电路输出的控制信号por、控制信号en、输入至节点n11的信号sn11、输入至节点n12的信号sn12、输入至节点n13的信号sn13、输入至节点n14的信号sn14、输入至节点n15的信号sn15、信号clk、D-type触发电路(DFF1)的Q输出即sq1、D-type触发电路(DFF2)的Q输出即sq2、D-type触发电路(DFFn)的Q输出即sqn、逻辑和电路(OR)的输出即信号rco(sn3)。横轴为时间。t3对应于期间1的(图11),t4对应于期间2(图11+期间3的(图11),t5对应于期间4(图11)。

如图14所示,设置振荡电路(Oscillator),利用计数器电路对振荡电路中生成的时钟(clk)的脉冲数进行计数。如果计数到预先设定的数量的脉冲,则生成作为触发信号的Ripple Carry Out(rco)。该rco信号被输入至D-type触发电路(DFF0)的上升沿的时钟端子。DFF0的数据端子(D)被上拉到电源电压(Vin)。DFF0的Qb输出成为2输入逻辑积电路(AND1)的输入信号。AND 1电路的另一方的输入被输入对驱动器IC进行enable/disable控制的控制信号en,输出sn13被输入至振荡电路。在向振荡电路输入高电平信号时,振荡电路成为动作状态,产生时钟脉冲。

该时间电路20e还设置有Power-On-Reset(POR)电路,以在接通电源电压Vin后设定全部的D-type触发电路的初始值。现在,全部的D-type触发电路(DFF0~DFFn)的初始值被设定为“0”,sq1~sqn输出为L(期间t3)。在此,当被输入将驱动器IC设为disable的高电平的控制信号en时,节点n11的信号sn11成为高电平。DFF0的Q输出的反相逻辑即Qb输出的节点n14的信号sn14的初始值为高电平,因此2输入均为高电平,AND1的输出(sn13)为高电平。由此,振荡电路成为动作状态,生成时钟脉冲。作为振荡电路的输出的信号clk成为D-type触发电路(DFF1)的上升沿的时钟输入。

DFF1的数据输入D与Qb输出连接,进行双稳态(toggle)动作。当来自振荡电路的clk的上升沿被输入至DFF1时,Q输出(sq1)将输出状态与另一D-type触发电路(DFF2)的时钟输入连接,并且与逻辑和电路(OR)的输入连接。通过该电路结构实现计数的功能。在图15中,由n个D-type触发电路构成,振荡电路的时钟脉冲被计数2n个。当振荡电路成为动作状态,而第一个clk的上升被输入至FF0时,信号sq1切换为高电平。该信号sq1被输入至DFF2的CLK端子,信号sq2也被切换为高电平。最后的DFFn也同样地动作,其结果,全部的Q输出(sq1~sqn)成为高电平。这些信号sq1~sqn成为逻辑和OR电路的输入,因此作为其输出的rco(sn3)信号成为高电平。

之后,若来自振荡电路的时钟达到2n个,则D-type触发电路的Q输出(sq1~sqn)全部成为低电平,OR电路输出的输出即信号rco成为低电平。该rco(sn3)信号经由INV2电路与DFF0电路的CLK输入连接。由于rco信号的反相信号被输入,所以FF0的Qb输出(sn15)从高电平切换到低电平。由于该sn15信号被输入至AND1,所以AND1的输出即信号sn13成为低电平,停止振荡电路的动作。

该信号rco(sn3)与第一接地开关元件Q3以及第二接地开关元件Q4(图9)的栅极连接,仅在高电平的信号被输出的期间导通(期间t4)。之后的期间(t5)中,控制信号en为低电平,但由于信号rco(sn3)保持低电平不变,因此第一接地开关元件Q3和第二接地开关元件Q4(图9)均截止。这样,将振荡器电路的周期设为T时,期间t4被设定为t4=T*2n。

接着,使用图16至图18,对时间电路20e内的振荡电路(Oscillator)的结构例进行说明。图16是表示设置有时间电路20e的电源电路1f的结构例的图。图17是表示时间电路20e中的振荡电路(Oscillator)的结构例的图。图18是图17的振荡电路的各节点的电压波形图。图18的(a)~(e)分别是控制信号Cntr、节点n21的输入信号sn21、节点n22的输入信号sn22、节点n23的输入信号sn23、信号clk。横轴为时间。

如图16所示,电源电路1对时间电路20e设置2个外接用端子PADJ1、PADJ2,能够连接外接部件。如图17所示,将时间电路20e内的振荡电路(Oscillator)的频率设为在外接部件中可变对应。振荡电路是一般已知的被称为环形振荡器的振荡电路,通过由晶体管Q21~Q24构成的2输入逻辑积(NAND)电路、由晶体管Q25以及晶体管Q26、晶体管Q27以及晶体管Q28构成的INVETER电路、电阻R以及电容C构成。对逻辑积电路的晶体管Q21、Q24的输入输入控制信号Cntr,若输入低电平的信号则停止振荡动作。将包含NAND电路的INVERTER电路串联连接3个,将第三个INVERTER(Q27、Q28)的输出(clk)连接到NAND电路的INVERTER(Q22、Q23)的输入,由此进行振荡动作。

振荡频率由内部电路的延迟时间决定,但在图17的电路中,设置电阻R和电容C,通过利用RC时间常数来设定振荡频率。电阻R配置在节点clk与节点n21之间,电容C配置在节点n21与n23之间。

如图18所示,在接通电源VDD后,当输入控制信号Cntr、输入低电平的信号时,停止振荡动作。当将NAND信号从低电平切换为高电平时,开始振荡动作。在此,假设NAND电路、INVERTER电路的阈值电压全部为相同的VTH。信号sn22、sn23、clk是以VSS~VDD为振幅的矩形波。信号sn21不是以VSS-VDD为振幅的矩形波,而是以-VTH~VDD+VTH为振幅的以RC时间常数决定的电荷、放电的电压波形。该低电平、高电平的电压与电容C的施加电压和内部电路的延迟时间有关。在电容C的单侧连接有节点n21,另一侧连接于节点n23,但若节点n21达到阈值电压VTH,则接收到该信号的晶体管Q2、Q3的输出sn22与节点n21相比瞬时切换。

进而,接收节点n22的信号的晶体管Q25、Q26的输出即信号sn23也瞬时切换。在与电容C的单侧连接的节点n23的输入信号sn23从高电平切换为低电平的期间(t1)的情况下,节点n23的电压从VDD成为VSS,电位差成为VDD-VSS。此时,与电容C的另一侧连接的节点n21还是阈值电压VTH附近的电压,因此,根据输入信号sn23的切换,成为VTH-(VDD-VSS)的电位。

若VSS=0V,则成为VTH-VDD的电位。同样,在输入信号sn23从L向H切换的期间(t2)的情况下,VTH+(VDD-VSS)=VTH+VDD。clk信号是信号sn23的反相输出,其周期T由T=t1+t2求出,频率F以F=1/T求出。接着,具体求出t1、t2。RC电路的充电特性由式(1)表示。V是时间t后的充电电压,E是供给电压。

若对时间t求解该时间t,则成为式(2)。

RC电路的放电特性通过式(3)表示,同样地按时间t求解时求出式(4)。

如图18所示,求出电压从-VTH充电至VTH的时间t1。在此,若将电压为-VTH时的时间设为t1_a,将达到VTH的时间设为t1_b,则通过式(5)求出t1。

t1=t1_b-t1_a--(5)

根据式(2),若分别计算t1_a、t1_b,则成为式(6)。在此,由于用-VTH=VTH=VDD进行置换,因此求出式(7)。

同样地计算t1_b时,求出式(8)。

通过将式(6)和式(8)到式(5),求出式(9),并计算充电时间t1。

接着,求出电压从VDD+VTH放电至VTH的时间t2。放电时的时间由式(4)计算,求出式(10)。

振荡器电路以由当前求出的充电时间t1和放电时间t2决定的周期(T=t1+t2)进行振荡,因此根据式(9)、式(10),T为式(11)。

在此,假设VTH=2/VDD,代入到式(11),则求出式(12)。

振荡频率F以F=1/T求出,F=1/2.196CR。

如上所述,振荡电路的频率由电阻R和电容C决定,因此通过改变R和C的常数,能够使频率可变。图17的例子除了设置于IC内的电容之外,还设置有追加外接电容的2个端子PADJ1、PADJ2。若将外接电容设为C_ext,则此时的振荡频率为1/R(C+C_ext)。

如以上说明的那样,根据本实施方式,设置了时间电路20e,在第一场效应晶体管Q10及第二场效应晶体管Q20截止并经过规定的时间后使第一接地开关元件Q3及第二接地开关元件Q4截止。由此,第一场效应晶体管Q10及第二场效应晶体管Q20开始截止,在将蓄积于端子PG1、端子PG2的电荷导出至地线之后,第一接地开关元件Q3及第二接地开关元件Q4能够截止。因此,在第四期间中,能够切断稳定地流动的电流Ivin、Iout。

以上,对本发明的几个实施方式进行了说明,但这些实施方式是作为例子进行的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

- 半导体集成电路、包括半导体集成电路的系统设备及半导体集成电路控制方法

- 半导体集成电路装置、半导体集成电路装置的安装结构及半导体集成电路装置的制造方法