存储器器件、随机数发生器及其操作方法

文献发布时间:2023-06-19 12:00:51

技术领域

本发明的实施例涉及存储器器件、随机数发生器及其操作方法。

背景技术

随机数发生器(RNG)是一种生成只有随机概率能最合理地预测的数字或符号序列的器件。由于RNG对于潜在的攻击者来说不可预测,所以其广泛用于安全应用中。可以由真随机(即,非确定性)物理源或由确定性算法来生成由RNG生成的这些随机数。通用的RNG架构可以组合这两种类型的RNG(即,非确定性RNG和确定性RNG)。具体而言,非确定性RNG用于提供非确定性种子,该非确定性种子用作生成更大量的伪随机比特的确定性随机比特发生器(DRBG)算法的输入。

发明内容

根据本发明实施例的一个方面,提供了一种存储器器件,包括:多个位线;多个字线;存储器单元阵列,包括耦合到位线和字线的多个位单元,位单元中的每一个配置为在位线上呈现初始逻辑状态;电源端子,耦合到存储器单元阵列;以及控制器,耦合到字线和位线,控制器配置为:在RNG阶段期间,将位线预充电到低于第一电压电平的第二电压电平,并且确定多个位单元的初始逻辑状态以生成随机数,第一电压电平是用于在SRAM阶段期间操作存储器单元阵列的电压电平。

根据本发明实施例的另一个方面,提供了一种随机数发生器(RNG),包括:存储器单元阵列,具有耦合到多个位线和多个字线的多个位单元,每个位单元包括多个晶体管并且配置为当RNG加电时呈现初始逻辑状态并且在位线上输出初始逻辑状态;电源端子,耦合到存储器单元阵列并且配置为将第一电压电平提供到存储器单元阵列;输入端子,配置为接收关断信号;头部开关,连接在电源端子和存储器单元阵列之间,头部开关响应于关断信号;字线驱动器,耦合到单元阵列,单元阵列配置为将字线信号输出到存储器单元阵列;以及延迟电路,连接在输入端子和字线驱动器之间,并且配置为响应于关断信号延迟字线信号到字线驱动器的输出,使得在字线信号被存储器阵列接收之前由头部开关接收关断信号。

根据本发明实施例的又一个方面,提供了一种操作随机数发生器的方法,包括:接收关断信号;响应于关断信号,将第一电压电平施加到存储器阵列,存储器单元阵列具有耦合到多个位线和多个字线的多个位单元;在随机数发生器(RNG)阶段期间将位线预充电到低于第一电压电平的第二电压电平;在RNG阶段期间发起字线假信号;以及在RNG阶段期间确定位单元的初始状态。

附图说明

当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各方面。应该注意,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

图1是根据一些实施例的SRAM RNG的实例的框图。

图2A是根据一些实施例的SRAM器件的实例的框图。

图2B是说明根据一些实施例的可用于图2A的SRAM器件中的位单元的实例的电路图。

图3A和图3B是示出根据一些实施例的当访问单元时的示例性SRAM单元行为的示意图。

图4A和图4B示出根据一些实施例的SRAM加电行为的实例。

图5是根据一些实施例的SRAM加电RNG的实例的框图。

图6是根据一些实施例的SRAM加电RNG的实例的时序图。

图7A-图7C示出了根据一些实施例的SRAM加电RNG的随机性与循环时间之间的示例性关系。

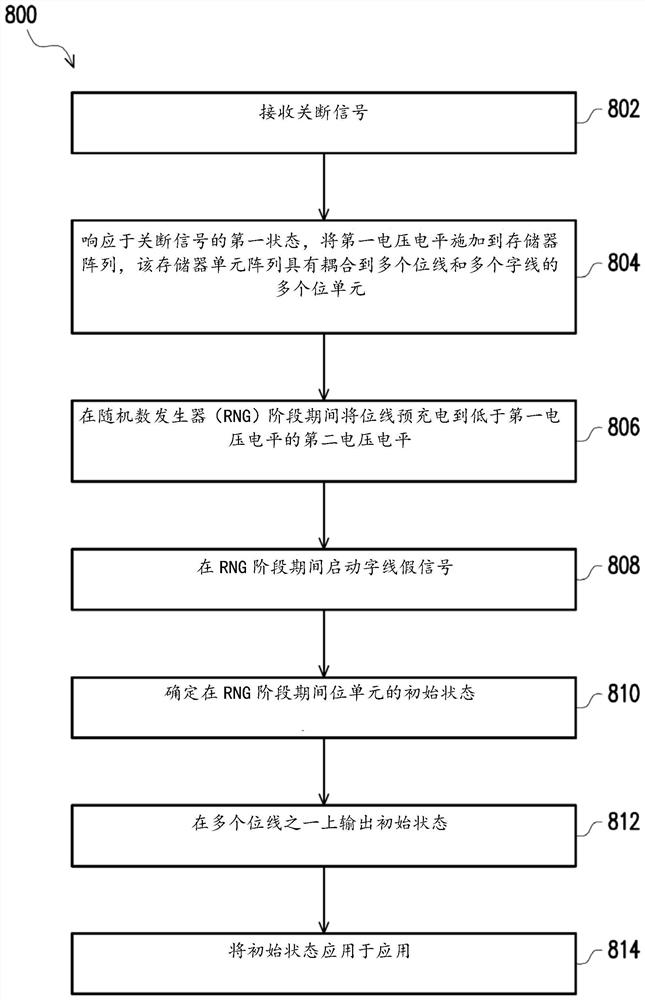

图8是根据一些实施例的用于操作SRAM加电RNG的示例性方法的流程图。

具体实施方式

以下公开内容提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

而且,为了便于描述,在此可以使用诸如“在…之下”、“在…下方”、“下部”、“在…之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。器件可以以其他方式定向(旋转90度或在其他方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。

静态随机存取存储器(SRAM)是一种使用双稳态锁存电路来将每一位存储在存储器阵列中的半导体存储器类型。虽然SRAM在存储器阵列中维持数据而不需要在加电时刷新,但其仍是易失性的,使得在存储器未加通时数据最终丢失。通常对存储器阵列实施功率门控及电压保持技术以减少功耗。例如,电源门可用于在深度休眠模式中断开存储器外围项目,且在关断模式中断开外围项目和存储器阵列两者。

图1是示出根据一些实施例的SRAM随机数发生器(RNG)101的实例的框图。在该实施例中,SRA RNG 101至少包括存储器控制器102、RNG控制器102、单元阵列200和输入/输出(IO)单元108。单元阵列200包括以阵列方式布置的多个位单元,这将在下面参考图2A和图2B进行详细描述。存储器控制器102连接到单元阵列200并控制单元阵列200的一般操作。RNG控制器104还连接到单元阵列200,并且控制单元阵列200的与RNG相关的操作,这将在下面参考图5和图6进行详细描述。在一些实施例中,RNG控制器104可以是存储器控制器102的一部分。换言之,RNG控制器104和存储器控制器102可以组合在一起。IO单元108连接到单元阵列200、存储器控制器102和RNG控制器104。IO单元108控制数据、地址和控制信号流入和流出单元阵列200。

图2A示出了根据一些实施例的SRAMR NG器件101的单元阵列200的实例的多个方面。如图2A所示,单元阵列200包括以阵列方式布置的多个位单元210。为了简单起见,在该实施例中,单元阵列200具有n行和两列位单元210。应当注意,可以使用其他行号和列号,并且典型的SRAM将包括更多的行和列。每行与字线(WL)220(即,WL0,WL1,…和WLn)相关联,而每列与一对位线(即,BLO 232和BLB0236;BLI 234和BLB1238)相关联。

图2B是示出在一些公开的实施例中可以在SRAM器件100中采用的位单元210的实例的电路图。位单元210包括但不限于六晶体管(6T)SRAM结构。在一些实施例中,可以使用多于或少于六个晶体管来实施位单元210。例如,在一些实施例中,位单元210可以使用4T、8T或10T SRAM结构,而在其他实施例中,位单元210可以包括类似存储器的位单元或构建单元。位单元210包括由NMOS/PMOS晶体管对M1和M2形成的第一反相器,由NMOS/PMOS晶体管对M3和M4形成的第二反相器,以及存取晶体管/传输门M5和M6。晶体管M1、M3、M5和M6包括n型金属氧化物半导体(NMOS)晶体管,而晶体管M2和M4包括p型金属氧化物半导体(PMOS)晶体管。

该第一反相器和第二反相器经由交叉耦合线202和204相互交叉耦合以形成用于数据存储的锁存电路。例如,交叉耦合线202耦合在第一反相器晶体管对的第二端子(例如M1和M2)与第二反相器晶体管对的门(例如M3和M4)之间。类似地,交叉耦合线204耦合在第二反相器晶体管对(例如,M3和M4)的第二端子与第一反相器晶体管对(例如,M1和M2)的门之间。这样,节点Qbar处的第一反相器的输出耦合到第二反相器的输入,并且节点Q处的第二反相器的输出耦合到第一反相器的输入。功率供给每个反相器,例如,每个晶体管M2和M4的第一端子耦合到电源端子240上的阵列电源电压VDDA,而每个晶体管M1和M3的第一端子耦合到参考电压VSS,例如,地面。一位数据作为节点Q处的电压电平存储在位单元210中,并且可以经由位线(连接漏极)BL由电路读取。通过传输门晶体管M6控制对节点Q的访问。节点Qbar将补码存储到Q处的值,例如,如果Q是“逻辑高不足”,则Qbar将是“逻辑低不足”,并且由传输门晶体管M5控制对Qbar的访问。

传输门晶体管M6的门耦合到字线220之一。传输门晶体管M6的第一源极/漏极耦合到位线(连接漏极)BL,传输门晶体管M6的第二源极/漏极端子在节点Q处耦合到晶体管M4和M3的第二端子。类似地,传输门晶体管M5的门耦合到字线(连接栅极,高通低止)WL。传输门晶体管M5的第一源极/漏极端子耦合到互补位线(连接漏极)BLB,并且传输门晶体管M5的第二源极/漏极端子在节点Qbar(i.e.,“Q”或“QB”)处耦合到晶体管M2和M1的第二端子。

再次参考图2A,字线220控制位单元210中的存取晶体管M5、M6,其确定哪些位单元210连接到对应对的位线。例如,对于第二行和第二列中的位单元210,当相应字线(即,WL1)处于逻辑高(1)时,位单元210中的存取晶体管接通。因此,位单元210连接到对应的位线对(即,BLB1234和BLB1238),其用于传输用于读取和写入操作两者的数据。在电源端子240处提供电压VDDA作为每个位单元210的电源电压。

SRAM加电过程可用作RNG的一部分。在加电时,位单元210将呈现初始逻辑状态并在对应字线220被致能时在位线上输出初始逻辑状态。例如,在加电时,存储器阵列的一些位单元将一致地默认为逻辑高值,其它位单元将一致被默认为逻辑低值。这些单元可分别被称为稳定1单元和稳定O单元。其它位单元将在加电时在逻辑高与逻辑低之间随机变化。这些单元可被称为不稳定单元。

当SRAM交叉耦合反相器对的强度非常接近时,SRAM加电行为是非确定性随机的。因此,SRAM可以为RNG提供随机种子。SRAM单元阵列中的位单元可以以三种不同的状态结束:不稳定位、稳定1位和稳定0位。落入上述状态之一的阵列中的SRAM单元的量受到工艺变化的影响。当SRAM阵列在正常操作模式下操作时,具有不稳定位的位单元可以占整个单元阵列中的一定百分比(例如,约5%-20%)。就RNG而言,通常不期望具有稳定的1比特的位单元和具有稳定的0比特的位单元,因为它们不是随机的。对于作为RNG的应用,可能期望最大化可以用作随机数发生器的非确定性种子的不稳定比特的数量。

图3A和图3B示出根据一些实施例的SRAM加电行为的实例。具体而言,当如图3A所示使能WL信号时,SRAM的反相器对中的每个反相器具有如图3B所示的噪声容限行为。BL和BLB用作通过M5和M6到Q和QBar的两个反相器的输入。由于交叉耦合的反相器对分别具有Q和QBar(QB)作为输入/输出和输出/输入,所以图3B使用Q作为输入,并且使用QBar(QB)作为输出,用于如图2B所示由M1和M2构成的反相器。另一个反相器(M3和M4)以QB(x轴)作为输入,而以Q作为输出。这两个反相器的两个输入/输出曲线被绘制在相同的图(即,图3B)中。由两条输入/输出转移曲线封装的两个方块通常称为噪声容限(NM)方块。

图4A和图4B示出根据一些实施例的SRAM加电行为的实例。一般而言,变化的WL电压、WL假信号的存在以及将BL电压预充电到不稳定区域中的值是用于RNG目的的SRAM加电期间的随机性的来源。

如图3A所示,在加电过程中,BL/BLB信号310从0增加到VDD 314。具体而言,BL/BLB信号310首先是零(即,未预充电的位线)。在时间t1301、BL/BLB信号310开始上升(即,位线开始被预充电)。在时间t2302,BL/BLB信号310上升到阈值电压Vth 312。一旦位单元210中的晶体管具有Vth 312的门电压,那么位单元210中的那些晶体管被接通。Vth312随不同的工艺和技术节点(例如,10nm和7nm)而变化。在一个实施例中,Vth 312为0.2V。在另一实施例中,Vth 312为0.5V。在时间t3,BL/BLB信号310上升到VDD 314。对于传统SRAM,一旦位单元210中的晶体管具有VDD 314的门电压,那么位单元210中的那些晶体管就准备好进行读取和写入操作。类似地,VDD 314随不同的工艺和技术节点(例如,10nm和7nm)而变化。在一个实施例中,VDD 314是0.75V。在另一个实施例中,VDD 314是0.9V。

静态噪声容限(SNM)被定义为在改变状态之前位单元210的交叉耦合反相器能够容忍的静态噪声的最大值。换言之,当直流(DC)噪声大于SNM时,位单元210的状态可以改变并且存储的数据丢失。因此,SNM越小,位单元210越不稳定。如图3B所示,两个电压转移曲线(VTC)330b对应于保持操作中的SRAM(即,WL信号320为逻辑低且WL信号320不具有WL假信号)。两个VTC 330b中的每一个对应于如上所述的两个交叉耦合的反相器之一。用于保持操作的SNM对应于噪声容限方块332b。具体而言,保持操作的SNM是以伏特为单位的噪声容限方块332b的边长。类似地,如图3B所示,两个电压转移曲线(VTC)330a对应于读取操作中的SRAM(即,WL信号320为逻辑高或当WL信号320具有WL假信号时)。两个VTC 330a中的每一个对应于如上所述的两个交叉耦合的反相器之一。用于读取操作的SNM对应于噪声容限方块332a。具体而言,保持操作的SNM是以伏特为单位的噪声容限方块332a的边长。用于读取操作的SNM小于用于保持操作的SNM,这意味着位单元210在读取操作期间比在保持操作期间更不稳定。

还如图4A所示,当WL电压增加时,SNM减小。随着WL电压增加,SNMv对WL电压曲线420a、420b和420c在加电持续时间422中显著下降。加电持续时间422是WL阈值电压424与VDD 314之间的WL电压范围。换句话说,当SRAM从保持操作(即,WL电压为逻辑低)转换到读取/写入操作(即,WL电压为逻辑高)(即,VDD 314)时,SNM减小。因此,在SRAM加电期间改变WL电压的性质是用于RNG目的的随机性的来源。

另一方面,如图3A所示,即使WL信号320打算为逻辑低(例如,0),也可能存在WL假信号(例如,WL假信号322)。当WL假信号322足够大(例如,大于WL阈值电压424)时,SNM显著下降(例如,从方块332b到方块332a)。换句话说,WL假信号322还使位单元210由于小SNM而不稳定。因此,在SRAM加电期间WL假信号322的存在也是用于RNG目的的随机性的来源。

另外,如图4B所示,当BL电压增加时,SNM增加。具体而言,当BL电压相对较低时,SNM相对较小(即,位单元210相对不稳定)。当BL电压增加超过BL阈值电压416时,SNM相对大(即,位单元210相对不稳定)并且不显著增加。换言之,SNM v.BL电压曲线410具有两个范围:不稳定范围412和稳定范围414。不稳定范围412是来自Vth 312和BL阈值电压416的BL电压范围。在一个实施例中,BL阈值电压416是VDD 314的90%。在另一个实施例中,BL阈值电压416是VDD 314的85%。在又一实施例中,BL阈值电压416是VDD 314的80%。应当注意,BL阈值电压416的各种值在本发明的预期范围内。通过将BL/BLB信号310预充电到不稳定区域412中的值(即,Vth 312与BL阈值电压416之间的BL电压)而不是VDD 314,位单元210由于小SNM而不稳定。因此,将BL/BLB信号310预充电到不稳定区域412中的值是用于RNG目的的又一随机性源极。

图5示出了根据一些实施例的示例性SRAM加电RNG 500。图6示出了根据一些实施例的SRAM加电RNG 500的实例的时序图600的实例。如图5所示,示例性SRAM加电RNG 500包括控制电路102(其可以组合图1所示的存储器控制器102和RNG控制器104),字线驱动器520、位线驱动器510、单元阵列200、第一箝位晶体管522、第二箝位晶体管526、第一延迟电路524、第二延迟电路528、关断(SD)信号504、头部开关506和泄漏晶体管508。SRAM加电RNG500可以包括图5中未示出的其它部件,在一些实施例中,仅包括第一延迟电路524或第二延迟电路258和第一箝位晶体管522或第二箝位晶体管526之一。在实例实施例中,SRAM加电RNG 500可以是集成电路(IC)芯片的一部分。

控制电路102生成地址解码信号DEC。字线驱动器520接收解码信号DEC并生成字线信号WL,该字线信号WL输出到阵列200的选定字线220。另一方面,控制电路102生成另一地址解码信号DEC(BL)。位线驱动器510接收解码信号DEC(BL)并生成输出到阵列200的选定位线对的位线信号BL。单元阵列200接收字线信号WL和位线信号BL,这反过来又控制单元阵列200的操作。

通过第一延迟电路524将关断信号SD 504馈送到第一箝位晶体管522的门。第一箝位晶体管522的漏极连接到地面,而第一箝位晶体管522的源极连接到字线驱动器520。在所示的实例中,还通过第二延迟电路528将关断信号SD 504馈送到第二箝位晶体管526的门。第二箝位晶体管526的漏极连接到地面,而第二箝位晶体管526的源极连接到单元阵列200。在一个实施例中,第一箝位晶体管522和第二箝位晶体管526是NMOS晶体管。应当注意,各种箝位晶体管或电路在本发明的预期范围内。在一个实施例中,第一延迟电路524或者可选地第二延迟电路528具有两个或多个串联连接的反相器。应当注意,各种延迟电路在本发明的预期范围内。

关断信号SD 504还被馈送到头部开关506的门和泄漏晶体管508的门。在一个实施例中,头部开关506是PMOS晶体管。在一个实施例中,泄漏晶体管508是NMOS晶体管。头部开关506的源极连接到VDD 314(逻辑外围电源电压),并且头部开关506的漏极连接到单元阵列200(即,具有电压VDDA 240)。泄漏晶体管508的源极连接到单元阵列200(即,具有电压VDDA 240的同频,且泄漏晶体管508的漏极连接到地面)。下面将详细描述泄漏晶体管508的操作。

如图6所示,关断信号SD 504在时间t1601之前为逻辑高(1)。在一个实施例中,关断信号SD 504被馈送到头部开关506的门,并且头部开关506是PMOS晶体管。因此,当关断信号SD 504为逻辑高(1)时,头部开关506关断。因此,电压VDDA 240(即,单元阵列200中的每个位单元210的电源电压)不被上拉到VDD 314。换句话说,位单元210在时间t1601之前没有被唤醒。在时间t1601,关断信号SD 504从逻辑高(1)切换到逻辑低(0)。同样,关断信号SD504被馈送到头部开关506的门,并且在一个实施例中头部开关506是PMOS晶体管。因此,当关断信号SD504为逻辑低(0)时,头部开关506接通。因此,电压VDDA 240(即,用于单元阵列200中的每个位单元210的电源电压)被拉高至VDD。换句话说,位单元210响应于关断信号504在加电阶段中在时间t1601之后开始唤醒。在时间t1601之后的RNG阶段612期间,SRAM加电RNG 500会在RNG阶段中操作,接着是SRAM操作阶段614具体而言,在RNG操作阶段612期间,信号BL/BLB 310处于非稳定区域412中的值(即,Vth 312和BL阈值电压416之间的BL电压)而不是VDD 314,这样,位线在非稳定区域412中被预充电到低于VDD的值。WL信号320通常保持在逻辑低(0)(下面还讨论),并且SRAM加电RNG 500作为RNG操作(即,生成不稳定位112)。在SRAM操作阶段614期间,信号BL/BLB310上升到VDD 314,并且SRAM加电RNG 500作为SRAM操作(即,导通保持、读和写操作)。

在RNG操作阶段612期间,如上所述,SRAM加电RNG 500的位线信号BL被预充电到不稳定区域412中的值(即,Vth 312和BL阈值电压416之间的BL电压),而不是VDD 314。因此,位单元210由于对应于不稳定区域412的小SNM而不稳定。这样,将BL/BLB信号310预充电到不稳定区域412中的值改善了在RNG操作阶段612期间SRAM加电RNG 500的随机性。

此外,在RNG操作阶段612期间,在SRAM加电期间变化的WL电压的性质是随机性的来源,如上文所提及。在SRAM加电期间WL假信号322的存在也是随机性的来源,如上所述。在一个实施例中,关断信号SD504通过第一延迟电路524馈送到第一箝位晶体管522的门。因此,箝位晶体管522的门处的信号Clamp_DEC是关断信号SD 504的延迟。如图6所示,它们在关断信号SD 504和信号Clamp_DEC之间的延迟由延迟周期602定义。当信号Clamp_DEC为逻辑高(1)时,在一个实施例中为NMOS晶体管的第一箝位晶体管522被接通,从而将信号DEC下拉到地面。在一些实例中,延迟602是可变的(即,每当SRAM加电RNG 500被加电时改变)。此操作可启动WL假信号322。换句话说,第一箝位晶体管522在延迟周期602内保持断开,而Clamp_WL信号转变不被延迟(或延迟较少),因此第二箝位晶体管526在第一箝位晶体管522之前接通。以这种方式,延迟周期602引入了潜在WL假信号322的影响,从而改善了在RNG操作阶段612期间SRAM加电RNG 500的随机性。在一些实施例中,延迟周期602是变化的。例如,在一个实施例中,可变延迟602对于当前加电可以是零。在另一个实施例中,可变延迟602可以是当前加电的延迟602的30%,如图6所示。在又一个实施例中,可变延迟602可以是当前加电的延迟602的80%,如图6所示。

类似地,在另一实施例中,关断信号SD 504通过第二延迟电路528馈送到第二箝位晶体管526的门。信号Clamp_WL和WL信号320的操作与信号Clamp_DEC和解码信号DEC的操作相同,为了简单起见不再重复。

此外,如上所述,当关断信号SD 504为逻辑高(1)时,头部开关506关断。然而,在没有泄漏晶体管508的情况下,电压VDDA 240(即,单元阵列200中的每个位单元210的电源电压)由于头部开关506的尺寸和泄漏而没有被完全拉到地面(即,不处于零伏)。这可能导致在关断阶段期间(即,当关断信号SD 504为逻辑高(1)时)将电压施加到单元阵列200中的位单元210,这可能使得一些位单元开始被偏置为逻辑高(1)或逻辑低(0),从而降低SRAM加电RNG 500的随机性

相反,利用泄漏晶体管508,电压VDDA 240被拉得非常接近零。具体而言,在一个实施例中,泄漏晶体管508是NMOS晶体管。当关断信号SD 504为逻辑高(1)时,泄漏晶体管508被接通,从而将电压VDDA 240下拉到地面。泄漏晶体管508的饱和电流Isat被选择为头部开关506的泄漏电流。换句话说,泄漏晶体管508提供额外路径以使头部开关506的泄漏电流流出。以此方式,通过将电压VDDA 240降低到非常接近零,存在较少初始偏置的位单元数据,从而改进SRAM加电RNG 500的随机性。

图7A-图7C示出根据一些实施例的SRAM加电RNG 500的随机性和断电/上电循环之间的示例性关系。具体而言,故障位图702、704、706示出了SRAM加电RNG 500的各种断电/加电循环的故障位的计数和地址的实例。图7A中的故障位图702示出了在单个电源回路之后SRAM加电RNG500的故障位的计数和地址的实例;图7B中的故障位图704示出了在一千个电源回路之后SRAM加电RNG 500的故障位的计数和地址的实例;而图7C中的故障位图706示出了在九千个电源回路之后SRAM加电RNG 500的故障位的计数和地址的实例。因此,在实现RNG 500之前循环器件功率可以改善RNG的随机性。

图8是根据一些实施例的用于操作SRAM加电RNG的示例性方法800的流程图。在步骤802中,接收关断信号SD。响应于关断信号的第一状态(即,逻辑低状态),在步骤804中将第一电压电平414施加到存储器阵列200。如上所述,存储器单元阵列200的实例具有耦合到多个位线和多个字线的多个位单元210。在步骤806中,在随机数发生器(RNG)阶段612期间将位线预充电到低于第一电压电平的第二电压电平412。此外,在一些实施例中,在步骤808中的RNG阶段期间启动字线假信号。在步骤810中,在RNG阶段期间确定位单元的初始状态以生成随机数。在步骤812中,在多个位线中之一上输出初始状态。在步骤814中,将初始状态应用于诸如安全、密码学、计算机模拟、统计采样、完全随机化设计、游戏和博彩等应用。

因此,所公开的实施例包括存储器器件和存储器单元阵列,该存储器器件具有多个位线、多个字线,并且该存储器单元阵列包括耦合到位线和字线的多个位单元。位单元中的每一个配置为在位线上呈现初始逻辑状态。电源端子耦合到存储器单元阵列。控制器耦合到字线和位线,并且配置为在RNG阶段期间将位线预充电到低于第一电压电平的第二电压电平,并且确定多个位单元的初始逻辑状态以生成随机数。第一电压电平是用于在SRAM阶段期间操作存储器单元阵列的电压电平。

根据其它实施例,RNG包括具有耦合到多个位线和多个字线的多个位单元的存储器单元阵列。每个位单元包括多个晶体管并且配置为当RNG加电时呈现初始逻辑状态并且在位线上输出该初始逻辑状态。电源端子耦合到存储器单元阵列且配置为将第一电压电平提供到存储器单元阵列。输入端子配置为接收关断信号。头部开关连接在电源端子和存储器单元阵列之间,并响应于关断信号。字线驱动器耦合到单元阵列,并配置为将字线信号输出到存储器单元阵列。延迟电路连接在输入端子和字线驱动器之间,并且配置为响应于关断信号延迟字线信号到字线驱动器的输出,使得在存储器阵列接收字线信号之前由头部开关接收关断信号。

根据另外的实施例,方法包括接收关断信号,并且响应于关断信号的第一状态,将第一电压电平施加到存储器阵列。存储器单元阵列具有耦合到多个位线和多个字线的多个位单元。在RNG阶段期间将位线预充电到低于第一电压电平的第二电压电平。在RNG阶段期间启动字线假信号。在RNG阶段期间确定位单元的初始状态。

在一些实施例中,提供了一种存储器器件,包括:多个位线;多个字线;存储器单元阵列,包括耦合到位线和字线的多个位单元,位单元中的每一个配置为在位线上呈现初始逻辑状态;电源端子,耦合到存储器单元阵列;以及控制器,耦合到字线和位线,控制器配置为:在随机数发生器阶段期间,将位线预充电到低于第一电压电平的第二电压电平,并且确定多个位单元的初始逻辑状态以生成随机数,第一电压电平是用于在SRAM阶段期间操作存储器单元阵列的电压电平。

在上述存储器器件中,包括:地址解码器,配置为输出存储器地址信号;字线驱动器,配置为接收存储器地址信号并输出字线信号;输入端子,配置为接收关断信号;以及头部开关,连接在第一电压电平与存储器单元阵列之间,其中,头部开关配置为响应于关断信号的第一状态而关断。

在上述存储器器件中,包括:泄漏晶体管,连接在头部开关和接地电压电平之间,其中,泄漏晶体管配置为响应于关断信号的第一状态而被接通。

在上述存储器器件中,包括:第一延迟电路,耦合到输入端子并且配置为将关断信号延迟第一延迟周期;以及第一箝位晶体管,耦合到第一延迟电路并且配置为响应于延迟第一延迟周期的关断信号而将存储器地址信号拉至接地电压电平。

在上述存储器器件中,包括:第二箝位晶体管,配置为响应于关断信号而将字线信号拉至接地电压电平。

在上述存储器器件中,还包括第二延迟电路,第二延迟电路耦合到输入端子并且配置为将关断信号延迟第二延迟周期;以及其中,第二箝位开关配置为响应于延迟第二延迟周期的延迟关断信号而将字线信号拉至接地电压电平。

在上述存储器器件中,第一延迟周期不同于第二延迟周期。在上述存储器器件中,控制器配置为在接收到关断信号之前以预定数量的循环对存储器单元阵列进行加电和断电。

在一些实施例中,提供了一种随机数发生器,包括:存储器单元阵列,具有耦合到多个位线和多个字线的多个位单元,每个位单元包括多个晶体管并且配置为当随机数发生器加电时呈现初始逻辑状态并且在位线上输出初始逻辑状态;电源端子,耦合到存储器单元阵列并且配置为将第一电压电平提供到存储器单元阵列;输入端子,配置为接收关断信号;头部开关,连接在电源端子和存储器单元阵列之间,头部开关响应于关断信号;字线驱动器,耦合到单元阵列,单元阵列配置为将字线信号输出到存储器单元阵列;以及延迟电路,连接在输入端子和字线驱动器之间,并且配置为响应于关断信号延迟字线信号到字线驱动器的输出,使得在字线信号被存储器阵列接收之前由头部开关接收关断信号。

在上述随机数发生器中,还包括:位线驱动器,耦合到单元阵列;以及控制电路,耦合到字线驱动器和位线驱动器,并且配置为控制位线驱动器将多个位线预充电到低于第一电压电平的第二电压电平。在上述随机数发生器中,第二电压电平高于多个晶体管的阈值电压。

在上述随机数发生器中,还包括连接在头部开关和接地电压端子之间的泄漏晶体管,其中,泄漏晶体管配置为响应于关断信号而被接通。在上述随机数发生器中,延迟电路包括箝位晶体管,箝位晶体管耦合到延迟电路并且配置为响应于关断信号将字线信号拉到接地电压电平。

在上述随机数发生器中,头部开关是PMOS晶体管,泄漏晶体管是NMOS晶体管。

在上述随机数发生器中,控制电路配置为在接收到关断信号之前以预定数量的循环对存储器单元阵列进行加电和断电。

在一些实施例中,提供了一种操作随机数发生器的方法,包括:接收关断信号;响应于关断信号,将第一电压电平施加到存储器阵列,存储器单元阵列具有耦合到多个位线和多个字线的多个位单元;在随机数发生器阶段期间将位线预充电到低于第一电压电平的第二电压电平;在随机数发生器阶段期间发起字线假信号;以及在随机数发生器阶段期间确定位单元的初始状态。

在上述方法中,在随机数发生器阶段期间确定位单元的初始状态发生在存储器单元阵列加电到第一电压电平之前。

在上述方法中,启动字线假信号包括:在第一时间点将关断信号施加到头部开关,头部开关配置为响应于关断信号而将第一电压电平施加到存储器单元阵列;在第一时间点将关断信号施加到第一箝位开关以将地址解码信号保持在第一信号电平;在晚于第一时间点的第二时间点将关断信号施加到第二箝位开关,以将字线信号保持在第一信号电平。

在上述方法中,还包括:响应于关断信号为头部开关提供接地路径。在上述方法中,还包括:在接收关断信号之前以预定数量的循环将存储器单元阵列进行加电和断电。

上面概述了若干实施例的特征,使得本领域技术人员可以更好地理解本发明的方面。本领域技术人员应该理解,它们可以容易地使用本发明作为基础来设计或修改用于实施与本文所介绍实施例相同的目的和/或实现相同优势的其它工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,本文中它们可以做出多种变化、替换以及改变。

- 存储器器件、随机数发生器及其操作方法

- 电压发生器、半导体存储器件及其操作方法