高压驱动电路及功率模块

文献发布时间:2023-06-19 12:11:54

技术领域

本发明涉及集成电路驱动控制的技术领域,特别地,涉及一种高压驱动电路及功率模块。

背景技术

IPM(Intelligent Power Module,智能功率模块)是一种新型的大功率电力电子器件,具有高电流密度、低饱和电压和耐高压等优点,目前广泛应用在空调、洗衣机、风扇等各种领域。IPM模块包括至少两相半桥驱动电路,每相半桥驱动电路中通常至少包括高压驱动单元、低压驱动单元以及功率器件。

目前的IPM,通过MCU(Microcontroller Unit,微控制单元)控制且提供输入信号,进而实现对IPM模块中所有相半桥驱动电路的控制,以达到驱动电机的目的。其中,IPM模块中的高压驱动单元和低压驱动单元用于将接收到的输入信号转换为功率器件所需的驱动信号。在实际应用中,观察到提供至其中一相半桥驱动电路中的高侧输入信号在整机掉电之后会忽然出现误触发脉冲,且该误触发脉冲的电压大于该相半桥驱动电路中的高压驱动单元的开启电压,进而会导致对应的功率器件误启动,进而造成IPM模块工作混乱,容易损坏内部的功率器件。

发明内容

鉴于上述问题,本发明的目的在于提供一种高压驱动电路及功率模块,显著降低了掉电后功率器件失效损坏的几率,从而进一步提高了功率模块的可靠性。

根据本发明的一方面,提供一种高压驱动电路,包括:

第一检测模块,根据电源电压和第一阈值生成第一检测信号,检测电源电压是否欠压;

第二检测模块,根据悬浮供电电压和第二阈值生成第二检测信号,检测悬浮供电电压是否欠压;

脉冲产生模块,连接所述第一检测模块,基于所述第一检测信号生成第一脉冲控制信号;

复位模块,连接所述脉冲产生模块以及所述第二检测模块,基于所述第二检测信号和所述第一脉冲控制信号生成复位信号,

高压驱动单元,连接所述复位模块,根据所述复位信号指示是否复位所述高压驱动单元输出的驱动信号。

可选地,所述脉冲产生模块对所述第一检测信号的上升沿进行检测产生所述第一脉冲控制信号。

可选地,所述第一脉冲控制信号为有效电平状态或者所述第二检测信号为无效电平状态时输出复位信号,所述复位信号指示复位所述高压驱动单元输出的驱动信号;否则,所述高压驱动单元正常输出驱动信号。

可选地,所述脉冲产生模块还接收输入信号,并基于所述第一检测信号开启或者关闭对所述输入信号的输入响应。

可选地,所述第一检测信号控制所述脉冲产生模块开启对所述输入信号的输入响应时,所述脉冲产生模块根据所述输入信号分别生成第二脉冲信号以及第三脉冲信号;所述第一检测信号控制所述脉冲产生模块关闭对所述输入信号的输入响应时,所述脉冲产生模块根据所述第一检测信号生成第二脉冲信号。

可选地,所述第一检测信号的电平状态由无效电平状态变为有效电平状态时,产生所述第二脉冲信号,进而控制所述复位模块生成所述复位信号;所述第一检测信号的电平状态为无效电平状态下开启输入响应,并基于所述输入信号产生所述第二脉冲信号和所述第三脉冲信号。

可选的,还包括:

第一信号处理模块,接收高侧输入信号,对所述高侧输入信号处理并产生所述输入信号提供至所述脉冲产生模块。

可选地,当所述电源电压低于所述第一阈值且延时持续一段预定时间,所述第一检测信号为有效电平状态,否则,所述第一检测信号为无效电平状态。

可选地,所述悬浮供电电压低于所述第二阈值且延时持续一段预定时间,所述第二检测信号为无效电平状态,否则,所述第二检测信号为有效电平状态。

可选地,所述无效电平状态为低电平状态,所述有效电平状态为高电平状态。

可选地,所述第二检测模块包括:

第一采样比较单元,采集所述悬浮供电电压,并与所述第二阈值比较输出第一比较信号;以及

第一运算单元,包括第一延时器和第一非门,将所述第一比较信号延时处理以及逻辑运算以输出所述第二检测信号。

可选地,所述第一检测模块包括:

电压检测单元,用于采集电源电压,并判断电源电压是否高于所述第一阈值且持续了预定时间,并输出表征检测结果的中间检测信号;以及

保持单元,基于所述中间检测信号,在所述电源电压不高于第一阈值且持续了一段时间的情况下输出电平状态变为有效电平状态的所述第一检测信号。

可选地,所述电压检测单元包括:

第二采样比较单元,采集所述电源电压,并与所述第一阈值比较输出第二比较信号;以及

第二运算单元,包括第二延时器和第一恒等门,将所述第二比较信号延时处理以及逻辑运算以输出所述中间检测信号,

其中,所述一段时间大于所述预定时间。

可选地,所述保持单元中还包括:

计数刷新单元,将所述中间检测信号处理后提供至所述保持单元,包括:

振荡器,第一端与电压检测单元连接以接收所述中间检测信号;

四输入与门,输出端与所述保持单元连接;

第一触发器,第一输入端分别与所述振荡器的第二端、所述四输入与门的第一输入端连接,第二输入端与第一触发器的输出端连接;

第二触发器,第一输入端分别与所述第一触发器的输出端、所述四输入与门的第二输入端连接,第二输入端与第二触发器的输出端连接;以及

第三触发器,第一输入端分别与所述第二触发器的输出端、所述四输入与门的第三输入端连接,第二输入端与第三触发器的输出端以及所述四输入与门的第四输入端连接。

可选地,所述脉冲产生模块包括:

第一边沿产生单元,输入端与所述第一检测模块连接以接收所述第一检测信号,输出端输出所述第一脉冲控制信号,所述第一边沿产生单元在所述第一检测信号从无效电平状态变为有效电平状态的情况下产生脉冲。

可选地,所述复位模块包括:

电平转换单元,与所述脉冲产生模块连接以接收所述第一脉冲控制信号,并将所述第一脉冲控制信号电平翻转以生成中间脉冲信号;

第三与非门,第一输入端与所述电平转换单元连接以接收所述中间脉冲信号,第二输入端与所述第二检测模块连接以接收所述第二检测信号,输出端输出所述复位信号。

可选地,所述脉冲产生模块还包括:

第一或非门,第一输入端与所述第一检测模块连接以接收所述第一检测信号;

第四非门,输入端与所述第一或非门连接;

第二或非门,第一输入端接收所述输入信号,第二输入端与所述第一或非门的输出端连接,输出端与所述第一或非门的第二输入端连接;

第二边沿产生单元,输入端与所述第四非门的输出端连接,输出端提供所述第二脉冲信号;

第三边沿产生单元,输入端与所述第一或非门的输出端连接,输出端提供所述第三脉冲信号。

可选地,还包括:

第一信号处理模块,接收低侧输入信号和高侧输入信号,并对低侧输入信号处理后传输至低压驱动单元,将高侧输入信号处理后提供至脉冲产生模块;以及

低压驱动单元,连接所述第一信号处理模块,根据所述第一信号处理模块输出的信号输出驱动信号。

可选地,所述第一信号处理模块包括:

滤波处理单元,将所述低侧输入信号滤波处理,以及将所述高侧输入信号滤波处理后传输至所述脉冲产生模块;

延时匹配单元,连接所述滤波处理单元,将滤波处理后的低侧输入信号进行延时处理并传输至低压驱动单元。

根据本申请的另一方面,提供一种功率模块,包括:

高侧功率管;以及

高压驱动电路,包括

第一检测模块,根据电源电压和第一阈值生成第一检测信号,检测电源电压是否欠压;

第二检测模块,根据悬浮供电电压和第二阈值生成第二检测信号,检测悬浮供电电压是否欠压;

脉冲产生模块,连接所述第一检测模块,基于所述第一检测信号生成第一脉冲控制信号;

复位模块,连接所述脉冲产生模块以及所述第二检测模块,基于所述第二检测信号和所述第一脉冲控制信号生成复位信号,

高压驱动单元,连接所述复位模块,根据所述复位信号指示是否复位所述高压驱动单元输出的驱动信号,

所述高压驱动单元连接所述高侧功率管以提供驱动信号。

可选地,所述脉冲产生模块对所述第一检测信号的上升沿进行检测产生所述第一脉冲控制信号。

可选地,所述第一脉冲控制信号为有效电平状态或者所述第二检测信号为无效电平状态时输出复位信号,所述复位信号指示复位所述高压驱动单元输出的驱动信号;否则,所述高压驱动单元正常输出驱动信号。

可选地,所述脉冲产生模块还接收输入信号,并基于所述第一检测信号开启或者关闭对所述输入信号的输入响应。

可选地,所述第一检测信号控制所述脉冲产生模块开启对所述输入信号的输入响应时,所述脉冲产生模块根据所述输入信号分别生成第二脉冲信号以及第三脉冲信号;所述第一检测信号控制所述脉冲产生模块关闭对所述输入信号的输入响应时,所述脉冲产生模块根据所述第一检测信号生成第二脉冲信号。

可选地,所述第一检测信号的电平状态由无效电平状态变为有效电平状态时,产生所述第二脉冲信号,进而控制所述复位模块生成所述复位信号;所述第一检测信号的电平状态为无效电平状态下开启输入响应,并基于所述输入信号产生所述第二脉冲信号和所述第三脉冲信号。

可选的,还包括:

第一信号处理模块,接收高侧输入信号,对所述高侧输入信号处理并产生所述输入信号提供至所述脉冲产生模块。

可选地,当所述电源电压低于所述第一阈值且延时持续一段预定时间,所述第一检测信号为有效电平状态,否则,所述第一检测信号为无效电平状态。

可选地,所述悬浮供电电压低于所述第二阈值且延时持续一段预定时间,所述第二检测信号为无效电平状态,否则,所述第二检测信号为有效电平状态。

可选地,所述无效电平状态为低电平状态,所述有效电平状态为高电平状态。

可选地,所述第二检测模块包括:

第一采样比较单元,采集所述悬浮供电电压,并与所述第二阈值比较输出第一比较信号;以及

第一运算单元,包括第一延时器和第一非门,将所述第一比较信号延时处理以及逻辑运算以输出所述第二检测信号。

可选地,所述第一检测模块包括:

电压检测单元,用于采集电源电压,和判断电源电压是否高于所述第一阈值且持续了预定时间,并输出表征检测结果的中间检测信号;以及

保持单元,基于所述中间检测信号,在所述电源电压不高于第一阈值且持续了一段时间的情况下输出电平状态变为有效电平状态的所述第一检测信号。

可选地,所述电压检测单元包括:

第二采样比较单元,采集所述电源电压,并与所述第一阈值比较输出第二比较信号;以及

第二运算单元,包括第二延时器和第一恒等门,将所述第二比较信号延时处理以及逻辑运算以输出所述中间检测信号,

其中,所述一段时间大于所述预定时间。

可选地,所述保持单元中还包括:

计数刷新单元,将所述中间检测信号处理后提供至所述保持单元,包括:

振荡器,第一端与电压检测单元连接以接收所述中间检测信号;

四输入与门,输出端与所述保持单元连接;

第一触发器,第一输入端分别与所述振荡器的第二端、所述四输入与门的第一输入端连接,第二输入端与第一触发器的输出端连接;

第二触发器,第一输入端分别与所述第一触发器的输出端、所述四输入与门的第二输入端连接,第二输入端与第二触发器的输出端连接;以及

第三触发器,第一输入端分别与所述第二触发器的输出端、所述四输入与门的第三输入端连接,第二输入端与第三触发器的输出端以及所述四输入与门的第四输入端连接。

可选地,所述脉冲产生模块包括:

第一边沿产生单元,输入端与所述第一检测模块连接以接收所述第一检测信号,输出端输出所述第一脉冲控制信号,所述第一边沿产生单元在所述第一检测信号从无效电平状态变为有效电平状态的情况下产生脉冲。

可选地,所述复位模块包括:

电平转换单元,与所述脉冲产生模块连接以接收所述第一脉冲控制信号,并将所述第一脉冲控制信号电平翻转以生成中间脉冲信号;

第三与非门,第一输入端与所述电平转换单元连接以接收所述中间脉冲信号,第二输入端与所述第二检测模块连接以接收所述第二检测信号,输出端提供所述复位信号。

可选地,所述脉冲产生模块还包括:

第一或非门,第一输入端与所述第一检测模块连接以接收所述第一检测信号;

第四非门,输入端与所述第一或非门连接;

第二或非门,第一输入端接收所述输入信号,第二输入端与所述第一或非门的输出端连接,输出端与所述第一或非门的第二输入端连接;

第二边沿产生单元,输入端与所述第四非门的输出端连接,输出端提供所述第二脉冲信号;

第三边沿产生单元,输入端与所述第一或非门的输出端连接,输出端提供所述第三脉冲信号。

可选地,还包括:

低侧功率管;

第一信号处理模块,接收低侧输入信号和高侧输入信号,并对低侧输入信号处理后传输至低压驱动单元,将高侧输入信号处理后提供至脉冲产生模块;以及

低压驱动单元,连接所述第一信号处理模块,根据所述第一信号处理模块输出的信号输出驱动信号,

所述低压驱动单元连接所述低侧功率管以提供驱动信号。

可选地,所述第一信号处理模块包括:

滤波处理单元,将所述低侧输入信号滤波处理,以及将所述高侧输入信号滤波处理后传输至所述脉冲产生模块;

延时匹配单元,连接所述滤波处理单元,将滤波处理后的低侧输入信号进行延时处理并传输至低压驱动单元。

本发明提供的高压驱动电路及功率模块,功率模块中设置有该高压驱动电路,可以在整机掉电之后出现误触发脉冲的情况下复位高压驱动单元输出的驱动信号,进而避免对应的功率器件误启动,显著降低了掉电后功率器件失效损坏的几率,从而进一步提高了功率模块的可靠性。进一步地,高压驱动电路中设置有第一检测模块和第二检测模块用于检测电源电压和悬浮供电电压,并通过脉冲产生模块和复位模块,基于对电源电压和悬浮供电电压的检测结果输出复位信号至高压驱动单元,复位信号用于指示是否复位高压驱动单元输出的驱动信号。

更进一步地,高压驱动电路还基于电源电压的检测结果以及输入信号产生脉冲信号,用于指示高压驱动单元开启或者关闭输入响应功能。也即,高压驱动电路基于检测结果以及输入信号同时控制后端的高压驱动单元的复位功能和输入响应功能,从而达到提高功率模块可靠性的作用。

附图说明

通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

图1示出了一种功率系统的结构示意图;

图2示出了一种功率系统中输入信号的波形示意图;

图3示出了一种功率系统中U相驱动电路的波形示意图;

图4示出了根据本发明实施例提供的功率模块的结构示意图;

图5示出了根据本发明实施例提供的功率模块中第二检测模块的电路示意图;

图6示出了根据本发明实施例提供的功率模块中电压检测单元的电路示意图;

图7示出了根据本发明实施例提供的功率模块中的一种保持单元的电路示意图;

图8示出了根据本发明实施例提供的功率模块中的另一种保持单元的电路示意图;

图9示出了根据本发明实施例提供的功率模块中的脉冲产生模块的电路示意图;

图10示出了根据本发明实施例提供的功率模块生成复位信号的时序示意图;

图11a示出了根据本发明实施例提供的功率模块生成第二脉冲信号及第三脉冲信号的一种时序示意图;

图11b示出了根据本发明实施例提供的功率模块生成第二脉冲信号及第三脉冲信号的另一种时序示意图。

具体实施方式

以下将参照附图更详细地描述本发明的各种实施例。在各个附图中,相同的元件采用相同或类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。

图1示出了一种功率系统的结构示意图,图2示出了一种功率系统中输入信号的波形示意图,图3示出了一种功率系统中U相驱动电路的波形示意图。

如图1所示,功率系统包括功率模块100、微控制器200以及负载300。其中,本实施例中的负载300以电机M为例,功率模块100例如为一种包含三相半桥驱动电路的智能功率模块,微控制器200例如为MCU。

微控制器200提供输入信号,其中,输入信号包括U相高侧输入信号HinU、V相高侧输入信号HinV、W相高侧输入信号HinW、W相低侧输入信号LinW、V相低侧输入信号LinV、U相低侧输入信号LinU。

功率模块100包括U相半桥驱动电路、V相半桥驱动电路以及W相半桥驱动电路,每相半桥驱动电路包括栅极驱动芯片、一高侧功率管和一低侧功率管,其中栅极驱动芯片中集成了高压驱动单元和低压驱动单元。进一步地,U相半桥驱动电路包括第一栅极驱动芯片110、第一高侧功率管Q11和第一低侧功率管Q21。V相半桥驱动电路包括第二栅极驱动芯片120、第二高侧功率管Q12和第二低侧功率管Q22。W相半桥驱动电路包括第三栅极驱动芯片130、第三高侧功率管Q13和第三低侧功率管Q23。其中,第一栅极驱动芯片110、第二栅极驱动芯片120、第三栅极驱动芯片130完全相同。其中每个栅极驱动芯片中还集成有故障报警模块等功能模块,本文中对上述集成的功能模块不做详细描述。

第一栅极驱动芯片110、第二栅极驱动芯片120、第三栅极驱动芯片130的内部连接关系和管脚布局相同,其管脚名称和描述如下表所示。

表1.智能功率模块中栅极驱动芯片的管脚名称及其描述

其中,在功率模块100的U相半桥驱动电路中,第一高侧功率管Q11的第一端作为U相半桥驱动电路的直流供电正端P。第一高侧功率管Q11的控制端与第一栅极驱动芯片110的高侧驱动信号输出端HO连接。第一高侧功率管Q11的第二端和第一低侧功率管Q21的第一端之间的中间节点作为功率模块100的U相输出端U以与负载300连接,且U相输出端U与第一栅极驱动芯片110中的高侧驱动悬浮供电地端VS连接。第一低侧功率管Q21的控制端与第一栅极驱动芯片110的低侧驱动信号输出端LO连接。第一低侧功率管Q21的第二端作为功率模块100的U相直流供电负端NU,U相直流供电负端NU与第一栅极驱动芯片110的信号地端COM连接并接地。第一栅极驱动芯片110的电源端VCC作为功率模块100的U相电源端接收电源电压Vcc,第一栅极驱动芯片110的高侧驱动悬浮供电端VB作为功率模块100的U相高侧驱动悬浮供电端,在第一栅极驱动芯片110中的电源端VCC与高侧驱动悬浮供电端VB之间连接有二极管(图中未示出),第一栅极驱动芯片110中的高侧驱动悬浮供电端VB与第一栅极驱动芯片110中的高侧驱动悬浮供电地端VS之间连接有自举电容(图中未示出)。第一栅极驱动芯片110的高侧信号输入端HIN作为功率模块100的U相高压信号输入端与微控制器200连接以接收U相高侧输入信号HinU。第一栅极驱动芯片110的低侧信号输入端LIN作为功率模块100的U相低压信号输入端与微控制器200连接以接收U相低侧输入信号LinU。

在功率模块100的V相半桥驱动电路中,第二高侧功率管Q12的第一端作为V相半桥驱动电路的直流供电正端P。第二高侧功率管Q12的控制端与第二栅极驱动芯片120的高侧驱动信号输出端HO连接。第二高侧功率管Q12的第二端和第二低侧功率管Q22的第一端之间的中间节点作为功率模块100的V相输出端V以与负载300连接,且V相输出端V与第二栅极驱动芯片120中的高侧驱动悬浮供电地端VS连接。第二低侧功率管Q22的控制端与第二栅极驱动芯片120的低侧驱动信号输出端LO连接。第二低侧功率管Q22的第二端作为功率模块100的V相直流供电负端NV,V相直流供电负端NV与第二栅极驱动芯片120的信号地端COM连接并接地。第二栅极驱动芯片120的电源端VCC作为功率模块100的V相电源端接收电源电压Vcc,第二栅极驱动芯片120的高侧驱动悬浮供电端VB作为功率模块100的V相高侧驱动悬浮供电端,在第二栅极驱动芯片120中的电源端VCC与高侧驱动悬浮供电端VB之间连接有二极管(图中未示出),第二栅极驱动芯片120中的高侧驱动悬浮供电端VB与第二栅极驱动芯片120中的高侧驱动悬浮供电地端VS之间连接有自举电容(图中未示出)。第二栅极驱动芯片120的高侧信号输入端HIN作为功率模块100的V相高压信号输入端与微控制器200连接以接收V相高侧输入信号HinV。第二栅极驱动芯片120的低侧信号输入端LIN作为功率模块100的V相低压信号输入端与微控制器200连接以接收V相低侧输入信号LinV。

在功率模块100的W相半桥驱动电路中,第三高侧功率管Q13的第一端作为W相半桥驱动电路的直流供电正端P。第三高侧功率管Q13的控制端与第三栅极驱动芯片130的高侧驱动信号输出端HO连接。第三高侧功率管Q13的第二端和第三低侧功率管Q23的第一端之间的中间节点作为功率模块100的W相输出端W以与负载300连接,且W相输出端W与第三栅极驱动芯片130中的高侧驱动悬浮供电地端VS连接。第三低侧功率管Q23的控制端与第三栅极驱动芯片130的低侧驱动信号输出端LO连接。第三低侧功率管Q23的第二端作为功率模块100的W相直流供电负端NW,W相直流供电负端NW与第三栅极驱动芯片130的信号地端COM连接并接地。第三栅极驱动芯片130的电源端VCC作为功率模块100的W相电源端接收电源电压Vcc,第三栅极驱动芯片130的高侧驱动悬浮供电端VB作为功率模块100的W相高侧驱动悬浮供电端,在第三栅极驱动芯片130中的电源端VCC与高侧驱动悬浮供电端VB之间连接有二极管(图中未示出),第三栅极驱动芯片130中的高侧驱动悬浮供电端VB与第三栅极驱动芯片130中的高侧驱动悬浮供电地端VS之间连接有自举电容(图中未示出)。第三栅极驱动芯片130的高侧信号输入端HIN作为功率模块100的W相高压信号输入端与微控制器200连接以接收W相高侧输入信号HinW。第三栅极驱动芯片130的低侧信号输入端LIN作为功率模块100的W相低压信号输入端与微控制器200连接以接收W相低侧输入信号LinW。

其中,第一栅极驱动芯片110、第二栅极驱动芯片120、以及第三栅极驱动芯片130的电源端VCC之间可以彼此连接以接收电源电压Vcc。U相半桥驱动电路的直流供电正端P、V相半桥驱动电路的直流供电正端P、以及W相半桥驱动电路的直流供电正端P例如在功率模块100内部连接并作为功率模块100的直流供电正端。

上述功率模块100用于将从微控制器200接收的输入信号转换为驱动信号提供至后端的负载300,进而驱动负载300。

如图2所示,上述功率系统在实际应用时,在T1时刻整机掉电,之后在T2时刻微控制器200停止信号输出,由微控制器200提供的六路输入信号正常关闭。但关闭之后由微控制器200提供至功率模块100的U相高压信号输入端的U相高侧输入信号HinU会出现一个大约持续4.7ms的误触发脉冲,且该误触发脉冲的电压大于第一栅极驱动芯片110中高压驱动单元的输入开启电压,进而会导致第一高侧功率管Q11误启动,造成功率模块100工作混乱,容易损坏内部的功率器件。

如图3所示,从T2时刻之后,电源电压Vcc处于持续掉电的状态,上述提供的功率模块100的各栅极驱动芯片的故障报警模块中集成有欠压保护电路,进而功率模块100具备欠压保护的功能。当各栅极驱动芯片的电源端VCC接收的电源电压Vcc,和高侧驱动悬浮供电端VB与高侧驱动悬浮供电地端VS之间的差值悬浮供电电压 Vbs低于一定的阈值时,欠压保护电路会自动关闭输出,一定程度上保护了功率模块100中的功率器件,此时电源电压Vcc低于阈值电压,功率模块100中的各低侧功率管关断。由于栅极驱动芯片中的高侧驱动悬浮供电端VB与高侧驱动悬浮供电地端VS之间连接有自举电容,自举电容的电压消耗缓慢,导致悬浮供电电压 Vbs基本稳定在15V左右,进而功率模块100中的栅极驱动芯片的高压驱动单元并未进入欠压保护模式。当图2中示出的U相高侧输入信号HinU的误触发脉冲上升沿到来时,电源电压Vcc约为4.4V,此时功率模块100中的对应相半桥驱动电路中的栅极驱动芯片的高压驱动单元响应该误触发脉冲,导致栅极驱动芯片中的高压驱动单元输出有效电平状态(高电平)的驱动信号VGEU,进而使得高侧功率管导通。相应地,该栅极驱动芯片中的高侧驱动悬浮供电地端VS处的悬浮地电压VsU和高侧驱动悬浮供电端VB的悬浮正电压 VbU抬升。大约4.7ms后误触发脉冲的下降沿到来,电源电压Vcc掉至2V左右,此时功率模块100中的第一栅极驱动芯片未响应U相高侧输入信号HinU中的误触发脉冲的下降沿,导致第一高侧功率管Q11一直处于导通状态,若此时再整机上电,会出现第一高侧功率管Q11、第一低侧功率管Q21直通的情况,进而损坏功率器件。

综上,当功率模块100整体掉电后,栅极驱动芯片中高压驱动单元未及时关闭输入信号响应或是未复位其输出的驱动信号,进而导致在掉电后U相高侧输入信号出现误触发脉冲时,功率模块100响应了该误触发脉冲的上升沿,导致高侧功率管一直处于导通的状态,出现失效损坏的情况。

本申请提供的功率模块,可以检测整机的工作状态进而判断是否会出现误触发脉冲,并在需要关闭输入响应或者复位输出的驱动信号的情况下控制对应的栅极驱动芯片中的高压驱动单元关闭输入响应或者复位其输出的驱动信号,进而防止功率模块中的功率器件因响应输入信号的误触发脉冲而失效。以下将结合附图对本申请提供的功率模块进行详细说明。

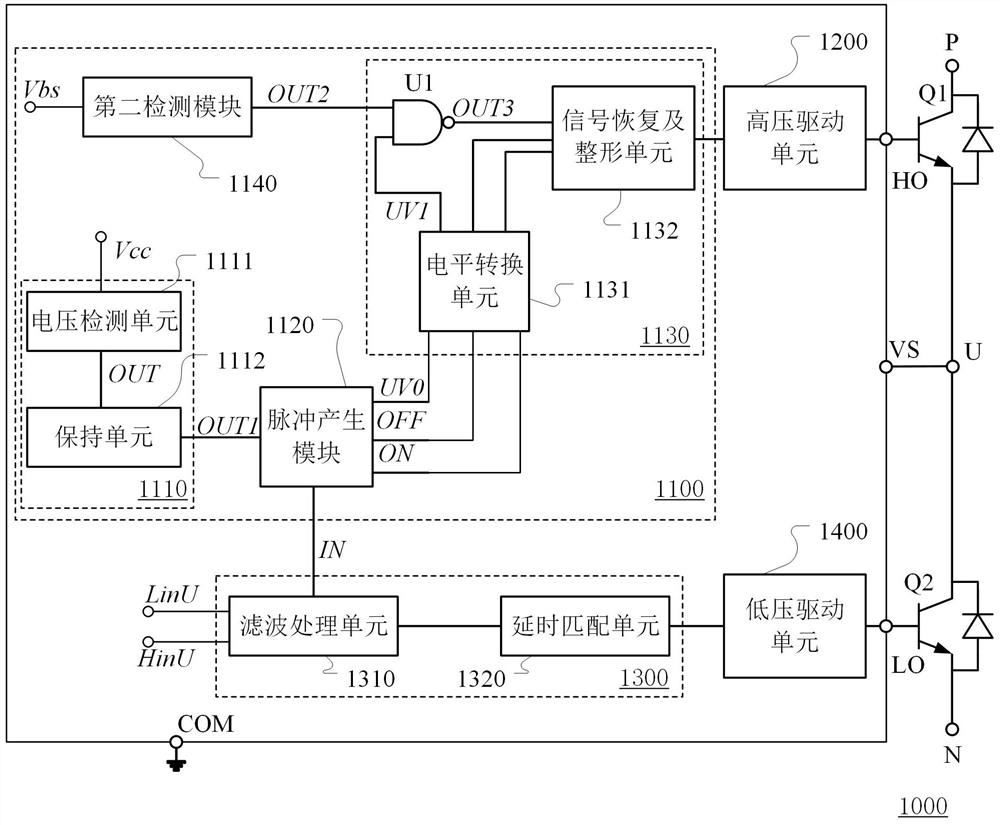

图4示出了根据本发明实施例提供的功率模块的结构示意图。

功率模块1000的其中一相半桥驱动电路如图4所示,该相半桥驱动电路以U相半桥驱动电路为例进行说明,但本申请的实施不以此为限,功率模块1000中的各相半桥驱动电路例如可以完全相同。

功率模块1000包括高压驱动电路1100、高压驱动单元1200、第一信号处理模块1300以及低压驱动单元1400、高侧功率管Q1(第一高侧功率管Q11)、低侧功率管Q2(第一低侧功率管Q21)。其中,高压驱动电路1100、高压驱动单元1200、第一信号处理模块1300以及低压驱动单元1400例如封装在一起组成栅极驱动芯片,本实施例提供的栅极驱动芯片相对于功率模块100中的各栅极驱动芯片,至少增加设置了高压驱动电路1100。

高压驱动电路1100连接高压驱动单元1200,用于检测本相半桥驱动电路中的电源电压Vcc和悬浮供电电压 Vbs,并基于检测结果控制高压驱动单元1200。高压驱动单元1200的输出端(高侧驱动信号输出端HO)连接高侧功率管Q1的控制端以提供驱动信号。高侧功率管Q1的第一端作为功率模块1000的直流供电正端P,高侧功率管Q1的第二端与低侧功率管Q2的第一端连接并作为功率模块1000的U相输出端U,且高侧功率管Q1的第二端与低侧功率管Q2的第一端连接并与U相半桥驱动电路中栅极驱动芯片的高侧驱动悬浮供电地端VS连接,低侧功率管Q2的第二端作为功率模块1000的U相直流供电负端N,低压驱动单元1400的输出端(低侧驱动信号输出端LO)连接低侧功率管Q2的控制端以提供驱动信号。U相半桥驱动电路中栅极驱动芯片的信号地端COM接地。

第一信号处理模块1300包括滤波处理单元1310和延时匹配单元1320。滤波处理单元1310分别接收U相低侧输入信号LinU以及U相高侧输入信号HinU,并将U相低侧输入信号LinU滤波处理后传输至延时匹配单元1320,以及将U相高侧输入信号HinU滤波处理后传输至高压驱动电路1100。延时匹配单元1320对滤波后的U相低侧输入信号LinU进行延时处理进而输出至低压驱动单元1400,低压驱动单元1400将处理后的U相低侧输入信号LinU进行转换进而得到驱动信号并输出至低侧功率管Q2的控制端。本实施例中的高压驱动单元1200和低压驱动单元1400采用现有的驱动电路即可实施,故此处不再赘述高压驱动单元1200和低压驱动单元1400的内部结构和工作原理相同。第一信号处理模块1300中的滤波处理单元1310例如为常见的滤波电路,延时匹配单元1320例如为常见的延时电路。

高压驱动电路1100包括第一检测模块1110、脉冲产生模块1120、复位模块1130以及第二检测模块1140。第一检测模块1110用于采集电源电压Vcc,和判断电源电压Vcc是否高于第一阈值Vref1且持续了预定时间并输出表征检测结果的第一检测信号OUT1。第二检测模块1140用于采集悬浮供电电压 Vbs,和判断悬浮供电电压 Vbs是否高于第二阈值Vref2且持续了预定时间并输出表征检测结果的第二检测信号OUT2。脉冲产生模块1120用于对第一检测信号OUT1的上升沿进行检测进而产生第一脉冲控制信号UV0。脉冲产生模块1120连接第一检测模块1110接收第一检测信号OUT1以及连接第一信号处理模块1300接收输入信号IN,基于第一检测信号OUT1生成第一脉冲控制信号UV0,并基于第一检测信号OUT1和输入信号IN生成第二脉冲信号OFF以及第三脉冲信号ON。其中,输入信号IN为第一信号处理模块1300中滤波处理单元1310将U相高侧输入信号HinU滤波处理后的信号。复位模块1130用于在第一脉冲控制信号UV0和第二检测信号OUT2均为有效电平状态或者均为无效电平时,产生的复位信号OUT3指示复位高压驱动单元1200输出的驱动信号;在第一脉冲控制信号UV0为无效电平状态且第二检测信号OUT2为有效电平状态,产生的复位信号OUT3指示高压驱动单元1200正常输出驱动信号。复位模块1130连接脉冲产生模块1120和第二检测模块1140,并基于第二检测信号OUT2和第一脉冲控制信号UV0生成复位信号OUT3,且用于向后端的高压驱动单元1200传输复位信号OUT3、第二脉冲信号OFF以及第三脉冲信号ON。其中,复位信号OUT3用于复位高压驱动单元1200输出的驱动信号,第二脉冲信号OFF以及第三脉冲信号ON用于在脉冲产生模块1120开启输入响应的情况下指示复位模块1130是否产生复位信号。

更进一步地,第一检测信号OUT1的电平状态由无效电平状态变为有效电平状态且第二检测信号OUT2为有效电平状态的情况下,复位信号OUT3指示复位高压驱动单元1200输出的驱动信号;第一检测信号OUT1的电平状态为其他情况且第二检测信号OUT2为无效电平状态的情况下,复位信号OUT3指示复位高压驱动单元1200输出的驱动信号;否则,复位信号OUT3指示高压驱动单元1200正常输出驱动信号。更进一步地,脉冲产生模块1120还接收输入信号IN,并基于第一检测信号OUT1开启或者关闭对输入信号IN的输入响应。第一检测信号OUT1控制脉冲产生模块1120开启对输入信号IN的输入响应时,脉冲产生模块1120根据输入信号IN生成第二脉冲信号OFF以及第三脉冲信号ON。具体地,在第一检测信号OUT1的电平状态为无效电平状态的情况下脉冲产生模块1120开启输入响应,并响应输入信号产生第二脉冲信号OFF和第三脉冲信号ON,以根据第二脉冲信号OFF控制复位模块1130生成复位信号,根据第三脉冲信号ON控制复位模块1130不生成复位信号。第一检测信号OUT1控制脉冲产生模块1120关闭对输入信号IN的输入响应时,脉冲产生模块1120根据第一检测信号OUT1生成第二脉冲信号OFF。具体地,脉冲产生模块1120在第一检测信号OUT1的电平状态由无效电平状态变为有效电平状态时控制脉冲产生模块1120关闭输入响应,产生第二脉冲信号OFF以控制复位模块1130生成复位信号。脉冲产生模块1120关闭对输入信号IN的输入响应之后,不产生第二脉冲信号OFF和第三脉冲信号ON。具体地,脉冲产生模块1120在第一检测信号OUT1的电平状态一直保持有效电平状态的情况下维持关闭输入响应,脉冲产生模块1120不产生第二脉冲信号OFF和第三脉冲信号ON。

其中,电源电压VCC低于第一阈值Vref1且持续一段预定时间,第一检测信号OUT1表征为有效电平状态,否则,第一检测信号OUT1表征为无效电平状态。其中,悬浮供电电压Vbs低于第二阈值Vref2且持续一段预定时间,第二检测信号OUT2表征为无效电平状态,否则,第二检测信号OUT2表征为有效电平状态。其中,无效电平状态例如为低电平状态,有效电平状态例如为高电平状态。

具体地,高压驱动电路1100用于检测电源电压Vcc和悬浮供电电压 Vbs,并对检测 结果运算和处理之后用于控制高压驱动单元1200,避免了高压驱动单元1200响应误触发脉 冲进而误启动造成功率器件损伤。高压驱动电路1100中第一检测信号OUT1表征电源电压 Vcc高于第一阈值Vref1,第二检测信号OUT2表征悬浮供电电压 Vbs高于第二阈值Vref2,则 表示功率模块1000处于工作模式下,在工作模式下高压驱动电路1100控制高压驱动单元 1200向高侧功率管Q1正常输出驱动信号。高压驱动电路1100中第一检测信号OUT1表征电源 电压Vcc不高于第一阈值Vref1,第二检测信号OUT2表征悬浮供电电压 Vbs高于第二阈值 Vref2,则表示功率模块1000处于风险模式下,在风险模式持续预定时间的情况下,高压驱 动电路1100控制复位高压驱动单元1200向高侧功率管Q1输出的驱动信号,且关闭脉冲产生 模块1120的输入响应。高压驱动电路1100中第一检测信号OUT1表征电源电压Vcc高于第一 阈值Vref1,第二检测信号OUT2表征悬浮供电电压 Vbs不高于第二阈值Vref2,则表示功率 模块1000处于高侧欠压保护模式下,在高侧欠压保护模式持续预定时间的情况下,高压驱 动电路1100控制复位高压驱动单元1200向高侧功率管Q1输出的驱动信号。高压驱动电路 1100中第一检测信号OUT1表征电源电压Vcc不高于第一阈值Vref1,第二检测信号OUT2表征 悬浮供电电压 Vbs不高于第二阈值Vref2,则表示功率模块1000处于欠压保护模式下,在欠 压保护模式持续预定时间的情况下,高压驱动电路1100控制复位高压驱动单元1200向高侧 功率管Q1输出的驱动信号,且关闭脉冲产生模块1120的输入响应。上述预定时间例如可以 设置为

更进一步地,图5示出了根据本发明实施例提供的功率模块中第二检测模块的电路示意图。如图5所示,第二检测模块1140包括第一采样比较单元1141和第一运算单元1142。第一采样比较单元1141用于将采集的悬浮供电电压 Vbs和第二阈值Vref2比较并输出第一比较信号。第一采样比较单元1141包括第一电阻R1、第二电阻R2、第三电阻R3以及第一比较器U2。第一电阻R1、第二电阻R2、第三电阻R3依次串联,第一电阻R1的第一端连接高侧驱动悬浮供电端VB,第一电阻R1的第二端与第二电阻R2的第一端连接的中间节点作为采样输出端与第一比较器U2的第一输入端连接,第二电阻R2的第二端与第三电阻R3的第一端连接,第三电阻R3的第二端连接高侧驱动悬浮供电地端VS。第一比较器U2的第二输入端接收第二阈值Vref2,第一比较器U2的输出端输出第一比较信号。第一运算单元1142用于将第一比较信号延时运算之后输出第二检测信号OUT2。第一运算单元1142包括第一延时器D1、第一非门U3和第一开关管Q3。第一延时器D1的输入端与第一比较器U2的输出端连接以接收第一比较信号,第一延时器D1的输出端连接第一非门U3的输入端,第一非门U3的输出端输出第二检测信号OUT2,第一开关管Q3的控制端与第一非门U3的输出端连接以接收第二检测信号OUT2,第一开关管Q3的第一端与第三电阻R3的第一端连接,第一开关管Q3的第二端与悬浮供电地端VS连接。其中,该实施例中第一比较器U2的第一输入端为负相输入端,第二输入端为正相输入端。当第一比较信号表征悬浮供电电压 Vbs不高于第二阈值Vref2,且第一比较信号通过第一延时器D1的持续时间大于预定时间的情况下,第二检测信号OUT2为低电平,否则第二检测信号OUT2为高电平。其中,第一开关管Q3例如为P型MOS管。

更进一步地,第一检测模块1110包括电压检测单元1111和保持单元1112。电压检测单元1111用于采集电源电压Vcc,和判断电源电压Vcc是否高于第一阈值Vref1且持续了预定时间,并输出表征检测结果的中间检测信号OUT。保持单元1112用于输出与中间检测信号OUT的电平状态保持一致的第一检测信号OUT1。图6示出了根据本发明实施例提供的功率模块的第一检测模块中电压检测单元的电路示意图,图7示出了根据本发明实施例提供的功率模块的第一检测模块中的一种保持单元的电路示意图。

如图6所示,电压检测单元1111包括第二采样比较单元11111和第二运算单元11112。第二采样比较单元11111用于将采集的电源电压Vcc和第一阈值Vref1比较并输出第二比较信号。第二采样比较单元11111包括第四电阻R4、第五电阻R5、第六电阻R6以及第二比较器U4。第四电阻R4、第五电阻R5、第六电阻R6依次串联,第四电阻R4的第一端接收电源电压Vcc,第四电阻R4的第二端与第五电阻R5的第一端连接的中间节点作为采样输出端与第二比较器U4的第一输入端连接,第五电阻R5的第二端与第六电阻R6的第一端连接,第六电阻R6的第二端接地。第二比较器U4的第二输入端接收第一阈值Vref1,第二比较器U4的输出端输出第二比较信号。第二运算单元11112用于将第二比较信号延时运算之后输出中间检测信号OUT。第二运算单元11112包括第二延时器D2、第一恒等门U5和第二开关管Q4。第二延时器D2的输入端与第二比较器U4的输出端连接以接收第二比较信号,第二延时器D2的输出端连接第一恒等门U5的输入端,第一恒等门U5的输出端输出中间检测信号OUT,第二开关管Q4的控制端与第一恒等门U5的输出端连接以接收中间检测信号OUT,第二开关管Q4的第一端与第六电阻R6的第一端连接,第二开关管Q4的第二端接地。其中,该实施例中第二比较器U4的第一输入端为负相输入端,第二输入端为正相输入端。当第二比较信号表征电源电压Vcc不高于第一阈值Vref1,且第二比较信号通过第二延时器D2的持续时间大于预定时间的情况下,中间检测信号OUT为高电平,否则中间检测信号OUT为低电平。其中,第二开关管Q4例如为N型MOS管。

如图7所示,保持单元1112包括第三延时器D3、第二非门U6、第三非门U9、第一与非门U7和第二与非门U8。第二非门U6的输入端连接电压检测单元1111的第二运算单元11112的第一恒等门U5的输出端以接收中间检测信号OUT,第二非门U6的输出端连接第一与非门U7的第一输入端,第一与非门U7的输出端连接第三非门U9的输入端,第三非门U9的输出端输出第一检测信号OUT1。第三延时器D3的输入端与第三非门U9的输出端连接,第三延时器D3的输出端与第二与非门U8的第一输入端连接,第二与非门U8的第二输入端与第一与非门U7的输出端连接,第二与非门U8的输出端与第一与非门U7的第二输入端连接。保持单元1112保持中间检测信号OUT的高电平状态,随着中间检测信号OUT翻转为低电平,在一定延时后,跟随翻转为低电平,进而输出与中间检测信号OUT的电平状态保持一致的第一检测信号OU1。

需要说明的是,本实施例中当电压检测单元1111检测到电源电压Vcc不高于第一阈值Vref1且持续了一段时间时,输出的中间检测信号OUT的电平状态由低电平变为高电平,且同时经由保持单元1112输出变为高电平的第一检测信号OUT1。

图8示出了根据本发明实施例提供的功率模块中的另一种保持单元的电路示意图。如图8所示,保持单元2112在保持单元1112的基础上增设了计数刷新单元2113,计数刷新单元2113包括振荡器OSC、第一触发器U11、第二触发器U12、第三触发器U13以及四输入与门U14。振荡器OSC的第一端连接电压检测单元1111的第二运算单元11112的第一恒等门U5的输出端以接收中间检测信号OUT,振荡器OSC的第二端分别连接第一触发器U11的第一输入端以及四输入与门U14的第一输入端A,第一触发器U11的第二输入端D连接第一触发器U11的输出端。第二触发器U12的第一输入端连接第一触发器U11的输出端并与四输入与门U14的第二输入端B连接,第二触发器U12的第二输入端D连接第二触发器U12的输出端。第三触发器U13的第一输入端连接第二触发器U12的输出端并与四输入与门U14的第三输入端C连接,第三触发器U13的第二输入端D连接第三触发器U13的输出端,且第三触发器U13的输出端与四输入与门U14的第四输入端E连接。四输入与门U14的输出端F作为保持单元1112的输入端与第二非门U6的输入端连接。计数刷新单元2113通过计数分频由四输入与门U14的输出端输出刷新关断信号,并通过保持单元1112的电路,进而输出第一检测信号OUT1。保持单元2112相较于保持单元1112增设了计数刷新单元2113,可以准确控制延时并不断刷新关断信号。需要说明的是,本实施例中采用另一种保持单元2112输出第一检测信号OUT1,本实施例中与保持单元2112连接的电压检测单元1111的第二延时器D2的延时系数低于预定时间。本实施例中当电压检测单元1111检测到电源电压Vcc不高于第一阈值Vref1且持续了小于预定时间时输出的中间检测信号OUT的电平状态由低电平变为高电平。在Vcc不高于第一阈值Vref1且持续了预定时间时由保持单元2112输出变为高电平的第一检测信号OUT1。

更进一步地,图9示出了根据本发明实施例提供的功率模块中的脉冲产生模块的电路示意图。

如图9所示,脉冲产生模块1120包括第一或非门U21、第二或非门U22、第四非门U23、第一边沿产生单元1121、第二边沿产生单元1122以及第三边沿产生单元1123。第一边沿产生单元1121的输入端与第一检测模块1110中保持单元1112连接以接收第一检测信号OUT1,第一边沿产生单元1121的输出端输出第一脉冲控制信号UV0。第一或非门U21的第一输入端与第一检测模块1110中保持单元1112连接以接收第一检测信号OUT1,第一或非门U21的第二输入端与第二或非门U22的输出端连接,第二或非门U22的第一输入端例如与第一信号处理模块1300的滤波处理单元1310连接以接收输入信号IN,第二或非门U22的第二输入端与第一或非门U21的输出端连接,第一或非门U21的输出端与第三边沿产生单元1123的输入端连接,第三边沿产生单元1123的输出端输出第三脉冲信号ON。第一或非门U21的输出端还与第四非门U23的输入端连接,第四非门U23的输出端与第二边沿产生单元1122的输入端连接,第二边沿产生单元1122的输出端输出第二脉冲信号OFF。第一检测信号OUT1进入脉冲产生模块1120的第一边沿产生单元1121,第一边沿产生单元1121在第一检测信号OUT1上升沿时生成第一脉冲控制信号UV0。第一检测信号OUT1和输入信号IN经由脉冲产生模块1120的第一或非门U21、第二或非门U22输入并进行运算,且通过第三边沿产生单元1123生成第三脉冲信号ON。第一检测信号OUT1和输入信号IN经由脉冲产生模块1120的第一或非门U21、第二或非门U22、第四非门U23输入并进行运算,且通过第二边沿产生单元1122生成第二脉冲信号OFF。

更进一步地,复位模块1130包括电平转移单元1131、信号恢复及整形单元1132以及第三与非门U1。电平转换单元1131与脉冲产生模块1120连接以接收第一脉冲控制信号UV0、第二脉冲信号OFF以及第三脉冲信号ON。电平转换单元1131用于将第一脉冲控制信号UV0翻转并生成中间脉冲信号UV1,第三与非门U1的第一输入端与电平转换单元1131连接以接收中间脉冲信号UV1,第三与非门U1的第二输入端与第二检测模块1140连接以接收第二检测信号OUT2,第三与非门U1的输出端与信号恢复及整形单元连接以提供复位信号OUT3。电平转移单元1131还与信号恢复及整形单元1132连接以传输由脉冲产生模块1120提供的第二脉冲信号ON和第三脉冲信号OFF。信号恢复及整形单元1132将接收到的复位信号OUT3、第二脉冲信号ON和第三脉冲信号OFF整形处理后输出至高压驱动单元1200进而控制是否复位高压驱动单元1200的输出的驱动信号。

进一步地,图10示出了根据本发明实施例提供的功率模块生成复位信号的时序示意图。

如图10所示,在t3阶段,第一检测模块1110的电压检测单元1111检测到电源电压Vcc不高于第一阈值Vref1且持续了预定时间时输出的中间检测信号OUT的电平状态由低电平变为高电平。进而中间检测信号OUT经由保持单元1112保持以进入脉冲产生模块1120,脉冲产生模块1120的第一边沿产生单元1121在保持单元1112提供的第一检测信号OUT1的上升沿到来时产生脉冲,进而生成第一脉冲控制信号UV0。复位模块1130的电平转换单元1131将接收的第一脉冲控制信号UV0电平翻转以生成中间脉冲信号UV1。第二检测模块1140在此阶段的T3时刻检测到悬浮供电电压Vbs不高于第二阈值Vref2,但在该阶段悬浮供电电压Vbs不高于第二阈值Vref2且未持续了预定时间,进而第二检测信号OUT2的电平状态保持为高电平。第一与非门U1在此阶段输出的复位信号OUT3的电平状态先变换为高电平而后变化为低电平。在此阶段,功率模块1000工作在风险模式,复位信号OUT3指示高压驱动单元1200复位输出的驱动信号。

在t4阶段的T4时刻之前,第一检测模块1110的电压检测单元1111检测到电源电压Vcc不高于第一阈值Vref1且持续了预定时间进而输出的中间检测信号OUT的电平状态保持为高电平,在t4阶段的T4时刻之后,第一检测模块1110的电压检测单元1111检测到电源电压Vcc高于第一阈值Vref1进而输出的中间检测信号OUT的电平状态由高电平变为低电平。进而中间检测信号OUT经由保持单元1112保持以进入脉冲产生模块1120,保持单元1112提供的第一检测信号OUT1随中间检测信号OUT的变化由高电平变为低电平。因此在此阶段第一检测信号OUT1没有上升沿到来,进而脉冲产生模块1120的第一边沿产生单元1121不产生脉冲,第一脉冲控制信号UV0保持为低电平。复位模块1130的电平转换单元1131将接收的第一脉冲控制信号UV0电平翻转以生成中间脉冲信号UV1,也即在此阶段中间脉冲信号UV1维持为高电平。第二检测模块1140在此阶段检测到悬浮供电电压 Vbs不高于第二阈值Vref2且持续了预定时间,进而第二检测信号OUT2的电平状态由高电平变为低电平。第一与非门U1在此阶段输出的复位信号OUT3的电平状态由低电平变为高电平。在此阶段的T4时刻之前,功率模块1000工作在欠压保护模式,复位信号OUT3指示高压驱动单元1200复位输出的驱动信号。在此阶段的T4时刻之后,功率模块1000工作在待机模式,复位信号OUT3指示高压驱动单元1200复位输出的驱动信号。

在t5阶段,第一检测模块1110的电压检测单元1111检测到电源电压Vcc高于第一阈值Vref1进而输出的中间检测信号OUT的电平状态维持为低电平。进而中间检测信号OUT经由保持单元1112保持以进入脉冲产生模块1120,保持单元1112提供的第一检测信号OUT1随中间检测信号OUT保持为低电平。因此在此阶段第一检测信号OUT1没有上升沿到来,进而脉冲产生模块1120的第一边沿产生单元1121不产生脉冲,第一脉冲控制信号UV0保持为低电平。复位模块1130的电平转换单元1131将接收的第一脉冲控制信号UV0电平翻转以生成中间脉冲信号UV1,也即在此阶段中间脉冲信号UV1维持为高电平。第二检测模块1140在此阶段检测到悬浮供电电压 Vbs高于第二阈值Vref2进而第二检测信号OUT2的电平状态由低电平变为高电平。第一与非门U1在此阶段输出的复位信号OUT3的电平状态由高电平变为低电平。在此阶段,功率模块1000工作在工作模式,复位信号OUT3指示高压驱动单元1200正常输出驱动信号。

图11a示出了根据本发明实施例提供的功率模块生成第二脉冲信号及第三脉冲信号的一种时序示意图。

如图11a所示,是脉冲产生模块1120基于由保持单元1112生成的第一检测信号OUT1、以及输入信号IN生成第二脉冲信号OFF和第三脉冲信号ON的时序示意图。在T5时刻之前,第一检测模块1110的电压检测单元1111检测到电源电压Vcc高于第一阈值Vref1或者不高于第一阈值Vref1且未持续预定时间进而输出的中间检测信号OUT的电平状态维持为低电平。进而中间检测信号OUT经由保持单元1112保持并提供的第一检测信号OUT1也维持为低电平。脉冲产生模块1120的第一边沿产生单元1121基于第一检测信号OUT1生成第一脉冲控制信号UV0。其中,在T5时刻之前第一检测信号OUT1没有上升沿到来,进而第一脉冲控制信号UV0维持为低电平。在第一检测信号OUT1维持为低电平的情况下开启输入响应,脉冲产生模块1120基于逻辑门的运算并通过第二边沿产生单元1122在输入信号IN的下降沿到来时产生脉冲进而生成第二脉冲信号OFF;以及脉冲产生模块1120基于逻辑门的运算并通过第三边沿产生单元1123在输入信号IN的上升沿到来时产生脉冲进而生成第三脉冲信号ON。在T5时刻之后以及T6时刻之前,第一检测模块1110的电压检测单元1111检测到电源电压Vcc不高于第一阈值Vref1且持续了预定时间进而输出的中间检测信号OUT的电平状态由低电平变为高电平。进而中间检测信号OUT经由保持单元1112保持并提供的第一检测信号OUT1也变为高电平。脉冲产生模块1120的第一边沿产生单元1121基于第一检测信号OUT1,进而生成第一脉冲控制信号UV0。其中,在T5时刻第一检测信号OUT1的上升沿到来,进而产生脉冲,第一脉冲控制信号UV0的电平状态先变为高电平之后脉冲结束后再变为低电平。在第一检测信号OUT1上升沿到来时,脉冲产生模块1120基于逻辑门的运算并通过第二边沿产生单元1122在输入信号IN维持为高电平时产生脉冲进而生成第二脉冲信号OFF。在第一检测信号OUT1维持为高电平的情况下,脉冲产生模块1120基于逻辑门的运算并通过第三边沿产生单元1123不产生脉冲进而第三脉冲信号ON维持为低电平。在T6时刻之后,第一检测模块1110的电压检测单元1111检测到电源电压Vcc高于第一阈值Vref1进而输出的中间检测信号OUT的电平状态变为低电平。进而中间检测信号OUT经由保持单元1112保持并提供的第一检测信号OUT1在延时一段时间后也维持为低电平,之后第二脉冲信号ON及第三脉冲信号OFF的电平状态的变换原理与时刻T5之前的相同。

图11b示出了根据本发明实施例提供的功率模块生成第二脉冲信号及第三脉冲信号的另一种时序示意图。

如图11b所示,是脉冲产生模块1120基于由另一种保持单元2112生成的第一检测信号OUT1、以及输入信号IN生成第二脉冲信号OFF和第三脉冲信号ON的时序示意图。与上述11a示出的时序不同的地方在于生成第一检测信号OUT1的原理发生了变化,对应地时序图相比于图11a,不同之处仅仅是生成第一检测信号OUT1之前的阶段,以下主要对生成第一检测信号OUT1的波形做说明。

在T5时刻之后级T6时刻之前,第一检测模块1110的电压检测单元1111检测到电源电压Vcc不高于第一阈值Vref1且持续了一段时间进而输出的中间检测信号OUT的电平状态为高电平,其中,上述一段时间大于其预定时间,具体地,上述一段时间例如为预定时间加四分频的时间。进而中间检测信号OUT进入保持单元2112首先被分频并进入保持单元2112中的四输入与门U14,四输入与门U17的第一输入端A处的信号Va、第二输入端B处的信号Vb、第三输入端C处的信号Vc、第四输入端E处的信号Ve经过与运算之后,其输出端F处的信号Vf为高电平时,进而输出端F处的信号Vf进入保持单元2112中的一种保持单元1112中之后运算输出变为高电平状态的第一检测信号OUT1。在T6时刻之后,第一检测模块1110的电压检测单元1111检测到电源电压Vcc高于第一阈值Vref1进而输出的中间检测信号OUT的电平状态变为低电平。进而输出端F处的信号Vf进入保持单元2112中的一种保持单元1112中之后经运算延时之后变为低电平状态的第一检测信号OUT1。

依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

- 高压驱动电路及功率模块

- 一种上桥臂驱动电路、高压集成电路以及功率模块