具有备份块的缓存编程

文献发布时间:2023-06-19 13:49:36

技术领域

本发明涉及NAND闪存设备的管理和实现,特别涉及NAND闪存设备的编程操作。

背景技术

固态硬盘(SSD)的出现在一定程度上推动了现代计算系统的发展,固态硬盘(SSD)的速度和延迟性能比传统硬盘更高。与依靠磁性来存储数据的硬盘不同,固态驱动器使用NAND闪存设备来实现数据存储。NAND闪存设备是通过先进的工艺和组装技术制造的集成电路系列,可实现多层存储单元垂直堆叠到较小的颗粒和封装中,从而实现高存储容量。

新的NAND闪存工艺技术突破带来的存储容量增加也导致NAND存储单元的可靠性降低。对于NAND闪存设备,编程操作是指将数据写入NAND闪存设备的操作。并且NAND闪存设备通常包含坏块,其中包括最初在制造过程中存在缺陷的原厂坏块(factory bad block)和经过多次编程和擦除(P/E)循环后变得有缺陷的生长坏块(grown bad block)。作为一个众所周知的行为,NAND存储单元开始随着P/E循环次数的增加而磨损,导致错误计数的增加和生长坏块的增加。

NAND闪存设备通常提供两种编程操作:规则编程操作和高速缓存编程操作。这两种编程操作都包括将数据接收到高速缓存寄存器(cache buffer)中,并将数据移动到数据寄存器(data buffer)和NAND存储单元阵列中。高速缓存编程操作将在完成从高速缓存缓冲器到数据缓冲器的数据传输时应答SSD控制器。相比之下,在完成数据传输到NAND存储单元阵列之前,规则编程操作不会应答SSD控制器,这需要几毫秒量级的长时间的编程时间(例如,tPROG)。

大多数现代SSD控制器利用高速缓存编程操作来最大限度地提高写入NAND闪存设备的性能。在启用该特性的情况下,SSD控制器一旦从NAND设备听到数据已从高速缓存缓冲器移动到数据缓冲器中,就向主机应答写命令完成。然而,这种方法具有编程错误的潜在风险,其中,当特定NAND块存在缺陷并且SSD控制器不知情的情况下,将数据写入NAND存储单元的最终操作可能仍会失败。这对于NAND闪存设备来说尤其是一个挑战,随着时间的推移,生长坏块的数量越来越多。

为了解决前面提到的在向主机过早应答的情况下向NAND存储阵列中的潜在写入失败的问题,具有板上DRAM的SSD控制器可以被配置为在DRAM中保留数据的副本,直到后来确认成功地将其写入NAND存储阵列。如果NAND报告一个编程错误,SSD控制器然后可以简单地用来自DRAM的数据对NAND设备进行另一个编程操作。

然而,对于一个没有DRAM的SSD控制器来说,这是一个更大的挑战,因为控制器只能在其内部SRAM中保留少量有限的数据。来自主机的写命令可能会很快超过内部SRAM的存储能力,而控制器仍在等待NAND存储设备对SRAM中存储的有限数据量进行缓慢确认,从而导致SRAM溢出。结果,在高速缓存编程操作期间,没有DRAM的SSD控制器可能无法将所有临时数据保存到其内部SRAM,这可能导致未能保存到NAND存储器的数据也未能从SRAM恢复的灾难性故障。试图改善这种情况的现有解决方案可能必须限制使用没有DRAM的SSD控制器的缓存编程操作的数量,这会导致性能下降。或者,现有的解决方案也可能以更大的芯片尺寸和更高的硅成本为代价增加内部SRAM的数量。

发明内容

本公开提供了一种非易失性存储设备高速缓存编程操作,其使用备份块以消除由于编程错误而导致的数据丢失的风险。备份块映射表可用于存储规则块和备份块之间的链接。在高速缓存编程操作期间,数据页被复制到目标规则块及其映射的备份块中。在目标规则块发生编程错误的情况下,从备份块处的备份副本中恢复数据。在一些实施例中,备份块可以使用由超额配置所提供的额外物理块中的一些。

在示例性实施例中,提供了一种方法,该方法可以包括:从存储控制器向非易失性存储设备发出第一高速缓存编程操作以将数据写入第一规则块,根据所述第一高速缓存编程操作将所述数据写入所述非易失性存储设备处的所述第一规则块,将所述数据的副本写入所述非易失性存储设备处的备份块,确定在将所述数据写入所述第一规则块时编程错误已发生,向所述存储控制器声明编程错误,由所述存储控制器从映射表中获取所述第一规则块和所述备份块之间的映射,从所述存储控制器向非易失性存储设备发出读取操作以从所述备份块中读取数据的副本,从所述备份块中读取所述数据的副本,并将所述数据的副本发送到所述存储控制器,以及从所述存储控制器向所述非易失性存储设备发出第二高速缓存编程操作以将所述数据写入第二规则块,并将所述第一规则块标记为缺陷。

在另一个示例性实施例中,提供了一种非易失性存储系统。所述非易失性存储系统可以包括非易失性存储设备和耦合到所述非易失性存储设备的存储控制器。所述存储控制器可以被配置为:向所述非易失性存储设备发出第一高速缓存编程操作以将数据写入第一规则块,从所述非易失性存储设备接收编程错误,从映射表中获取所述第一规则块与备份块之间的映射,向所述非易失性存储设备发出读取操作以从所述备份块中读取数据的副本,以及向所述非易失性存储设备发出第二高速缓存编程操作以将所述数据写入第二规则块并将所述第一规则块标记为缺陷。所述非易失性存储装置可以被配置为:根据所述高速缓存编程操作将所述数据写入所述第一规则块;将所述数据的副本写入所述备份块;确定在将所述数据写入所述第一规则块时所述编程错误已发生;向所述存储控制器声明所述编程错误;根据所述读取操作从所述备份块读取所述数据的副本,并将所述数据的副本发送给所述存储控制器。

在又一示例性实施例中,提供了一种非暂时性机器可读介质。所述非暂时性机器可读介质可以具有计算机指令,当由存储控制器的硬件处理器执行时,使硬件处理器:向非易失性存储设备发出第一高速缓存编程操作以将数据写入第一规则块,从所述非易失性存储设备接收编程错误,从映射表中获取所述第一规则块与备份块之间的映射,向所述非易失性存储设备发出读取操作以从所述备份块中读取数据的副本,以及向所述非易失性存储设备发出第二高速缓存编程操作以将数据写入第二规则块并将所述第一规则块标记为缺陷。

附图简要说明

图1示意性地示出了根据本公开的一个实施例的非易失性存储系统。

图2示意性地示出了根据本公开的一个实施例的高速缓存编程操作中的数据移动。

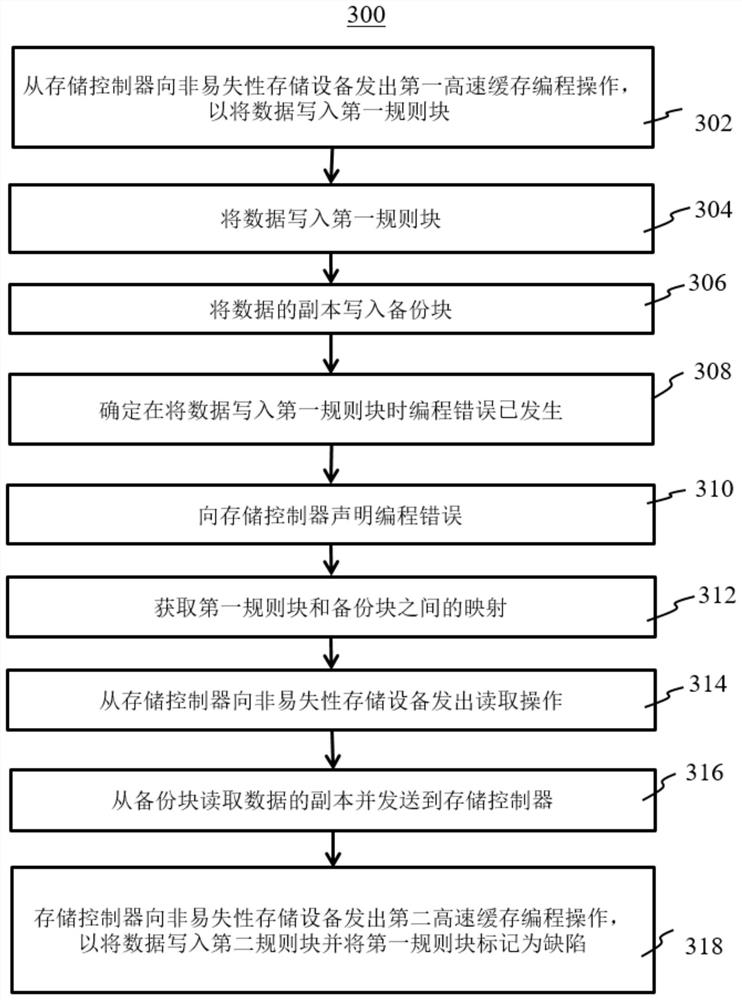

图3是根据本公开的一个实施例的用于在非易失性存储系统中执行高速缓存编程操作的过程的流程图。

具体实施方式

现在将参考附图详细描述根据本申请的具体实施例。为了一致性,各个图中的相同元件由相同的附图标记表示。

本公开提供了用于高速缓存编程的系统和方法,所述高速缓存编程使用备份块来存储正被写入到非易失性存储设备的规则块的数据的副本。如本文所使用的,非易失性存储设备可以是在断电之后能够维持存储的信息的计算机存储设备,并且可以在断电之后(关闭和重新打开)获取存储的信息。非易失性存储设备可以包括NAND闪存、NOR闪存、磁阻随机存取存储器(MRAM)、电阻式随机存取存储器(RRAM)、相变随机存取存储器(PCRAM)、Nano-RAM等。NAND闪存可以用作示例,用于演示如何实现高速缓存编程操作。然而,根据本公开的各种实施例可以利用其他类型的非易失性存储设备来实现该技术。

图1示意性地示出了根据本公开的一个实施例的非易失性存储系统100。非易失性存储系统100可以包括存储控制器102和非易失性存储设备104。当非易失性存储系统100耦合到主机时,该非易失性存储系统100可以为主机提供数据存储和/或对存储数据的访问。非易失性存储设备104可以是基于非易失性存储器(NVM)的存储设备,例如,NAND设备。应当注意,非易失性存储系统100可以包括多个非易失性存储设备,并且非易失性存储设备104可以被示为多个非易失性存储设备的代表。存储控制器102可以包括处理器106和存储器108。处理器106可以是计算机处理器,例如但不限于微处理器或微控制器。存储器108可以是非暂时性计算机可读存储介质,例如DRAM或SRAM,以存储将由处理器106执行的计算机可执行指令。

在各种实施例中,非易失性存储设备104可以包含比公布的容量(volume)更多的物理块。这可能被称为超额配置(overprovision,或over-provision)。额外的物理块可以用于坏块管理、垃圾回收和刷新。在一些实施例中,非易失性存储设备104中的物理块可以被分类为规则块和备份块。规则块可以是用于存储数据的普通物理块,例如,在所公布的容量中的物理块。备份块可用于临时存储用于高速缓存编程操作的备份数据。例如,由超额配置提供的大量备用块可以是冗余块,并且可以用作备份块。在一个实施例中,当数据被写入用于高速缓存编程操作的规则块时,数据的副本可以被写入备份块。在数据被写入规则块时发生错误的情况下,可以获取数据的副本并将其写入另一规则块。因此,根据本公开一个实施例的高速缓存编程操作可以从编程错误中恢复而不会丢失数据。

非易失性存储设备104可以包括一个或多个芯片,并且每个芯片可以包括一个或多个平面(plane),每个平面具有多个物理块。在一些实施例中,所需的备份块的数量可以比相应的规则块的数量小得多。一个平面的规则块可以具有一组备份块来提供数据备份。备份块可以被保持在列表中,并且对于平面的规则块以循环方式分配给规则块。例如,假设可能存在M个备份块(例如,块0、1、…、M-1),平面的规则块可以被分配给从块0到块M-1的备份块,然后从块0再次以循环方式重复,直到所有规则块都可以被分配一个备份块。因此,规则块可以以多对一的关系映射到备份块,其中多个规则块映射到一个备份块。

存储控制器102可以实现许多技术来管理备份块。例如,在一个实施例中,非易失性存储设备104的规则块可以是多比特单元(例如,多级单元(MLC)或三级单元(TLC),而备份块可以是单比特单元(例如,单级单元(SLC))。由于多对一的映射关系,备份块可以比规则块经历更多的编程/擦除(P/E)操作,并且SLC单元可以提供对P/E操作的最大可靠性和耐久性。此外,存储控制器102可以通过跟踪P/E循环和错误计数来监视备份块的磨损。在一些实施例中,例如,可以设置错误计数的阈值使得进一步增加的错误不再是可纠正的。当备份块的错误计数增加到达到阈值时,可以将备份块视为已达到其寿命,并且存储控制器102可以配置为退休备份块(例如,将其从备份块的列表和映射表中移除)并选择另一个块(例如,SLC块)来替换退休的备份块。

图2示意性地示出了根据本公开的一个实施例的高速缓存编程操作中的数据移动。存储控制器102可以在高速缓存编程操作中将数据页202写入非易失性存储设备104。高速缓存编程操作可以具有包括物理地址的字段,该物理地址可以标识用于保存数据的目标位置。目标位置可以是规则块206内的页208。可以在非易失性存储设备104的缓冲器204中接收数据页,并且非易失性存储设备104可以将数据写入规则块206的页208。规则块206可以具有指定的备份块210,并且可以将数据的副本写入备份块210内的页212。

缓冲器204可以包括高速缓存缓冲器和规则缓冲器。高速缓存编程操作可以在完成从高速缓存缓冲器到数据缓冲器的数据传输时应答存储控制器102。相比之下,规则编程操作直到完成向非易失性存储设备104的存储阵列(例如,规则块206)中的数据传输才会应答存储控制器102,这需要几毫秒量级的长时间tPROG。通过使用备份块210来存储数据页202的副本,即使在将数据写入规则块206时存在编程错误,用于将数据页写入规则块206的页208的高速缓存编程操作也可以在完成从高速缓存缓冲器到数据缓冲器的数据传输而没有数据丢失时向存储控制器102应答。

在一些实施例中,对于通过高速缓存编程操作从存储控制器102写入非易失性存储设备104的每一个数据页,非易失性存储设备104除了将数据写入在高速缓存编程操作的地址中指定的规则块之外,还可以制作数据的副本,并将数据的副本写入备份块m(其中m是0、1、…、M-1)。数据的副本也可以称为数据的备份副本。

在示例实现中,备份块列表中的备份块的数量可以被设置为每个平面4个。这是因为在数据被写入非易失性存储设备104的存储阵列的给定时间,每个平面可以有最多2个附加传输,一个从存储控制器102到非易失性存储设备104的高速缓存缓冲器,另一个从非易失性存储设备104的高速缓存缓冲器到非易失性存储设备104的数据缓冲器。通过每个平面具有4个备份块,可以确保在编程错误被声明之前,备份块中的数据不会被覆盖。

可以保留以将备份块与规则块链接起来的映射表。映射表可以记录每个规则块被映射到哪个备份块中。在一个实施例中,映射表可由存储控制器102管理并动态更新。在另一实施例中,映射表也可由非易失性存储设备104管理,并使其对存储控制器102可见。应当注意,如果非易失性存储设备104具有多个平面,则在一个实施例中,可以有多个映射表,使得每个平面可以具有其自己的映射表。在另一个实施例中,非易失性存储设备104可以具有用于所有规则块的一个映射表。表一示出了一个实施例中规则块和备份块之间的示例性映射。应当注意,左列可以包括许多不同的块,而右列可以包括以循环方式重复的M个块。

映射表一

图3是根据本公开的一个实施例的用于在非易失性存储系统中执行高速缓存编程操作的过程300的流程图。在框302中,可以从存储控制器向非易失性存储设备发出第一高速缓存编程操作,以将数据写入第一规则块。在一个实施例中,例如,存储控制器102可以向非易失性存储设备104发出高速缓存编程操作,以将数据写入非易失性存储设备104中的规则块A。在框304中,根据高速缓存编程操作,可以将数据写入非易失性存储设备处的第一规则块,并且在框306中,可以将数据的副本写入非易失性存储设备处的备份块。在一个实施例中,通过如示例映射表一中所示的从规则块A到备份块0的映射,可以将数据的副本写入映射到规则块A的备份块0。

在框308中,可以确定在将数据写入第一规则块时编程错误已发生,并且在框310中,可以向存储控制器声明编程错误。在一个实施例中,如果在编程时没有向规则块A报告编程错误,则可以认为高速缓存编程操作成功完成。然而,如果在将数据写入规则块A时报告了任何编程错误,则非易失性存储设备104可以向存储控制器102声明该编程错误。

在框312中,存储控制器可以从映射表中获取第一规则块和备份块之间的映射。在一个实施例中,一旦接收到编程错误,存储控制器102可以从映射表一获得规则块A和备份块0之间的映射。

在框314中,可以从存储控制器向非易失性存储设备发出读取操作,以从备份块读取数据的副本。在一个实施例中,利用映射信息,存储控制器102可以确定数据的副本存储在备份块0中,并向非易失性存储设备104发出读取操作以从备份块0读取数据的副本。在框316中,可以从备份块读取数据的副本并将其发送到存储控制器。例如,非易失性存储设备104可以从备份块0读取数据的副本,并将数据的副本发送到存储控制器104。在框318中,存储控制器可向非易失性存储设备发出第二高速缓存编程操作,以将数据写入第二规则块并将第一规则块标记为缺陷。在一个实施例中,利用从备份块0获得的数据的副本,存储控制器102可以发出另一高速缓存编程操作以将数据写入另一规则块(例如,规则块B,其可根据映射表一映射到备份块1)。同时,存储控制器102可以将块A标记为坏块并将其从存储使用中移除。

可以使用软件(例如,可由计算机处理器(CPU,GPU或两者)执行)、硬件(例如,现场可编程门阵列(FPGA)或专用IC(ASIC))、固件、或三者的任何适当组合来实现过程300的至少一部分。在一个实施例中,例如,将由存储控制器102执行的过程300的部分可以编程在计算机处理器可执行指令中,存储在非暂时性机器可读介质(例如,存储器108、非易失性存储设备104、硬盘驱动器、CD、DVD等)中,并由执行可执行指令的处理器102(例如,微处理器或微控制器)执行。

在示例性实施例中,提供了一种方法,该方法可以包括:从存储控制器向非易失性存储设备发出第一高速缓存编程操作以将数据写入第一规则块;根据所述第一高速缓存编程操作将所述数据写入所述非易失性存储设备处的所述第一规则块;将所述数据的副本写入所述非易失性存储设备处的备份块;确定在将所述数据写入所述第一规则块时编程错误已发生;向所述存储控制器声明所述编程错误;由所述存储控制器从映射表中获取所述第一规则块与所述备份块之间的映射;从所述存储控制器向所述非易失性存储设备发出读取操作,以从所述备份块读取所述数据的副本;从所述备份块读取所述数据的副本,并将所述数据的副本发送到所述存储控制器;和从所述存储控制器向所述非易失性存储设备发出第二高速缓存编程操作以将所述数据写入第二规则块,并将所述第一规则块标记为缺陷。

在一个实施例中,所述备份块可以包括单比特单元的存储单元,并且所述第一规则块和所述第二规则块包括多比特单元的存储单元。

在一个实施例中,该方法可以进一步包括获得所述备份块的错误计数,并且,当所述错误计数达到阈值时,确定所述备份块已经达到其寿命,以及用新备份块替换所述备份块。

在一个实施例中,用所述新备份块替换所述备份块可以包括将所述映射表中的所述备份块更新为所述新备份块。

在一个实施例中,所述映射表可以包含以循环方式重复映射到平面中的规则块的四个备份块。

在一个实施例中,所述映射表可以由存储控制器管理。

在一个实施例中,所述映射表可以由所述非易失性存储设备管理,并提供给所述存储控制器,用于所述存储控制器获得所述第一规则块与所述备份块之间的映射。

在一个实施例中,所述备份块可以是由超额配置所提供的备用块。

在另一个示例性实施例中,提供了一种非易失性存储系统。所述非易失性存储系统可以包括非易失性存储设备和耦合到所述非易失性存储设备的存储控制器。所述存储控制器可以被配置为:向所述非易失性存储设备发出第一高速缓存编程操作以将数据写入第一规则块,从所述非易失性存储设备接收编程错误,从映射表中获取所述第一规则块与备份块之间的映射,向所述非易失性存储设备发出读取操作以从所述备份块中读取数据的副本,以及向所述非易失性存储设备发出第二高速缓存编程操作以将所述数据写入第二规则块并将所述第一规则块标记为缺陷。所述非易失性存储装置可以被配置为:根据所述高速缓存编程操作将所述数据写入所述第一规则块;将所述数据的副本写入所述备份块;确定在将所述数据写入所述第一规则块时所述编程错误已发生;向所述存储控制器声明所述编程错误;根据所述读取操作从所述备份块读取所述数据的副本,并将所述数据的副本发送给所述存储控制器。

在一个实施例中,所述备份块可以包括单比特单元的存储单元,并且所述第一规则块和所述第二规则块可以包括多比特单元的存储单元。

在一个实施例中,所述存储控制器还可以被配置为获得备份块的错误计数,当错误计数达到阈值时确定备份块已经达到其寿命,并且用新备份块替换所述备份块。

在一个实施例中,用所述新备份块替换所述备份块可以包括将所述映射表中的所述备份块更新为所述新备份块。

在一个实施例中,所述映射表可以包含以循环方式重复映射到平面中的规则块的四个备份块。

在一个实施例中,所述的映射表可以由存储控制器管理。

在一个实施例中,所述映射表可以由所述非易失性存储设备管理,并提供给所述存储控制器,用于所述存储控制器获得所述第一规则块与所述备份块之间的映射。

在一个实施例中,所述备份块可以是由超额配置所提供的备用块。

在又一示例性实施例中,提供了一种非暂时性机器可读介质。所述非暂时性机器可读介质可以具有计算机指令,当由存储控制器的硬件处理器执行时,使硬件处理器:向非易失性存储设备发出第一高速缓存编程操作以将数据写入第一规则块,从所述非易失性存储设备接收编程错误,从映射表中获取所述第一规则块与备份块之间的映射,向所述非易失性存储设备发出读取操作以从所述备份块中读取数据的副本,以及向所述非易失性存储设备发出第二高速缓存编程操作以将数据写入第二规则块并将所述第一规则块标记为缺陷。

在一个实施例中,所述备份块可以包括单比特单元的存储单元并且是由超额配置所提供的备用块之一,并且所述第一规则块和所述第二规则块包括多比特单元的存储单元。

在一个实施例中,当由所述存储控制器的硬件处理器执行时,所述计算机指令可进一步使硬件处理器:获得备份块的错误计数,当错误计数达到阈值时确定备份块已经达到其寿命,并且用新备份块替换所述备份块。

在一个实施例中,所述映射表可以由存储控制器管理,或者由所述非易失性存储设备管理,并提供给所述存储控制器,用于所述存储控制器获得所述第一规则块与所述备份块之间的映射。

任何公开的方法和操作可以被实现为存储在一个或多个计算机可读存储介质(例如,非暂时性计算机可读介质,例如,一个或更多个光盘介质,易失性存储组件(例如DRAM或SRAM),或非易失性存储组件(例如硬盘驱动器)上并在设备控制器(例如,ASIC执行的固件)上执行的计算机可执行指令(例如,本文描述的操作的软件代码)。可以将用于实现所公开的技术的任何计算机可执行指令以及在所公开的实施例的实现期间创建和使用的任何数据可以存储在一个或多个计算机可读介质(例如,非暂时性计算机可读介质)上。

尽管本文已经公开了各个方面和实施例,但是其他方面和实施例对于本领域技术人员将是显而易见的。本文所公开的各个方面和实施例是出于说明的目的,而不是旨在进行限制,真实的范围和精神由所附权利要求书指示。

- 具有备份块的缓存编程

- 具有备份电路的存储系统及编程方法