一种射频收发电路

文献发布时间:2023-06-19 19:14:59

技术领域

本发明涉及无线通信设备技术领域,尤其涉及一种射频收发电路。

背景技术

为了满足人们不同的通信需求,种类繁多的无线通信标准被相继提出。目前主流的无线通信标准主要集中于45MHz~2.5GHz频段范围内,按照应用领域大致可分为四大类:数字蜂窝通信标准(LTE、CDMA、TD-SCDMA、CDMA200、GSM、WiMAX等)、无线接入通信标准(WLAN、Bluetooth、UWB、ZigBee、RFID等)、移动广播通信标准(DVB、CMMB、ATSC等)和导航定位通信标准(GPS、Galileo、Glonass、BDS等)。每一种通信标准具有不同的中心频率、信道带宽、噪声指标、线性度指标、发射功率等。因此软件无线电收发机射频前端电路必须同时具有大动态范围的可配置性,又要满足不同通信标准的性能指标要求。

为了能够便捷通信,用户希望将尽可能多的应用集成到一台移动通信终端。软件无线电技术可使通信终端支持不同通信标准:根据不同调制或者编码制式,使用不同的数据接口,动态加载不同的系统软件架构,无需修改硬件电路。由于软件无线电能够以一个通用、标准、模块化的硬件平台为依托,通过软件编程来实现无线电台的各种功能,通过体系结构的开放性和全面可编程性,通过软件更新改变硬件配置结构,实现新的功能。目前,主要通过软件无线电信号收发平台实现多通信标准的通信,能够根据其不同的应用环境,灵活配置其性能指标,尽可能实现各通信指标的折衷。

目前国内软件无线电收发机虽然基带算法已经取得了一定的突破,但是射频前端电路依然是收发机的设计瓶颈。目前出现了一些多标准可配置的收发机射频前端电路,仅仅能够实现部分可配置,支持部分通信标准,同时目前的软件无线电平台的射频接收链路和发射链路分离,缺少射频信号自检回路。

发明内容

本发明针对上述缺陷公开了一种射频收发电路,具有灵活的可配置性,支持宽频宽带性能,同时支持发射链路与接收链路对接自回环检测。

本申请一种射频收发电路,包括:可编程射频收发集成电路;

可编程射频收发集成电路包括:至少一个接收通道、至少一个发射通道和控制电路;

任一接收通道包括:依次连接的低噪声放大电路、第一混频放大电路、第一低通滤波电路和模数转换电路,以及与第一混频放大电路连接的第一频率合成电路;

任一发射通道包括:依次连接的数模转换电路、第二低通滤波电路、第二混频放大电路和功率放大电路,以及与第二混频放大电路连接的第二频率合成电路;

所述控制电路用于控制任一接收通道和任一发射通道的信号传输;

其中,任一接收通道和任一发射通道中多个电路设置有可编程接口,用于接收所述控制电路的配置信号。

可选的,所述射频收发电路还包括:射频前端电路;

所述射频前端电路包括天线接口、功率放大电路和射频开关单元;

所述天线接口用于接入射频无线信号,所述功率放大电路对所述射频无线信号进行放大处理,所述射频开关单元用于信号路径选择。

可选的,所述射频开关单元包括设置在接收链路上、位于天线接口与可编程射频收发集成电路之间的第一开关,以及设置在发射链路上,位于天线接口与可编程射频收发集成电路之间的第二开关;所述第一开关与第二开关可选择连通或断开,当所述第一开关与第二开关选择连通时,所述射频收发电路进入通信链路回环自检模式。

可选的,所述第一频率合成电路和所述第二频率合成电路为同一电路,用于产生下混频或上混频本振信号。

可选的,所述任一接收通道还包括:设置在第一低通滤波电路和模数转换电路之间的第一可变增益放大器,用于可配置调节接收链路的信号增益。

可选的,所述第一可变增益放大器包括:一级增益放大细调电路和多级增益放大粗调电路。

可选的,所述任一发射通道还包括:设置在第二低通滤波电路和第二混频放大电路之间的第二可变增益放大器,用于可配置调节发射链路的信号增益。

可选的,所述第二可变增益放大器包括:一级增益放大细调电路和多级增益放大粗调电路。

可选的,所述射频收发电路还包括:与可编程射频收发集成电路连接的时钟电路,用于为可编程射频收发集成电路提供时钟信号。

可选的,可编程接口包括控制参数配置接口和环境参数配置接口。

本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

1)射频收发电路包括:可编程射频收发集成电路;可编程射频收发集成电路包括:至少一个接收通道、至少一个发射通道和控制电路;所述控制电路用于控制任一接收通道和任一发射通道的信号传输;其中,任一接收通道和任一发射通道中多个电路设置有可编程接口,用于接收所述控制电路的配置信号。实现了可编程控制收发集成电路,具有灵活的可配置性,通过配置能够使得射频信号中心频率覆盖MHz级别至GHz级别的频率范围,支持TDD和FDD工作模式,通道带宽可调谐,满足不同通信标准的射频收发要求。

2)本发明射频前端电路设置有射频开关单元,设置在接收链路的第一开关和设置在发射链路的第二开关可选择连通,且在二者连通时所述射频收发电路进入通信链路回环自检模式。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其它的附图。

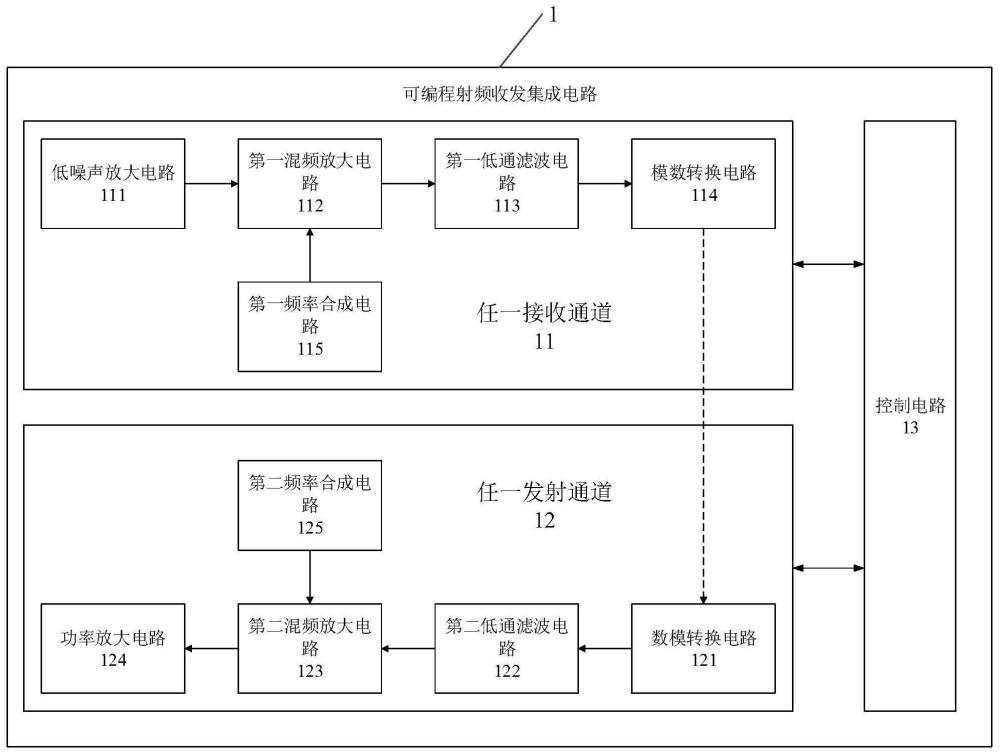

图1为本发明实施例提供的一种射频收发电路的可编程射频收发集成电路结构框图;

图2A为本发明实施例提供的一种射频收发电路的整体结构框图;

图2B为本发明实施例提供的一种射频前端电路的电路原理图;

图3为本发明实施例提供的一种频率合成电路的电路原理图;

图4为本发明实施例提供的一种低通滤波电路的结构图;

图5为本发明实施例提供的一种具有可变增益放大器的射频收发电路接收通道的结构框图;

图6为本发明实施例提供的一种具有可变增益放大器的射频收发电路发射通道的结构框图;

图7为本发明实施例提供的一种可变增益放大器的电路结构图。

具体实施方式

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对照附图说明本发明的具体实施方式。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图,并获得其它的实施方式。

为使图面简洁,各图中只示意性地表示出了与本发明相关的部分,它们并不代表其作为产品的实际结构。另外,以使图面简洁便于理解,在有些图中具有相同结构或功能的部件,仅示意性地绘示了其中的一个,或仅标出了其中的一个。在本文中,“一个”不仅表示“仅此一个”,也可以表示“多于一个”的情形。

下面以具体实施例详细介绍本发明的技术方案。

请参考图1,本发明实施例提供一种射频收发电路,包括:可编程射频收发集成电路1;可编程射频收发集成电路1包括:至少一个接收通道11、至少一个发射通道12和控制电路13;任一接收通道11包括:依次连接的低噪声放大电路111、第一混频放大电路112、第一低通滤波电路113和模数转换电路114,以及与第一混频放大电路112连接的第一频率合成电路115;任一发射通道12包括:依次连接的数模转换电路121、第二低通滤波电路122、第二混频放大电路123和功率放大电路124,以及与第二混频放大电路123连接的第二频率合成电路125;控制电路13用于控制任一接收通道11和任一发射通道12的信号传输;其中,任一接收通道11和任一发射通道12中多个电路设置有可编程接口,用于接收控制电路13的配置信号。同时,控制电路13还能够接收至少一个接收通道11和/或至少一个发射通道12的反馈信息,并根据反馈信息进行参数配置。其中,可编程接口包括控制参数配置接口和环境参数配置接口;控制参数主要关系电路模块的功能和性能,环境参数主要关系电路模块的温度、湿度、电磁环境情况等。

接收电路(对应接收通道),信号经前端放大,并与第一频率合成电路115输出的本振信号进行混频,将射频信号直接下变频到中频信号,中频信号经接收电路中频放大、滤波后最终输出。发射电路(对应发射通道),将基带信号经发射电路中频滤波、放大后,再经上混频器与第二频率合成电路125输出的本振信号进行混频,混频后的信号经功率放大器放大后输出。

在具体实施过程中,可编程射频收发集成电路1具体可为无线收发器芯片,整个无线收发器芯片所有工作状态及工作模式寄存器均通过控制电路13以串行SPI接口进行配置,SPI采用四线制标准协议,工作模式为全双工。为了便于控制,此无线收发器芯片在功率检测模式下可通过功率检测模块实现发射功率检测。

在具体实施过程中,请参考图2A,所述射频收发电路还包括射频前端电路2;射频前端电路2包括天线接口21、功率放大单元22和射频开关单元23;天线接口21用于接入射频无线信号,功率放大单元22对所述射频无线信号进行放大处理,射频开关单元23用于信号路径选择。具体的,射频开关单元23包括设置在接收链路上、位于天线接口21与可编程射频收发集成电路1之间的第一开关231,以及设置在发射链路上,位于天线接口21与可编程射频收发集成电路1之间的第二开关232;第一开关231与第二开关232可选择连通或断开,当第一开关231与第二开关232选择连通时,所述射频收发电路进入通信链路回环自检模式。射频回环检测,主要用于IQ校准、本振泄漏校准。发射信号经过内置的射频开关后,输出到接收端LNA输出,混频器输入,下变频后由ADC后的数字模块进行分析,并适应性地做出调整。

其中,天线接口21能够兼容多种型号的射频天线。天线接口21包括用于连接信号接收天线的至少一个接口和用于连接信号发射天线的至少一个接口。

如图2B为本申请的射频前端电路的电路原理图:该电路中采用位号为U9和U10的型号为SKYA21001射频开关芯片、位号为T1的型号为TCM2-43X+的巴伦、位号为U11的型号为TRF37C75的射频放大器组合而成;其中,U9对应第一开关231,U10对应第二开关232。射频开关U9的5号引脚与可编程射频收发集成电路1的射频输入端口相连;U9的1号引脚与射频连接器J3相连,用于接收天线端的信号;U9的5号引脚与U10的1号引脚相连,用于将发射端的信号回环至接收端,可用于系统信号的自我检测;U9和U10的4、6号引脚为高低电平切换控制端口,用于选择是5号引脚和1号引脚连通或者与3号引脚连通;U10的3号引脚与U11的2号引脚相连,U11的作用是将可编程射频收发集成电路1出来的信号进一步放大功率,经过U11的7号引脚连接至射频连接器J4,经天线端发射。T1的作用是将可编程射频收发集成电路1输出的差分为100欧姆的差分信号转换成单端50欧姆的单端信号。

接着,对可编程射频收发集成电路1的接收通道11电路模块进行介绍:

在具体实施过程中,低噪声放大电路111(LNA)是可编程射频收发集成电路1与天线相连的第一级,它起到了对天线信号进行放大的作用。控制电路13控制LNA偏置电路(LNA_BIAS)为LNA提供各项偏置,并选择输入通路。在这个过程中,通信频带内的有用信号被低噪声放大器放大,而由无线空间信道产生的噪声被放大器的增益抑制,同时放大器本身附加的噪声非常小,使得有用信号被放大的同时并不影响其质量。无线空间信道传来的各类干扰将产生信号交调量,这部分干扰将由放大器良好的线性性能抑制。

本申请实施例低噪声放大电路设计组合了噪声消除技术与多场效应复用技术(Multi-gated Transistor,MGTR),在噪声消除结构的后级采用了MGTR形式的缓冲器,从而解决LNA的阻抗匹配、低噪声、高线性度、阻抗平衡、高增益等特性间的折中问题。在靠前级的匹配放大级,采用噪声消除结构,在实现宽带阻抗匹配的同时确保了第一级噪声的最小化,从而提升整体LNA的噪声性能;在靠后级的增益提升级,采用了多晶体管复用结构,由于其是一种对称性结构,其差分端的输出阻抗是平衡的。这种结构在提升整体增益的同时,消除了增益提升带来的非线性。与此同时,由于弱反型的晶体管处于LNA的后一级,其引入的噪声是可以忽略不计的。从整体上看,这样的技术方案有效的提升了LNA电路的噪声性能、增益性能,同时并没有恶化其线性性能。

在具体实施过程中,本申请接收通道11第一混频放大电路112采用了高线性度有源下混频器,是基于多场效应复用技术(Multi-gated Transistor,MGTR)的有源混频器,在传统的吉尔伯特双平衡混频器的输入全差分对管上并行接入了两对工作在弱反型区的补偿晶体管,使得有源混频器在提供一定信号增益的同时可以消除三阶非线性,从而使IIP3可以达到0以上。

在具体实施过程中,为了提高电路集成度、缩减电路面积,第一频率合成电路115和第二频率合成电路125为同一电路,用于产生下混频或上混频本振信号。在本申请实施例中,频率合成器具有宽频带快速锁定的特性,结构为小数型电荷泵结构。请参考图3,环路主要由鉴频鉴相器(PHASE FREQUENCY DETECTOR),电荷泵(CHARGE PUMP),压控振荡器(VCO),分频器(N COUNTER),输出级(OUTPUT STAGE)以及片外滤波器组成。为了应用中时钟便利化和灵活化,通过CLK_SLE信号选择参考时钟供给方式:晶振输入(XIN)或者外部时钟输入(CIN)。同时通过端口XOUT检测输入时钟信号是否正常。频率合成电路115、125中所有信号均通过控制电路13的数字SPI控制。环路工作时,鉴频鉴相器比较输入参考信号和分频器输出信号的频率和相位,同时鉴频鉴相器输出控制信号控制电荷泵的输出电流,如果参考信号超前分频信号,那么电荷泵给外部环路滤波器充电,反之则放电,环路滤波器对输出电流进行滤波后得到一个直流控制电压,来调整VCO的振荡频率,通过调整分频信号的频率和相位使分频信号和参考信号同频同相。

在具体实施过程中,接收通道11设置的第一低通滤波电路113为带宽可调有源低通滤波器,图4为第一低通滤波电路113的结构图,采用五阶的BUTTERWORTH无源低通滤波器为模型,通过Gm_C单元模拟电感,搭建有源的Butterworth低通滤波器,通过改变流过Gm_C单元的电流大小来改变Gm_C单元的跨导值,从而改变电感值,实现改变滤波器截止频率的功能。第一低通滤波电路113的输出设计了缓冲器BUF,起到阻抗转换作用,提升其在接收链路接口的驱动力。

模数转换电路114包含两个独立的I、Q通路,每个通路为一个流水线ADC。子ADC采用2.5bit/stage结构,主要包括以下单元:输入缓冲器、前端采样保持电路、Pipeline ADC电路、数字延迟单元和数字纠错电路,以及参考电路、时钟电路、数字编码电路、输出复用电路等。控制电路13用来控制每个通路的工作状态,主要有使能控制、参考电源选择、内部偏置电流调节、内部参考电压调节等。在具体实施过程中,请参考图5,任一接收通道11还包括:设置在第一低通滤波电路113和模数转换电路114之间的第一可变增益放大器116,用于可配置调节接收链路的信号增益。进一步,第一可变增益放大器116包括:一级增益放大细调电路和多级增益放大粗调电路。

在本申请实施例中,第一可变增益放大器116增益动态范围为96dB,步进为1dB,选择7位数字控制信号。将7位控制信号分为低4位和高3位两部分,低4位控制以1dB步进的细调电路16dB的增益范围,高3位控制两个32dB和一个16dB的粗调电路。在一具体实施方式中,第一可变增益放大器116由八级放大器组成,在任一相邻两个放大器之间设置有缓冲电路,用于减小输出阻抗,增大驱动能力。为实现增益可调,在各级放大器电路设置与其并行的旁路开关,根据具体放大需求,控制电路13选择性控制各旁路开关的开与关,实现功耗的优化。

接着,对可编程射频收发集成电路1的发射通道12电路模块进行介绍:

数模转换电路121,采用的是分段式电流舵型DAC,包括:时钟产生模块、输入数据锁存模块、同步锁存模块、开关驱动电路、基准源电路、偏置电路等。控制电路13用来控制每个通路的工作状态,主要有使能控制、参考电源选择、内部偏置电流调节、内部参考电压调节等。在本申请实施例中,由于发射及接收链路对中频信号的带宽要求一致,发射通道12的第二低通滤波电路122与接收通道11的第一低通滤波电路122的结构设计完全相同,这里不再一一赘述。

在具体实施过程中,请参考图6,任一发射通道12还包括:设置在第二低通滤波电路122和第二混频放大电路123之间的第二可变增益放大器126,用于可配置调节发射链路的信号增益。第二可变增益放大器126包括:一级增益放大细调电路和多级增益放大粗调电路。可综合考虑放大倍数、带宽以及其他因素,以确定第二可变增益放大器126的放大器电路的级数。在本申请一具体实施方式中,选定第二可变增益放大器126的放大器的级数为5级。如图7所示,第二可变增益放大器126主要由细调电路(第一级TVGA_FINE为细调电路)和粗调电路组成(第二级到第五级TVGA_FIXED全为粗调电路)。细调电路的增益范围-7dB~8dB,调节步进为1dB。粗调电路的增益可选择为-2dB或14dB。第二可变增益放大器126通过细调电路实现增益以1dB步进改变,随着增益的增加,粗调电路TVGA_FIXED将依次由-2dB模式切换至14dB模式,由此实现了-21.0dB~51.5dB范围内增益连续可调。第二可变增益放大器126的输入及输出端添加了输入及输出Buffer,实现驱动力增强及阻抗转换的作用。由于中频放大器之前的混频器输出带有较大的直流失调,会影响电路的动态范围,因此放大器中需加入直流消除电路(DCOC,DC offset cancellation)。

进一步,在发射通道12中,第二混频放大电路123用于上混频,一般的做法是引入无源混频器以提供优良的线性度性能。但无源混频器的开关对产生的闪烁噪声将对链路的EVM产生较大影响。在本申请实施例中,引入了折叠式有源上混频器,其具有以下特点:

(1)在输入跨导级,使用电流复用结构,最大化了输入跨导;

(2)输入自偏置,无需要额外的偏置电路;

(3)同时采用了两条增益支路,增强增益同时消弱前级电路的相位差。

在具体实施过程中,在发射通道12中,功率放大器电路124,包括高频段和低频段两路子PA,高频段PA(1.2GHz-2.5GHz)采用片上匹配网络、低频段PA(0.045GHz-1.2GHz)采用片外匹配网络;PA的所有控制信号通过控制电路13的SPI接口输入。

另外,在具体实施过程中,仍请参考图2A,射频收发电路还包括:与可编程射频收发集成电路1连接的时钟电路3,用于为可编程射频收发集成电路1提供时钟参考信号,以使频率合成电路能够正常工作。

综上所述,本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

1)射频收发电路包括:可编程射频收发集成电路;可编程射频收发集成电路包括:至少一个接收通道、至少一个发射通道和控制电路;所述控制电路用于控制任一接收通道和任一发射通道的信号传输;其中,任一接收通道和任一发射通道中多个电路设置有可编程接口,用于接收所述控制电路的配置信号。实现了可编程控制收发集成电路,具有灵活的可配置性,通过配置能够使得射频信号中心频率覆盖MHz级别至GHz级别的频率范围,支持TDD和FDD工作模式,通道带宽可调谐,满足不同通信标准的射频收发要求。

2)本发明射频前端电路设置有射频开关单元,设置在接收链路的第一开关和设置在发射链路的第二开关可选择连通,且在二者连通时所述射频收发电路进入通信链路回环自检模式。

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例做出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 一种射频收发开关电路、射频前端电路及射频收发机

- 一种射频收发开关电路、射频前端电路及射频收发机