用于准备跟踪数据的系统和方法

文献发布时间:2023-06-19 19:33:46

技术领域

本发明总体涉及用于提供跟踪数据的系统和方法。

背景技术

追踪针对片上系统或其他设备的组件的处理步骤往往是有利的。然而,捕获跟踪数据可能严重占用系统的资源,从而给生成综合数据带来许多挑战。需要能更有效地提供跟踪数据的系统、设备和方法,以满足准备综合数据准备的需求。

发明内容

根据实施例,一种用于提供经过滤的跟踪数据的系统包括:处理器;静态随机存取存储器(SRAM)控制器;第一数据准备电路,与处理器耦接以接收来自处理器的被跟踪存储器写入数据,该第一数据准备电路被配置为从被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据;第二数据准备电路,与SRAM控制器耦接以接收来自SRAM控制器的被跟踪存储器写入数据,该第二数据准备电路被配置为从被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据;数据收集网络,被配置为从第一数据准备电路接收被选择的被跟踪存储器写入数据,并从第二数据准备电路接收被选择的被跟踪存储器写入数据;以及输出接口,与数据收集网络耦接以输出来自第一数据准备电路的被选择的被跟踪存储器写入数据和来自第二数据准备电路的被选择的被跟踪存储器写入数据。

根据实施例,系统还包括,其中处理器包括紧密耦接存储器,并且来自处理器的被跟踪存储器写入数据与针对紧密耦接存储器的存储器写入数据操作相对应。

根据实施例,系统还包括,其中SRAM控制器与对应的处理器或非处理器主机通信,并且来自SRAM控制器的被跟踪存储器写入数据针对由处理器或非处理器主机访问的存储器的存储器写入数据操作相对应。

根据实施例,系统还包括,其中来自处理器的被跟踪存储器写入数据包括寻址位、数据位和控制位,并且来自SRAM控制器的被跟踪存储器写入数据包括寻址位、数据位和控制位。

根据实施例,该系统还包括,其中第一数据准备电路被配置为基于被选择的存储器位置的映射来标识来自处理器的被跟踪存储器写入数据的被选择的被跟踪存储器写入数据。

根据实施例,该系统还包括,其中第二数据准备电路被配置为基于被选择的存储器位置的映射来标识来自SRAM控制器的被跟踪存储器写入数据的被选择的存储器写入数据。

根据实施例,该系统还包括,其中第一数据准备电路包括:过滤电路,用于从被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据;以及先进先出缓冲器,用于存储被选择的被跟踪存储器写入数据。

根据实施例,该系统还包括,其中第一数据准备电路被配置为响应于先进先出缓冲器达到满容量而使被提供到处理器的背压信号生效。

根据实施例,系统还包括,其中第一数据准备电路包括数据压缩电路,该数据压缩电路被配置为标识被选择的被跟踪存储器写入数据的数据包,并向第一数据准备电路的数据封装电路提供封装数据,以将被选择的被跟踪存储器写入数据归组到具有地址和控制信息的数据包中。

根据实施例,系统还包括,其中第一数据准备电路还包括时间戳电路,该时间戳电路被配置为向数据包添加时间戳。

根据实施例,该系统还包括与数据封装电路耦接的探寻(trace-out)控制器,该探寻控制器用于接收数据包并将其提供给数据收集网络。

根据实施例,一种用于过滤跟踪数据的方法包括:接收被跟踪存储器写入数据;标识被选择的存储器写入数据;将被选择的存储器写入数据封装到数据包中;以及将数据包输出到开发工具。

根据实施例,该方法还包括将数据包转换成用于输出的标准格式。

根据实施例,该方法还包括,其中标识被选择的被跟踪存储器写入数据包括选择针对被选择的存储器位置的存储器写入数据。

根据实施例,该方法还包括,其中被跟踪存储器写入数据包括地址位、数据位和控制位。

根据实施例,该方法还包括,其中被选择的存储器写入数据被封装成具有控制字节的数据包。

根据实施例,该方法还包括,分析被选择的存储器写入数据以确定如何封装被选择的存储器写入数据。

根据实施例,该方法还包括,其中分析被选择的存储器写入数据包括确定被选择的存储器写入数据是否与指向连续地址、指向不连续地址以及属于相同类型的存储器写入数据操作相对应。

根据实施例,一种跟踪数据准备电路,包括:过滤电路,被配置为接收被跟踪存储器写入数据;先进先出缓冲器,与过滤电路耦接以接收由过滤电路过滤的被选择的存储器写入数据;数据压缩电路,与先进先出缓冲器耦接,被配置为基于被选择的存储器写入数据的内容来提供封装数据;封装电路,被配置为基于封装数据将被选择的存储器写入数据归组到数据包中;以及输出控制器,被配置为从封装电路接收数据包并将数据包转换成标准协议格式。

根据实施例,跟踪数据准备电路包括时间戳电路,该时间戳电路被配置为将时间戳添加到每第n个数据包,n是整数。

根据实施例,跟踪数据准备电路还包括,其中用于封装电路的输出总线被配置为每周期比用于封装电路的输入总线发送更多的位。

根据实施例,跟踪数据准备电路还包括,其中由过滤电路接收到的被跟踪存储器写入数据包括寻址位、数据位和控制位。

根据实施例,跟踪数据准备电路还包括,其中过滤电路包括用于接收寻址位的地址输入、用于接收数据位的数据输入、用于接收控制位的控制输入、用于提供寻址位的寻址输出、用于提供数据位的数据输出以及用于提供控制位的控制输出。

根据实施例,跟踪数据准备电路还包括用于接收来自过滤电路的寻址位、来自过滤电路的数据位以及来自过滤电路的控制位的级联电路,该级联电路被配置为级联寻址位、数据位和控制位,并将它们提供给先进先出缓冲器。

附图说明

为了更完整地理解本发明及其优点,现在对结合附图的以下描述进行参考,其中:

图1描绘了与实施例一致的提供经过滤的跟踪数据的系统;

图2描绘了与实施例一致的提供经过滤的跟踪数据的系统;

图3描绘了与实施例一致的跟踪数据准备电路;以及

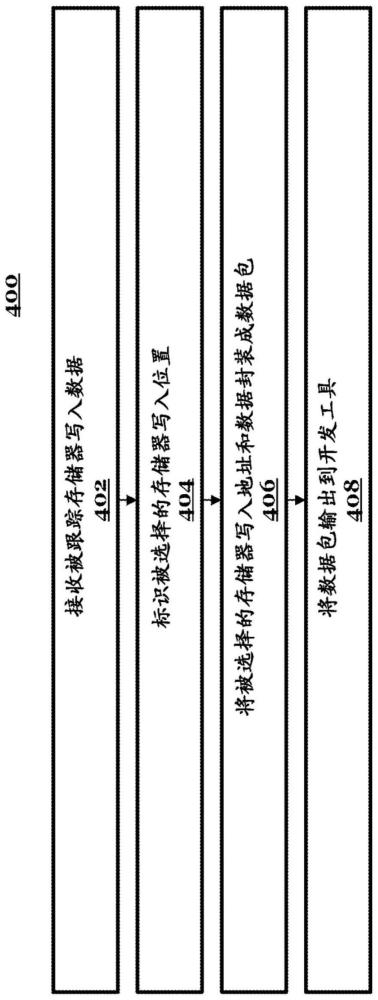

图4描绘了与实施例一致的提供经过滤的跟踪数据的方法的流程图。

具体实施方式

片上系统(“SoC”)被用于各种各样的应用中。在SoC的生命周期的不同阶段,使用外部工具测试其性能可能是有利的。这种测试可能针对许多不同类型的过程而发生,包括但不限于校准、诊断和开发。外部工具可以被用于跟踪在SoC执行功能时的操作期间在内部发生的不同执行步骤。使用此信息,设计者可以发现可能对执行产生不利影响的潜在问题。因此,数据跟踪可以向设计者、技术人员或其他人提供了解SoC的内部操作的窗口,这有助于设计者、技术人员或其他人改进、调试、校准或修复潜在问题。

举例来说,将来自SoC的跟踪数据与其他外部信息同步以获得对潜在问题的看法可能是有益的。例如,跟踪日期可以结合视觉数据使用,以诊断或校准机动车中的停车辅助操作。跟踪数据可以与执行停车动作的目标车辆的传感器数据或视频数据相对应。可以将从SoC接收到的跟踪数据与传感器和视频数据同步,以跟踪现实世界的刺激以及SoC对该刺激的反应。该数据可以有助于开发、校准或故障排除。

提供给外部工具的跟踪数据可以有利地包括由SoC内部的系统软件所更新的实时数据。系统软件应用可以同时在SoC内部的多个核上运行。这些核可以在操作被执行时连续地更新系统存储器映射的许多地址位置处的数据。例如,这些位置可以是紧密耦接存储器或系统RAM。

为了数据跟踪,针对这些位置的存储器写入地址和数据信息可以被跟踪并被提供给外部工具,以跟踪处理器和非处理器功能块的操作。然后,由于存储器位置的值被更新以运行提供关于系统行为的信息的本地算法,外部工具可以使用具有地址和控制信息的被跟踪存储器写入数据来跟踪它们。然后,这可以被分析以用于执行。写入数据也可以由其他非CPU主机(诸如直接存储器存取存储装置)来生成。跟踪针对这些位置的存储器写入数据并向外部工具提供被跟踪存储器写入数据也可能是有利的。

正如应该了解的那样,由SoC执行的操作的数量所造成的数据量可以迅速成为跟踪数据收集工作的负担。许多SoC可能同时在多个核上运行写入到大量的存储器位置的多个软件应用。同时,多个非CPU主机(诸如DMA控制器)也可以执行写入操作。由SoC执行的大量操作可能会使试图捕获跟踪数据的系统不堪重负。在一些情况下,这可能致使数据溢出,并且关键跟踪数据可能会丢失。

在许多应用中,丢失的跟踪数据严重阻碍了评估跟踪信息的努力。例如,在开发电动汽车、混合动力汽车和传统汽油汽车时,对测量内部电子控制单元信号的仪器的要求非常高。正如对综合跟踪数据的需求一样。没有综合数据,诊断或校准操作可能是不成功或不准确的。对综合跟踪数据的需求也适用于汽车的许多或所有主要应用领域,包括但不限于汽车发动机控制、车身和底盘以及其他领域(如高级驾驶辅助系统)。除汽车行业之外的许多领域也受益于用于测量运行时间以提供跟踪数据的综合数据。

跟踪数据准备的已知方法在跟踪数据被递送给外部工具之前几乎没有对其进行过滤。SoC可能同时在多个核上运行多个程序,并利用多个非CPU主机进行写入。然而,外部工具可能只对在特定时间处在SoC上发生的一些进程感兴趣。因此,虽然可能需要针对一些存储器位置的综合数据,但是外部工具可能永远不会使用与SoC上存在的许多(即使不是大多数)紧密耦接存储器(“TCM”)和片上静态随机存取存储器(“SRAM”)的更新相关的跟踪数据。通过根据具体的数据需求定制跟踪数据收集,准备跟踪数据的系统可以(在速度和操作的硬件要求方面)以被改进的可靠性和被改进的效率提供综合数据。

可以利用这一点来提供用于提供跟踪数据的更有效的系统和方法。不想要的数据可以被滤除,并且更多资源可以被专门用于从感兴趣的位置收集更加综合的数据。因此,可以通过如下操作来改进数据跟踪:允许进行高粒度过滤以便仅选择期望的数据位置来探寻。

这在包括但不限于汽车领域的广泛领域中是有益的。例如,汽车应用的仪表要求可以从收集由系统软件写入到系统中存储器(in-system memories)中的更新后的数据中受益。在许多情况下,需要从被选择的存储器位置中获得所有综合数据。但是,可能不需要与其他存储器位置相关的更新。为了满足这一要求,与本公开一致的实施例允许对于来自被选择的存储器位置的综合数据进行细粒度过滤,以便从提供给外部工具的数据中移除不想要的存储器写入数据。此外,数据压缩和数据包化也可以增强数据跟踪系统和方法。

图1描绘了与实施例一致的提供经过滤的跟踪数据的系统。

提供经过滤的跟踪数据的系统100可以被包含在片上系统上。在各种实施例中,用于提供经过滤的跟踪数据的系统100可以包括处理器102。处理器102可以被配置为执行存储在存储器(未示出)中的软件指令。在执行期间,处理器可以向存储器位置写入。处理器可以包括紧密耦接(TCM)存储器101。

用于TCM存储器(或其他存储器位置)的存储器写入数据、地址和控制信息可以包括寻址位、数据位和控制位。这些信息中的每一个都可以被携载在单独的总线上。而且,正如应当了解的那样,针对每条的位数在不同的实施例中可能会有所不同。系统还可以包括SRAM控制器104(静态随机存取存储器控制器)。SRAM控制器也可以处理有利于捕获用于数据被跟踪存储器写入数据。这样的存储器写入数据还可以包括可以在单独的总线上携载的寻址位、数据位和控制位。

在各种实施例中,第一数据准备电路106可以与处理器102耦接以接收来自处理器102的被跟踪存储器写入数据。被跟踪存储器写入数据可以包括用于写入到处理器102的TCM存储器101的数据。可以向第一数据准备电路106提供重复的写入数据。

在各种实施例中,递送携载存储器写入数据的信号的一个或多个总线可以与第一数据准备电路106耦接以接收存储器写入数据。处理器102和第一数据准备电路106之间的通信可以使用存储器写入数据端口接口111A来完成,存储器写入数据端口接口111A为诸如但不限于存储器重建端口(“MRP”),其在ARM Cortex处理器和系统中存储器控制器中可用。在各种实施例中,数据端口接口111A可以被集成到处理器102中。写入数据存储器端口接口可以经由地址总线、数据总线和控制总线来提供各种信号。由数据准备电路接收的存储器写入数据可以被称为被跟踪存储器写入数据。

在各种实施例中,第一数据准备电路106可以在其管道被填充并且其不能处理来自处理器102的更多数据时,提供背压信号。在各种实施例中,存储器写入数据端口接口111A可以向第一数据准备电路106提供用于处理器102的TCM存储器101的写入数据。

在各种实施例中,第一数据准备电路106可以执行过滤操作以滤除在被选择的地址位置处的一些被跟踪存储器写入数据。这可能有利于限制最终被提供给外部工具的数据,并减少跟踪操作所需的带宽。在各种实施例中,第一数据准备电路106可以被配置为从针对被选择的地址位置的存储器写入操作相对应的被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据,该未被选择的被跟踪存储器写入数据对应于针对未被选择的存储器位置的存储器写入操作。在各种实施例中,只有针对被选择的位置的被跟踪存储器写入数据将由第一数据准备电路106传递。

在各种实施例中,系统100可以包括附加数据准备电路。附加数据准备电路可以与生成存储器写入数据的附加源耦接。并且,系统可以包括附加存储器写入数据端口接口(诸如MRP,但不限于此)。附加存储器写入数据端口接口可以操作为存储器写入数据端口接口111A。并且,附加数据准备电路也可以进行操作以对它们所接收的存储器写入数据进行过滤。

作为示例,系统100可以包括与SRAM控制器104耦接的第二数据准备电路108。第二数据准备电路108可以从SRAM控制器104接收被跟踪存储器写入数据。可以包括MRP的存储器写入数据端口接口111B可以将被跟踪存储器写入数据从SRAM控制器104携载到第二数据准备电路108。

第二数据准备电路108可以被配置为从被选择的被跟踪存储器写入位置滤除未被选择的被跟踪存储器写入数据。在各种实施例中,选择可以由打算用于存储器写入数据的存储器位置来确定。针对被选择的存储器位置的存储器写入数据可以由第二数据准备电路108传递,而针对其他存储器位置的存储器写入数据不被传递。在各种实施例中,SRAM控制器104和第二数据准备电路108之间的耦接可以使用数据端口接口111B来完成,该数据端口接口111B可以包括MRP。

在各种实施例中,系统100还可以包括数据收集网络110,其被配置为从第一数据准备电路106接收被选择的被跟踪存储器写入数据,并且从第二数据准备电路108接收被选择的被跟踪存储器写入数据。数据收集网络110可以包括分散在整个SoC的组件。在各种实施例中,数据收集网络可以包括存储器以存储被选择的存储器写入数据。

系统100还可以包括与数据收集网络110耦接的输出接口112,以输出来自第一数据准备电路106的被选择的存储器写入数据以及输出来自第二数据准备电路108的被选择的存储器写入数据。输出接口112可以包括高速串行探寻控制器接口。高速串行跟踪数据可以被提供给外部开发工具,该外部开发工具可以包括测量硬件基础模块114以及测量和校准工具116。

处理器102可以包括TCM存储器101,并且来自处理器102的被跟踪存储器写入数据可以根据针对TCM存储器101的存储器写入数据而被跟踪。TCM存储器可以包括具有与核的专用连接的低延迟存储器。在各种实施例中,数据准备电路可以接收针对除TCM存储器之外,或代替TCM存储器的其他类型的存储器的存储器写入数据。

在各种实施例中,SRAM控制器104与直接存储器存取电路通信,并且来自SRAM控制器104的被跟踪存储器写入数据根据针对直接存储器存取电路可访问的存储器的存储器写入数据而被跟踪。来自SRAM控制器104的被跟踪存储器写入数据可以包括寻址位、数据位和控制位。正如应当了解的那样,这些可以分别被携载在寻址总线、数据总线和控制总线上。

在各种实施例中,第一数据准备电路106被配置为基于被选择的存储器位置的映射来标识来自处理器102的被跟踪存储器写入数据的被选择的存储器写入位置。例如,TCM存储器101的每个存储器位置可以被映射到单个位。如果该位具有传递设置(其在不同的实施例中可以是高或低),则针对该地址位置的存储器写入数据可以由第一数据准备电路106传递。如果对应于给定存储器位置的位不具有传递设置,那么针对该存储器位置的存储器写入数据可能不会被传递。

正如应当了解的那样,其他数据准备电路(诸如第二数据准备电路108)可以以类似的方式操作。针对数据准备电路的映射可以与由耦接到数据准备电路的源可访问的存储器位置相对应。例如,在各种实施例中,第二数据准备电路108可以被配置为基于被选择的存储器位置的映射来标识从SRAM控制器104接收到的被跟踪存储器写入数据的被选择的存储器写入位置。该映射可以与SRAM可访问的存储器位置相对应,以用于写入指示是否传递打算用于该位置的存储器写入数据的过滤位。

在各种实施例中,映射可由外部工具编程。这可以允许根据与系统100耦接的外部工具来调整映射。因此,外部工具可以选择哪些存储器位置与它的目的相关,因此只有相关的存储器写入位置最终被传递给外部工具。通过向外部提供跟踪数据的总线系统,外部工具可以访问能够被存储在系统100的存储器中的映射。

还应当了解的是,映射提供的只是对由数据准备电路接收到的被跟踪存储器写入数据进行过滤的一种可能的方式。数据准备电路可以使用其他方式来滤除未被选择的存储器写入位置数据,并传递被选择的存储器写入数据。一个这样的附加示例是一组寄存器。可编程寄存器可以被用于过滤位置的编程。也可以利用另外的过滤方法。

图2描绘了与实施例一致的提供经过滤的跟踪数据的系统。

系统200包括附加数据准备电路。除非另外指出,否则在本公开中以相同的附图标记指明的特征可以包括在本公开中以相同的附图标记确定的相同特征。系统200可以包括第三存储写入源103和第四存储写入源105。正如应当了解的那样,附加源可以包括附加核,其可以包括附加的紧密耦接存储器(在图2中未描绘)。

附加源还可以包括附加SRAM控制器或其他存储器写入源。作为示例,第三存储器写入源103可以包括处理器。第四存储器写入源105可以包括SRAM控制器。被跟踪存储器写入数据可以包括寻址位、数据位和控制位,它们可以在单独的总线上被携载。

第三存储器写入源103可以通过存储器端口接口111C(诸如MRP)与第三数据准备电路107耦接。并且,第四存储器写入源105可以通过存储器写入数据端口接口111D(诸如MRP)与第四数据准备电路109耦接。第三数据准备电路107可以被配置为从第三存储器写入源103接收到的被选择的存储器写入位置过滤从第三存储器写入源103接收到的未被选择的存储器写入位置。

第四数据准备电路109可以被配置为从第四存储器写入源105接收到的被选择的存储器写入位置过滤从第四存储器写入源105接收到的未被选择的存储器写入位置。

由第三数据准备电路107进行的过滤可以通过用于写入的第三存储器写入源103可访问的存储器位置的映射来完成。与存储器位置相对应的位可以被设置以存储对应于传递值的设置,该设置可以包括取决于实施例的高设置或低设置。其对应位具有传递设置的存储器位置的写入数据可以由第三数据准备电路107传递。并且,其对应位不具有通过设置的存储器位置不被传递。

类似地,由第四数据准备电路109进行的过滤可以通过用于写入的第四存储器写入源105可访问的存储器位置的映射来完成。与存储器位置相对应的位可以被设置以存储对应于传递值的设置,该设置可以包括取决于实施例的高设置或低设置。其对应位具有传递设置的存储器位置的写入数据可以由第四数据准备电路109传递。并且,其对应位不具有传递设置的存储器位置不被传递。

图3描绘了与实施例一致的数据准备电路。

跟踪数据准备电路300可以包括过滤电路302,该过滤电路被配置为接收具有寻址数据的被跟踪存储器写入数据。在各种实施例中,过滤电路302可以被编程以过滤32/64位的范围内的(多个)地址位置或最多单个地址位置。在各种实施例中,只有期望的位置数据从该阶段被传递到下一个阶段。

过滤电路302可以允许跟踪数据准备电路300仅选择外部测量工具进行分析可能需要的期望数据。这进而允许跟踪数据准备电路300减少跟踪数据带宽,并通过减少测量工具的软件或硬件中的过滤而降低整个仪器系统的复杂性。

过滤电路302可以取决于针对存储器写入操作的预期目的地而对被跟踪存储器写入数据进行过滤。例如,跟踪电路可以利用映射,该映射将存储器写入数据的源可访问的存储器位置与指示是否针对该位置传递存储器写入数据的位相对应。映射示例已经参照图1和图2进行了描述,因此为了简洁起见,在这里将不再重复。不是映射或者除了映射之外,还可以利用其他过滤方法。

基于针对存储器写入位置的所指明的目标位置的过滤允许过滤电路302传递针对被选择的位置的所有存储器写入数据,同时剔除不想要的信息。在各种实施例中,外部工具可以对感兴趣的位置进行编程,从而控制其获得的信息。

在各种实施例中,过滤电路302可以包括用于接收被跟踪存储器写入位置的寻址位的寻址接口302A、用于接收被跟踪存储器写入数据的数据位的数据接口302B以及用于接收存储器写入数据的控制位的控制接口302C。在各种实施例中,存储器端口接口可以包括寻址接口、数据接口和控制接口。

过滤电路302可以包括用于输出被选择的被跟踪存储器写入位置的寻址位的寻址输出接口302D、用于输出被选择的被跟踪存储器写入数据的数据位的数据输出接口302E以及用于输出被选择的存储器写入数据的控制位的控制输出接口302F。输出接口302D、数据输出接口302E和控制输出接口302F可以被用来在由过滤电路302接收到的被跟踪存储器写入数据已被过滤之后输出结果。

跟踪数据准备电路300还可以包括输出302G,以向存储器写入数据的源(诸如处理器102或SRAM控制器104)提供反压信号。在各种实施例中,输出302G可以内部地与FIFO数据存储装置306(先进先出数据存储装置)耦接。

在各种实施例中,跟踪数据准备电路300可以包括级联电路304,用于级联从过滤电路302接收到的被选择的存储器写入数据的寻址位、数据位和控制位。合并这一数据以用于存储到FIFO数据存储装置306中可能是有益的。在各种实施例中,FIFO数据存储装置306可以在每个时钟周期输出一个被跟踪存储器写入数据集。

跟踪数据准备电路300还可以包括FIFO数据存储装置306。FIFO数据存储装置306可以与过滤电路302耦接以在过滤电路302从未被选择的存储器写入位置对数据进行过滤之后接收被选择的存储器写入数据。在各种实施例中,级联电路304可以耦接在过滤电路302和FIFO数据存储装置306之间。FIFO数据存储装置306可能有利于减少背压信号的频率。将背压信号设置为在期望电平处被触发可以允许核和系统中存储器控制器透明地工作。例如,当FIFO数据存储装置306达到阈值容量时,背压信号可以被生效。背压信号可以基于FIFO填充水平来设置。

用于生效背压信号的阈值容量在各种实施例中可能不同,并且它可能取决于系统100的其他能力。例如,具有较快处理器的SoC可能需要比具有较慢处理器的系统更早地使背压生效。正如应当了解的那样,FIFO数据存储装置306的大小以及其他因素也可能影响何时使背压信号生效或者背压信号的生效的被选择的容量水平。

在各种实施例中,背压信号的生效可能使提供存储器写入数据的源的操作停滞。这对于关键是即使牺牲速度也要获取综合数据收集的实施例可能是真实的。然而,如上面所提及,触发背压信号的事件可以进行挑选,以将需要背压信号的时间最小化。

在各种实施例中,跟踪数据准备电路300可以包括与FIFO数据存储装置306耦接的数据压缩电路308。数据压缩电路308可以基于从FIFO数据存储装置306接收到的被选择的存储器写入数据的内容来提供封装地址和数据。数据压缩电路308可以检查从FIFO数据存储装置306接收到的被选择的存储器写入数据,以确定数据可以如何被压缩和封装。

仅举几个示例,数据压缩电路308可以将传入的被跟踪的存储器写入地址与由数据压缩电路308接收到的先前被跟踪的存储器写入地址进行比较。如果这两个地址指向同一个存储器位置,则它们可以被标记为在一个数据包中被归组在一起。如果这两个地址是指向连续的存储器位置,则它们可以被标记以进行归组。前述每个示例可以通过比较当前周期的被跟踪存储器写入数据的寻址数据(诸如寻址位)与前一周期的寻址数据来完成。

在另一个示例中,如果两个写入数据集是相同的类型(诸如对齐的双字、半字),则它们可以被标记以进行归组。这可以通过比较来自当前周期的被跟踪存储器写入数据的控制数据与来自前一周期的存储器写入数据的控制来进行检查。

应当了解的是,也可以为可能存在潜在数据包机会的各种其他组合而检查由数据压缩电路308接收到的被跟踪存储器写入数据。在各种实施例中,可能有超过100个组合被检查以标识压缩机会。基于检测到的组合,数据压缩电路308可以向封装电路310提供信息,以将输入数据背靠背封装到更宽宽度的输出数据总线中。这一原则进而可以减少由输出传送跟踪数据的时钟周期的总数。这可以节省输出带宽。压缩可以节省输出带宽,因为它决定输入数据在更宽宽度的输出数据总线中的封装顺序。

封装也可以允许从供应给外部工具的数据中移除附加数据。控制字节和地址信息可以在存储器跟踪数据的单个数据包中只封装一次,以节省输出数据带宽。例如,对于为被打包在一起的相同的或连续的地址提供的一组存储器写入数据,地址数据可以只被提供一次,而不是为存储器写入数据的每个实例提供寻址数据。其他数据也可以取决于打包和压缩的情况而被移除。

封装电路310可以被配置为基于从数据压缩电路308接收到的封装信息而将被选择的存储器写入数据和地址归组到数据包中。例如,连续的被跟踪存储器写入数据可以一起被打包并输出。数据压缩电路308可以在接收到连续的存储器写入数据集时使一个信号生效。该信号可以被提供给数据封装电路,并可以指使封装电路310将最近接收到的存储器写入数据与前一周期的存储器写入数据打包。只要该信号从数据压缩电路308生效,封装电路310就可以继续将随后接收到的存储器写入数据进行归组。一旦,该信号被失效,封装电路310可以输出当前数据包。

对于被标识以进行归组的其他周期的被跟踪存储器写入数据,可以遵循类似的程序。当可组合的地址和数据被标识时,数据压缩电路308可以使一个信号生效。封装电路310可以将这些地址和数据打包在一起,直到该信号被失效。

封装电路310可以从数据压缩电路308接受输入,并将连续和对齐的数据背靠背与控制字节和地址信息一起封装。封装电路310的输出总线310A的宽度可以比数据压缩电路308的输出总线308A的宽度大。这可以允许从数据封装电路输出带有地址的被跟踪存储器写入数据的数据包,而不是一次输出对应于一个写入操作的数据。

在各种实施例中,可能花费输出总线310A的一个以上的输出周期来输出被跟踪存储器写入数据数据包。例如,如果连续的存储器写入数据的一个数据包填充输出总线310A,第一周期可以输出存储器写入数据的第一部分,并且第二周期可以输出同一数据包的附加存储器写入数据。对于整个数据包,寻址信息可能只需要输出一次。附加的周期也可以被利用,直到指示可组合数据被标识的信号被失效。类似地,如果该信号在总线满了之前被失效,则可以在总线的所有位被数据填充的情况下进行输出。

在各种实施例中,跟踪数据准备电路300还可以包括输出控制器312,其被配置为从封装电路接收数据包并将数据包转换成标准协议格式。输出控制器可以接收封装数据并将其提供给SoC的跟踪下游基础设施(诸如数据收集网络110)。它可以利用标准接口协议,如ARM的高级跟踪总线(ATB)。探寻数据可以在探寻数据输出312A处被输出,并且探寻控制数据可以在探寻控制输出312B处被输出。控制输出312B可以提供控制数据,该控制数据可以由接收跟踪数据的从机进行解码以进一步处理。

跟踪数据准备电路300还可以包括时间戳电路314。时间戳电路314可以是可编程单元,其可以在间隔之后将时间戳数据添加到跟踪数据。例如,时间戳电路314可以对输出周期进行计数,直到达到间隔。如果间隔被设定为五个周期,则时间戳可以被添加到每第五个周期。

时间戳数据可以被外部工具用来将来自各种源的数据按时间尺度进行相关。这可能有利于跟踪写入何时发生。正如已经讨论过的,准备跟踪数据的系统可以包括许多数据准备电路,因此对输出打上时间戳可能是有利的。时间戳也可以被外部工具利用来在写入地址和数据被解封装之后对其进行排序。

时间戳之间的间隔可以是可编程的。例如,它可以由外部工具来编程。该间隔可以被存储在外部工具可访问以进行写入的存储器位置中。通信可以通过总线而从外部工具来携载。正如应当了解的那样,在系统中的数据准备电路的数量越多或者取决于外部工具的需求,减少间隔可能是有益的。

图4描绘了与实施例一致的用于提供经过滤的跟踪数据的方法的流程图。

在各种实施例中,一种用于准备经过滤的跟踪数据的方法400包括:在步骤402,接收被跟踪存储器写入数据;在步骤404,标识被选择的存储器写入位置;在步骤406,将被选择的存储器写入地址和数据封装成数据包;以及在步骤408,将数据包输出到开发工具。

在各种实施例中,方法400还可以包括将数据包转换成用于输出的标准格式。

在各种实施例中,所述方法400,其中标识被选择的存储器写入数据包括选择针对被选择的存储器位置的存储器写入地址。

在各种实施例中,所述方法400,还可以包括分析被选择的存储器写入位置以确定如何封装被选择的存储器写入数据。

在各种实施例中,方法400还可以包括,其中分析被选择的存储器写入数据包括确定存储器写入位置是否指向连续地址、指向不连续地址以及属于相同类型。

各个附图用方框图描述了电路和其他组件。这些附图不应该被视为标记了对应组件的物理边界。正如应当了解的那样,物理组件可以分散在整个SoC中。

示例1.一种用于提供经过滤的跟踪数据的系统,该系统包括:处理器;静态随机存取存储器(SRAM)控制器;第一数据准备电路,与处理器耦接以接收来自处理器的被跟踪存储器写入数据,该第一数据准备电路被配置为从被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据;第二数据准备电路,与SRAM控制器耦接以接收来自SRAM控制器的被跟踪存储器写入数据,该第二数据准备电路被配置为从被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据;数据收集网络,被配置为从第一数据准备电路接收被选择的被跟踪存储器写入数据,并从第二数据准备电路接收被选择的被跟踪存储器写入数据;以及输出接口,与数据收集网络耦接以输出来自第一数据准备电路的被选择的被跟踪存储器写入数据和来自第二数据准备电路的被选择的被跟踪存储器写入数据。

示例2.根据示例1所述的系统,其中处理器包括紧密耦接存储器,并且来自处理器的被跟踪存储器写入数据与紧密耦接存储器的存储器写入数据操作相对应。

示例3.根据示例1或示例2所述的系统,其中SRAM控制器与对应的处理器或非处理器主机通信,并且来自SRAM控制器的被跟踪存储器写入数据与针对可由处理器或非处理器主机访问的存储器的存储器写入数据操作相对应。

示例4.根据示例1至示例3所述的系统,其中来自处理器的被跟踪存储器写入数据包括寻址位、数据位和控制位,并且来自SRAM控制器的被跟踪存储器写入数据包括寻址位、数据位和控制位。

示例5.根据示例1至示例4所述的系统,其中第一数据准备电路被配置为基于被选择的存储器位置的映射来标识来自处理器的被跟踪存储器写入数据的被选择的被跟踪存储器写入数据。

示例6.根据示例1至示例5所述的系统,其中第二数据准备电路被配置为基于被选择的存储器位置的映射来标识来自SRAM控制器的被跟踪存储器写入数据的被选择的存储器写入数据。

示例7.根据示例1至示例6所述的系统,其中第一数据准备电路包括:过滤电路,用于从被选择的被跟踪存储器写入数据过滤未被选择的被跟踪存储器写入数据;以及先进先出缓冲器,用于存储被选择的被跟踪存储器写入数据。

示例8.根据示例1至示例7所述的系统,其中第一数据准备电路被配置为响应于先进先出缓冲器达到满容量而使被提供到处理器的背压信号生效。

示例9.根据示例1至示例8所述的系统,其中第一数据准备电路包括数据压缩电路,该数据压缩电路被配置为标识被选择的被跟踪存储器写入数据的数据包,并向第一数据准备电路的数据封装电路提供封装数据,以将被选择的被跟踪存储器写入数据归组到具有地址和控制信息的数据包中。

示例10.根据示例1至示例9所述的系统,其中该第一数据准备电路还包括时间戳电路,该时间戳电路,向数据包添加时间戳。

示例11.根据示例1至示例4所述的系统还包括与数据封装电路耦接的探寻控制器,该探寻控制器用于接收数据包并将其提供给数据收集网络。

示例12.一种用于过滤跟踪数据所述的方法,该方法包括:接收被跟踪存储器写入数据;标识被选择的存储器写入数据;将被选择的存储器写入数据封装到数据包中;以及将数据包输出到开发工具。

示例13.根据示例12所述的方法,还包括将数据包转换成用于输出的标准格式。

示例14.根据示例12或示例13所述的方法,其中标识被选择的被跟踪存储器写入数据包括选择针对被选择的存储器位置的存储器写入数据。

示例15.根据示例12至示例14所述的方法,其中被跟踪存储器写入数据包括地址位、数据位和控制位。

示例16.根据示例12至示例15所述的方法,其中被选择的存储器写入数据被封装到具有控制字节的数据包中。

示例17.根据示例12至示例16所述的方法,还包括分析被选择的存储器写入数据以确定如何封装被选择的存储器写入数据。

示例18.根据示例12至示例17所述的方法,其中分析被选择的存储器写入数据包括确定被选择的存储器写入数据是否与指向连续地址、指向不连续地址以及相同类型的存储器写入数据操作相对应。

示例19.一种跟踪数据准备电路,包括:过滤电路,被配置为接收被跟踪存储器写入数据;先进先出缓冲器,其与过滤电路耦接以接收由过滤电路过滤的被选择的存储器写入数据;数据压缩电路,与先进先出缓冲器耦接,被配置为基于被选择的存储器写入数据的内容来提供封装数据;封装电路,被配置为基于封装数据将被选择的存储器写入数据归组到数据包中;以及输出控制器,被配置为从封装电路接收数据包并将数据包转换成标准协议格式。

示例20.根据示例19所述的跟踪数据准备电路,还包括时间戳电路,该时间戳电路被配置为将时间戳添加到每第n个数据包,n是整数。

示例21.根据示例19或示例20所述的跟踪数据准备电路,其中用于封装电路的输出总线被配置为每周期比用于封装电路的输入总线发送更多的位。

示例22.根据示例19至示例21所述的方法,其中由过滤电路接收到的被跟踪存储器写入数据包括寻址位、数据位和控制位。

示例23.根据示例19至示例22所述的方法,其中过滤电路包括用于接收寻址位的地址输入、用于接收数据位的数据输入、用于接收控制位的控制输入、用于提供寻址位的寻址输出、用于提供数据位的数据输出以及用于提供控制位的控制输出。

示例24.根据示例19至示例23所述的方法,还包括用于接收来自过滤电路的寻址位、来自过滤电路的数据位以及来自过滤电路的控制位的级联电路,该级联电路被配置为级联寻址位、数据位和控制位,并将它们提供给先进先出缓冲器。

虽然本发明已经参照说明性实施例进行了描述,但是该描述不旨在在限制性意义上进行解释。说明性实施例的各种修改和组合以及本发明的其他实施例,对于本领域的技术人员来说,在参考该描述后将是显而易见的。因此,所附的权利要求书旨在包括任何此类修改或实施例。

- 大数据系统文件数据准备方法和系统

- 用于准备用于搜索数据库的系统的方法以及用于执行向所连接的数据源的查询的系统和方法

- 用于准备用于搜索数据库的系统的方法以及用于执行向所连接的数据源的查询的系统和方法