一种MCU访问系统

文献发布时间:2023-06-19 19:33:46

技术领域

本发明涉及计算机体系结构与处理器微结构设计的技术领域,具体涉及一种MCU访问系统。

背景技术

MCU(Microcontroller Unit,即微控制器)具有实时性高,响应迅速的特点,因此在RTOS(Real Time Operating System,即实时操作系统)中被广泛应用。但是在RTOS中,MCU访问DDR(Double Data Rate Synchronous Dynamic Random Access Memory,简称为DDR,即双倍速率同步动态随机存储器)等外部存储器时速度很慢,因此需要在MCU内嵌入专门的SRAM(Static Random Access Memory,即静态随机存取存储器)或eFlash(e是embedding的意思,可以理解为嵌入到芯片中的flash,称之为嵌入式闪存),形成嵌入式存储器(也称之为于片内存储器或内嵌存储器)进行相关指令数据的存储。

为了应对较为复杂的应用程序,需要在MCU内部嵌入大容量的SRAM和flash进行指令的执行和存储,在这一情况下,由于嵌入的SRAM和flash成本很高,所以不利于MCU的成本控制且指令执行效率低下,这样就对MCU的应用程序开发造成了很大的限制。

发明内容

本申请公开一种MCU访问系统,具体的技术方案如下:

一种MCU访问系统,MCU访问系统包括cache存储器和MCU;MCU用于通过cache存储器对DDR存储器进行访问;cache存储器与MCU连接;cache存储器和DDR存储器设置在MCU的外部;cache存储器用于以突发传输操作的方式访问DDR存储器;MCU用于以单次传输操作的方式或以突发传输操作的方式访问cache存储器。

进一步地,MCU在一个时钟周期内以目标类型传输操作的方式进行访问的情况下,从cache存储器内获取的数据的数量是大于从DDR存储器内获取的数据的数量;其中,目标类型传输操作是突发传输操作或单次传输操作;所述MCU在一个时钟周期内对所述cache存储器突发传输操作过的地址单元的数量等于所述MCU在一个时钟周期内对所述cache存储器单次传输操作过的地址单元的数量。

进一步地,所述MCU的内部不设置目标片内存储器,以使cache存储器代替目标片内存储器缓存MCU与DDR存储器之间传输的数据;其中,所述DDR存储器的容量大于所述cache存储器的容量。

进一步地,所述目标片内存储器包括嵌入式SRAM或嵌入式flash;所述目标片内存储器、所述MCU、所述cache存储器和所述DDR存储器设置在同一电路板的情况下,所述MCU不嵌入所述目标片内存储器。

进一步地,所述cache存储器包括多条缓存行;所述cache存储器,用于根据所述MCU的读请求指令,将所述DDR存储器内所存储的第一目标数据读取出来并存储到对应的缓存行中,然后通知所述MCU读取对应的缓存行中的数据,以使所述MCU索引到第一目标数据;所述cache存储器,还用于根据所述MCU的写请求指令,接收所述MCU输出的第二目标数据并存储到对应的缓存行中;其中,读请求指令是在突发传输操作下配置出来;写请求指令是在单次传输操作或突发传输操作下配置出来。

进一步地,所述MCU每次从所述cache存储器读取第一目标数据之前,依次对各条缓存行进行数据索引;若所述第一目标数据存在于当前索引的一条缓存行中,则从当前索引的一条缓存行中读取所述第一目标数据;若所述第一目标数据不存在于所述cache存储器内所有的缓存行中,则触发所述cache存储器一次性从所述DDR存储器中读取出一个突发长度的数据,并存储起来以更新掉对应缓存行中的数据,直至所述MCU从当前索引的一条缓存行中读取所述第一目标数据;其中,所述cache存储器一次性从所述DDR存储器中读取出一个突发长度的地址单元内的数据的方式是突发读操作;突发长度表示一次突发传输操作下传输的连续的地址单元的数量;所述突发传输操作是突发读操作或突发写操作。

进一步地,突发长度等于第一预设参数与缓存行长度的乘积;其中,突发长度小于或等于缓存行长度;缓存行长度是一条缓存行当中设置的连续的地址单元的数量;第一预设参数等于数值1时,所述cache存储器一次性从所述DDR存储器中读取出的数据更新掉最早被所述MCU读取的一条缓存行中全部的数据;第一预设参数小于数值1且大于数值0时,所述cache存储器一次性从所述DDR存储器中读取出的数据更新掉最早被所述MCU读取的一条缓存行中的部分数据,该部分数据占据的地址单元的数量与最早被所述MCU读取的一条缓存行所有地址单元的数量的比值是第一预设参数;其中,每个地址单元的数据存储容量相等。

进一步地,所述MCU对所述cache存储器的读操作是单次读操作或突发读操作,所述MCU对所述cache存储器的写操作是突发写操作或单次写操作;其中,单次长度表示一次所述单次传输操作下传输的连续的地址单元的数量,单次长度小于突发长度;其中,所述单次传输操作是单次读操作或单次写操作。

进一步地,在所述cache存储器中,每条缓存行中的地址单元的数量都是相等,而且,每个地址单元设置的数据位宽是相等,以使所述cache存储器由多行多列的数据块组成。

进一步地,所述cache存储器的容量是等于所述缓存行的总条数、所述缓存行长度与预设数据位宽的乘积,其中,每个地址单元存储的数据都是预设数据位宽的指令。

本申请的技术效果在于:

本申请公开的MCU与DDR存储器之间连接上专门的cache存储器,以使cache存储器代替所述目标片内存储器加入所述MCU和所述DDR存储器之间的数据通路中,cache存储器用于以突发传输操作的方式访问DDR存储器;MCU用于以单次传输操作的方式或以突发传输操作的方式访问cache存储器,使得MCU通过cache存储器从DDR存储器获取数据的速率整体上是大于直接从DDR存储器获取数据。从而通过所述cache存储器与DDR存储器的协作来保证MCU的取指操作能够快速高效地进行。

由于MCU在一个时钟周期内对所述cache存储器突发传输操作过的地址单元的数量等于MCU在一个时钟周期内对所述cache存储器单次传输操作过的地址单元的数量,以使得MCU采用突发传输操作访问所述cache存储器和采用单次传输操作的方式访问所述cache存储器在同一时钟周期内的传输过的数据的数量是一样;所以,MCU在不设置目标片内存储器的情况下通过cache存储器对DDR存储器的访问不会受到单次传输操作的影响(来源于MCU以单次传输操作的方式访问DDR存储器的效率约束)。

由于MCU在一个时钟周期内以目标类型传输操作的方式进行访问的情况下,访问所述cache存储器是快于访问所述DDR存储器;所以,在所述cache存储器预先存有所述MCU所需访问的数据的情况下,所述MCU会以突发传输操作的方式或单次传输操作的方式优先在所述cache存储器对应缓存行中查找,提高对DDR存储器的访问效率。而且,cache存储器被配置为以突发传输操作的方式访问DDR存储器且MCU被配置为以单次传输操作的方式访问cache存储器的情况下,对应产生的读写效率比内设SRAM的MCU以单次传输操作方式访问DDR存储器所产生的读写效率高。解决设置片内目标存储器的MCU以单次传输操作的方式直接访问DDR存储器存在的效率过低的问题。

附图说明

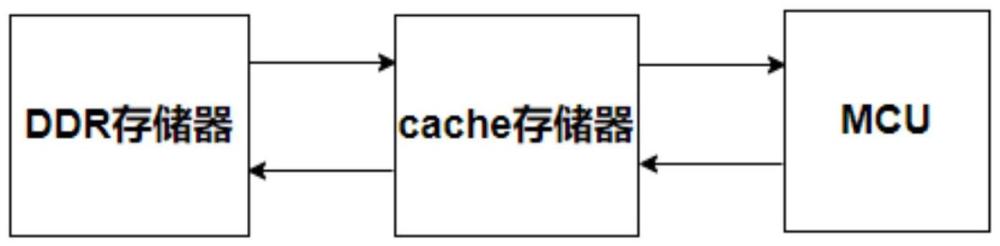

图1为一种实施例公开的MCU、cache存储器以及DDR存储器之间的连接关系示意图。

实施方式

下面结合附图对本发明的具体实施方式作进一步说明。以下实施方式中所涉及到的各模块均为逻辑电路单元,在实际应用中,一个逻辑电路单元可以是一个物理单元,也可以是一个物理单元的一部分,还可以以多个物理单元的组合实现。此外,为了突出本发明的创新部分,本发明实施方式中并没有将与解决本发明所提出的技术问题关系不太密切的单元引入,但这并不表明本发明实施方式中不存在其它的单元。

在目前的RTOS系统所依赖的嵌入式设备中,嵌入式存储器是指集成在片内且与系统中各个逻辑、混合信号等IP共同组成单一芯片中的存储器,成为SOC芯片的基本组成部分,用来存储程序和数据,克服加载RTOS系统的MCU在访问DDR等外部存储器时效率低且速度慢的问题。在配置专门的嵌入式SRAM或eFlash到MCU的内部的设计场景,随着应用程序在嵌入式存储器占用的内存增大,嵌入式SRAM或eFlash占用的面积需要增加以增大MCU的容量,导致整体设计成本提高;需要注意的是,存储容量较大的DDR存储器的价格相对便宜,尤其是作为分立式存储器件使用时比较便宜;虽然都是存储器,但二者还是有些许不同,嵌入式存储器和分立式存储器最重要的不同之处在于嵌入式存储器往往跟应用IC自身的工艺特性条件有很大关系,比如用45nm和用22nm工艺做出来的芯片,其内部嵌入式存储器大小差别也是很大的。而分立式存储器件则主要围绕存储器器件工艺进行优化。

作为一种实施例,本实施例公开一种MCU访问系统,MCU访问系统包括cache存储器和MCU;MCU访问系统用于访问DDR存储器;cache存储器、DDR存储器和MCU三者可以电气连接在同一电路实体中;MCU用于通过cache存储器对DDR存储器进行访问;其中,cache存储器和DDR存储器设置在MCU的外部;cache存储器连接在MCU和所述DDR存储器之间。cache存储器用于以突发传输操作的方式访问DDR存储器;MCU用于以单次传输操作的方式访问cache存储器。参阅图1可知,cache存储器和DDR存储器设置在MCU的外部,属于MCU的片外存储器。本实施例将MCU配置为通过cache存储器对DDR存储器进行访问,其中,MCU访问系统所需访问的DDR存储器可以是一个或多个,MCU访问系统当中的MCU,cache存储器也可以是一个或多个;而且,cache存储器连接在所述MCU和所述DDR存储器之间,以使cache存储器代替所述目标片内存储器加入所述MCU和所述DDR存储器之间的数据通路中。

如图1所示,所述DDR存储器和所述cache存储器连接,所述DDR存储器和所述cache存储器之间向右的箭头表示所述cache存储器从所述DDR存储器的接口读取数据,所述DDR存储器和所述cache存储器之间向左的箭头表示所述cache存储器向所述DDR存储器的接口写入数据;同理地,所述MCU和所述cache存储器连接,所述MCU和所述cache存储器之间向右的箭头表示所述MCU通过其取指接口从所述cache存储器读取数据,所述MCU和所述cache存储器之间向左的箭头表示所述MCU向所述cache存储器写入数据。为了提高所述MCU的访问效率,本实施例中,cache存储器用于以突发传输操作的方式访问DDR存储器,以实现对DDR存储器较高的访问效率。MCU用于以单次传输操作的方式或以突发传输操作的方式访问cache存储器,比其以相同类型传输操作的方式访问DDR存储器快,使得MCU通过cache存储器从DDR存储器获取数据的速率整体上是大于直接从DDR存储器获取数据。从而通过所述cache存储器与DDR存储器的协作来保证MCU的取指操作能够快速高效地进行。

在本实施例中,MCU在一个时钟周期内以目标类型传输操作的方式进行访问的情况下,从cache存储器内获取的数据的数量是多于从DDR存储器内获取的数据的数量,以使MCU以相同类型传输操作对外部存储器进行访问的情况下,访问所述cache存储器的速率大于访问所述DDR存储器的速率,其中,MCU从DDR存储器内获取第一个数据相对于MCU从cache存储器内获取第一个数据产生延迟时间;具体地,MCU以同一类型传输操作的方式进行访问的情况下,从DDR存储器内获取数据相对于从cache存储器内获取数据产生的延迟时间取决于当前访问DDR存储器的主机(例如cache存储器或MCU)的数量、各个主机的访问优先级、DDR存储器内的数据读取机制所要求的延时等因素。在本实施例中,目标类型传输操作是突发传输操作或单次传输操作。具体地,MCU被配置为单次传输操作的方式访问cache存储器,对应产生的读写效率比设置片内目标存储器的MCU被配置为以单次传输操作的方式访问DDR存储器所产生的读写效率高;同理地,MCU被配置为突发传输操作的方式访问cache存储器,对应产生的读写效率比设置片内目标存储器的MCU被配置为以突发传输操作的方式访问DDR存储器所产生的读写效率高。由于MCU在一个时钟周期内对所述cache存储器突发传输操作过的地址单元的数量等于MCU在一个时钟周期内对所述cache存储器单次传输操作过的地址单元的数量,所以在所述MCU访问系统内,MCU在不设置目标片内存储器的情况下对DDR存储器的访问速率不受到具体总线传输类型的影响。从而在所述cache存储器预先存有所述MCU所需访问的数据的情况下,所述MCU会以突发传输操作的方式或以单次传输操作的方式先在所述cache存储器对应缓存行中查找,而不是直接以单次传输操作的方式访问DDR存储器,从而解决设置片内目标存储器的MCU以单次传输操作的方式访问DDR存储器存在的效率过低的问题。

在一些实施例中,MCU被配置为以单次传输操作的方式访问cache存储器的情况下,由于MCU在一个时钟周期内对所述cache存储器突发传输操作过的地址单元的数量等于MCU在一个时钟周期内对所述cache存储器单次传输操作过的地址单元的数量,所以MCU在不设置目标片内存储器的情况下对DDR存储器的访问速率不受到具体总线传输类型的影响。因而,cache存储器被配置为以突发传输操作的方式访问DDR存储器的情况下,即使MCU被配置为单次传输操作的方式访问cache存储器,对应产生的读写效率也比设置片内目标存储器的MCU被配置为以单次传输操作的方式访问DDR存储器所产生的读写效率高。另一方面,所述cache存储器是SRAM存储器的情况下,对于cache存储器而言,所述突发传输操作和所述单次传输操作的访问速度之间没有区别,进而相对于MCU访问片外flash,不存在输入输出接口之间的速度差异,减少设置额外的缓存区来平衡速度差,减少对所述MCU外部的总线仲裁占用资源,简化所述MCU的访问控制逻辑。

需要说明的是,对于DDR存储器而言,所述MCU或cache存储器对DDR存储器发起的突发传输操作的效率高于其发起的单次传输操作的效率,即所述MCU在同一时钟周期内对DDR存储器突发传输的数据的数量大于对DDR存储器单次传输的数据的数量;然而对于cache存储器而言,所述MCU对cache存储器发起的突发传输操作的效率与单次传输操作的效率相等,即所述MCU在同一时钟周期内对cache存储器突发传输的数据的数量等于对cache存储器单次传输的数据的数量。其中,突发传输操作和单次传输操作都属于AHB总线协议下规定的总线传输操作类型。

作为一种实施例,MCU的内部不设置目标片内存储器,目标片内存储器可以是不设置嵌入式SRAM和嵌入式flash等充当高速取指接口的片内存储器。不设置目标片内存储器的MCU可以构成一种通用微控制器,不设置SRAM的MCU可以但不限于集成硬件乘法器、硬件除法器、硬件分频器、嵌套向量中断控制器(NVIC)等独立资源,但不设置嵌入式SRAM以及其它大容量的片内存储器(例如flash),在一些实施场景是属于ARM Cortex-M系列架构下的部分类型的通用微控制器,而且在AHB总线协议下对对片外存储器进行单次传输操作。在本实施例中,所述MCU的内部不设置目标片内存储器,以使cache存储器代替目标片内存储器缓存MCU与DDR存储器之间传输的数据;其中,所述DDR存储器的容量大于所述cache存储器的容量;所述cache存储器的容量优选为大于所述目标片内存储器的容量。相对于所述MCU,所述DDR存储器内存储的数据是外部数据,包括需要被MCU调取的指令和数据块;为了满足应用程序的存储量需求,所述DDR存储器的容量大于所述cache存储器的容量,所述cache存储器的容量大于所述目标片内存储器的容量;而且,DDR存储器的容量大于目标片内存储器的容量,为MCU提供足够多的片外存储空间。发挥DDR存储器在片外的容量优势,MCU不设置片内存储器,则可以让DDR存储器代替所述目标片内存储器的指令缓冲作用,从而降低MCU的设计成本,进而降低所述MCU外围的硬件电路设计成本。因此,MCU不采用大容量的内嵌SRAM和内嵌flash进行数据缓存操作的前提下,在MCU的外部引入DDR存储器来代替所述目标片内存储器执行大容量的应用程序存储功能,从而不需开发一款更大容量的MCU芯片,克服应用程序超出内嵌存储器的容量而需要扩大MCU的芯片面积的问题,既可以发挥DDR存储器大容量的优势,又可以降低MCU的开发成本。

具体地,MCU用于在不设置目标片内存储器的情况下,通过cache存储器对DDR存储器进行访问,可以包括对DDR存储器进行读操作或写操作,尤其是对DDR存储器内一批用于循环计算的数据的读写操作,MCU在每次突发传输操作中只读取用于一轮循环计算的数据缓存到cache存储器内,即一批用于循环计算的数据当中的少部分数据,在不使用目标片内存储器进行外部数据存储的情况下减少MCU内部的缓存压力,在不需要MCU中过多内嵌存储器的支持下一定程度上解决前述的成本问题以及容量问题;另一方面,所述MCU与DDR存储器之间进行高速数据交换的过程中,所述MCU访问所述cache存储器时,所述MCU会先在在所述cache存储器对应缓存行中查找;当所述cache存储器中没有所述MCU所需访问的数据时,才启动所述cache存储器访问所述DDR存储器,提高MCU对DDR存储器的数据访问效率。

需要说明的是,DDR SDRAM(简称为DDR)双倍速率同步动态随机存储器,DDR存储器可以通过DDR接口与MCU外部的总线建立电气连接关系,以将所述MCU外部的访存空间设置成双倍数据速率 (DDR) 内存系统。DDR存储器的DDR接口可以在不改变系统最大信号频率的情况下显着提高数据传输速率;即使数据信号的最大频率增加了两倍,DDR信号使外部的访问设备能够在保持当前可行的最大时钟频率的同时将吞吐量提高一倍。

在一些实施例中,所述目标片内存储器包括嵌入式SRAM或嵌入式flash;所述目标片内存储器、所述MCU、所述cache存储器和所述DDR存储器设置在同一电路板的情况下,若所述目标片内存储器嵌入到所述MCU所在的芯片内部,则嵌入式SRAM和嵌入式flash的设计成本很高,因此二者的晶圆面积不能做得很大,会制约所述MCU的使用,因此需要使用前述实施例公开的cache存储器和DDR存储器作为片外存储器,不保留嵌入式SRAM和嵌入式flash的部分数据缓存功能,则所述目标片内存储器、所述MCU、所述cache存储器和所述DDR存储器设置在同一电路板的情况下,所述MCU不嵌入所述目标片内存储器,则直接使用前述实施例公开的cache存储器和DDR存储器作为片外存储器,不再使用所述目标片内存储器进行数据缓存,节约MCU的设计成本。需要说明的是,所述MCU、所述cache存储器和所述DDR存储器设置在同一电路板的情况下,所述MCU、所述cache存储器和所述DDR存储器成为电路板中的三种芯片。

需要说明的是,在所述MCU的内部配置有AHB总线解析模块(图中没有表示出),起到传输控制作用;所述MCU可以采用AHB总线解析模块(可以理解为寄存器模组)与cache存储器进行AHB总线上的数据交互,cache存储器也可以采用AHB总线解析模块(可以理解为寄存器模组)与DDR存储器进行AHB总线上的数据交互;AHB总线解析模块,用于解析总线协议指令,将总线传送的数据信号和地址信号进行转化,在所述MCU发出取址指令后按照总线地址访问cache存储器;本实施中使用的总线协议优选为AHB总线协议,其中,突发传输操作(包括突发读操作和突发写操作)的控制作用和单次传输操作(单次写操作和单次读操作)的控制作用的控制作用,且均由AHB总线协议规范(这一作为SOC的片上系统总线协议)规定的,所述MCU或所述cache存储器进行数据的突发传输操作的过程中,发出的地址都是对齐的,则以对齐地址的形式来对存储空间(逻辑 Bank)进行划分,在外部访问突发读取或者突发写入数据时,要以这种划分为前提进行,对齐地址是由每拍传输的数据的宽度来决定的,对齐地址是属于连续地址,存在的地址数量是突发长度。所述MCU或所述cache存储器进行数据的单次传输操作的过程中,一次性传输的连续地址的数量是单次长度,在外部单次读取或者单次写入数据时,单次长度是由每拍传输的地址连续的数据来决定的。其中,单次长度小于突发长度,单次长度大于或等于数值1;突发长度表示一次突发传输操作下传输的连续的地址单元的数量;突发传输操作是突发读操作或突发写操作;单次长度表示一次单次传输操作下传输的连续的地址单元的数量;单次传输操作是单次读操作或单次写操作。在本实施例中,一次突发读取的数据数量与一次单次读取的数据数量的比值是预设整数值,使得所述cache存储器或设置片内目标存储器的MCU对DDR存储器执行过预设整数值的单次读操作,获得的数据的数量或地址单元的数量,等于cache存储器对DDR存储器执行过一次突发读操作所获得数据的数量或地址单元的数量。

需要说明的是,cache存储器,简称为cache,用于缓存所述MCU从所述DDR存储器内所需读取的数据、以及所述MCU所需写入述DDR存储器的数据,则所述MCU可以通过cache存储器来间接(代替目标片内存储器发挥数据缓存作用)访问所述DDR存储器,每次可以从cache存储器读取所需访问的数据当中的一部分(相当于原本存储于所述DDR存储器内的一段指令集当中的若干条指令,若干条指令是预先被读取到cache存储器),当然所述MCU也可以将少部分指令写入cache存储器内以起到数据备份的作用。值得注意的是,cache存储器的接口所支持的输入速率与其输出速率最好不存在差异,则不需要在所访问cache存储器的设备中设置数据缓冲区来平衡这一差异,减少访问控制逻辑的复杂度。

作为一种实施例,所述cache存储器包括多条缓存行;所述cache存储器,用于根据所述MCU的读请求指令,将所述DDR存储器内所存储的第一目标数据读取出来并存储到对应的缓存行中,然后通知所述MCU读取对应的缓存行中的数据,以使所述MCU索引到第一目标数据。所述MCU的读请求指令是预先发送给所述cache存储器,所述MCU的读请求指令包括第一目标数据在所述DDR存储器内的存储地址、或第一目标数据在所述cache存储器的对应缓存行的存储地址;在所述cache存储器预先存储好第一目标数据的情况下,所述MCU的读请求指令还可以支持所述MCU从所述cache存储器内读取对应缓存行中的第一目标数据,相对于在同一传输操作下从所述DDR存储器内读取第一目标数据快。其中,读请求指令是在突发传输操作下配置出来,以使所述cache存储器每次从所述DDR存储器内突发读取出一批数据,可能包括第一目标数据。

所述cache存储器,还用于根据所述MCU的写请求指令,接收所述MCU输出的第二目标数据,并将第二目标数据存储到对应的缓存行中,可以起到数据备份的作用,当然可以在所述cache存储器的容量受限的情况下,通知所述DDR存储器读取对应的缓存行中的数据以使所述MCU将第二目标数据写入到所述DDR存储器内,其中,所述MCU的写请求指令包括第二目标数据在所述DDR存储器内的存储地址、或第二目标数据在所述cache存储器的对应缓存行的存储地址。写请求指令是在突发传输操作下或单次传输操作下配置出来,以使所述MCU每次向所述cache存储器内突发写入或单次写入一批数据,可能包括第二目标数据。

需要说明的是,所述MCU的写请求指令和所述MCU的读请求指令都是由MCU的取指令接口所控制,并且遵循MCU支持的访问总线协议的时序特征,以保障所述MCU正常访问所述cache存储器。所述MCU一般通过单次传输操作的方式访问外部的存储器。所述MCU可以由专用控制逻辑组成;所述MCU还可以是指处理器核(core)或其他特定集成电路(Application Specific Integrated Circuit,ASIC),或者是被配置成实施本实施例的一个或多个集成电路。所述cache存储器可以通过独立的存储器接口与所述MCU的取指令接口相连接,所述DDR存储器的DDR接口与所述cache存储器的其它接口相连接。所述MCU的内部可以是不设置所述目标片内存储器。

所述MCU在所述MCU访问系统内进行数据交互的过程中,当所述MCU访问数据时,所述MCU会先在在所述cache存储器中对应缓存行中查找,可以是以突发传输操作的方式或单次传输操作的方式;当所述cache存储器中没有所述MCU所需访问的数据时,才启动所述cache存储器访问所述DDR存储器,一般会以突发传输操作的方式访问,从而加快了所述MCU的访问速率。具体地,所述MCU每次从所述cache存储器读取第一目标数据之前,依次对各条缓存行进行数据索引,包括按照索引号由小到大的顺序依次索引各条缓存行;并在当前一条缓存行中按照地址值由小到大的顺序依次索引各个地址单元,然后换行继续索引下一条缓存行中的地址单元。

若所述第一目标数据存在于当前索引的一条缓存行中,则从当前索引的一条缓存行中读取所述第一目标数据。若所述第一目标数据不存在于所述cache存储器内所有的缓存行中,则触发所述cache存储器一次性从所述DDR存储器中读取出一个突发长度的数据,并存储起来以更新掉对应缓存行中的数据;由于cache存储器用于以突发传输操作的方式访问DDR存储器,所以,所述cache存储器通过突发传输操作的方式访问所述DDR存储器,以获得一个突发长度的数据。因此,当所述cache存储器中没有所述MCU所需访问的数据时,才启动所述cache存储器访问所述DDR存储器,提高对所述MCU的数据访问效率。更新掉对应缓存行中的数据后,所述cache存储器通知所述MCU读取更新后的缓存行中的数据(也可视为当前索引的一条缓存行中的数据),并判断当前索引的一条缓存行中的数据是否存在所述第一目标数据,是则确定地址匹配并确定索引完成,但不一定遍历完整条缓存行;否则确定缓存丢失,需要继续触发所述cache存储器进一步地从所述DDR存储器中读取出新的一个突发长度的数据,如此重复更新和索引,直至所述MCU从当前索引的一条缓存行中读取所述第一目标数据,确定获得有效的数据和匹配的地址,在本实施例中,整个索引过程中可以视为由所述MCU内部的硬件读写操作逻辑发出相应的访问命令以控制完成,具体可以是突发传输操作下规定的突发读操作。

由于MCU在一个时钟周期内以突发传输操作的方式进行访问的情况下,从cache存储器内获取的数据的数量是多于从DDR存储器内获取的数据的数量,即MCU在同一传输操作下访问cache存储器快于访问DDR存储器;所以在所述cache存储器预先存有所述MCU所需访问的数据(第一目标数据)的情况下,所以,在所述cache存储器预先存有所述MCU所需访问的数据的情况下,所述MCU会以突发传输操作的方式或单次传输操作的方式先在所述cache存储器对应缓存行中查找,而不是以单次传输操作的方式从所述DDR存储器查找,提高所述MCU的访问效率。

在前述实施例的基础上,所述突发长度等于第一预设参数与缓存行长度的乘积;其中,缓存行长度是一条缓存行当中设置的连续的地址单元的数量,也表示一条缓存行当中地址连续的数据的数量;所述突发长度小于或等于缓存行长度,则所述第一预设参数大于数值0,但小于或等于数值1。每个地址单元的数据存储容量相等,则一条缓存行中缓存的最大数据容量等于缓存行长度与单个地址单元的数据位宽之间的乘积;缓存行中一个地址单元存储一个数据,缓存行长度等于一条缓存行当中存储的数据的数量。优选地,所述cache存储器的接口位宽等于所述DDR存储器的DDR接口的位宽,所述cache存储器的接口位宽等于所述MCU的取指接口的位宽,减少因为位宽不兼容而需要对传输的数据进行拆分现象,有利于形成高效的数据通路。

所述第一预设参数等于数值1时,所述cache存储器一次性从所述DDR存储器中读取出的数据更新掉预先设置的最早被所述MCU读取的一条缓存行中的数据,实现所述MCU以一条缓存行为访问单位进行访问;其中,所述cache存储器一次性从所述DDR存储器中读取出的数据的数量等于所述缓存行长度,该实施方式可以发生在所述MCU检测到所述第一目标数据不存在于所述cache存储器内所有的缓存行中的情况下,也可以发生在所述MCU开始访问所述cache存储器之前。因而,cache存储器能够一次性地从大容量的DDR存储器内读取一个缓存行的数据,以便于更新替换cache存储器内对应一个缓存行的数据,从而以一个缓存行长度为粒度进行缓存数据的刷新,进而辅助MCU以一个缓存行长度为粒度从外挂的相应缓存行内索引出所需读取的第一目标数据,既兼顾到MCU访问数据的准确性和实时性,又考虑到MCU内嵌存储器的空间容量负担。

所述第一预设参数小于数值1且大于数值0时,所述cache存储器一次性从所述DDR存储器中读取出的数据更新掉预先设置的最早被所述MCU读取的一条缓存行中的部分数据,该部分数据占据的地址单元的数量与最早被所述MCU读取的一条缓存行所有地址单元的数量的比值是第一预设参数,所述cache存储器一次性从所述DDR存储器中读取出的数据的数量小于所述缓存行长度,则只能替换掉一条缓存行内部分数据;该实施方式可以发生在所述MCU检测到所述第一目标数据不存在于所述cache存储器内所有的缓存行中的情况下,也可以发生在所述MCU开始访问所述cache存储器之前。

在所述MCU访问系统中,所述MCU对所述cache存储器的访问都是基于AHB协议或AXI协议设计,以使所述MCU对所述cache存储器的读操作是突发读操作或单次读操作,所述MCU对所述cache存储器的写操作是突发写操作或单次写操作,实现基于硬件逻辑实现的对所述cache存储器的访问,至少由所述MCU的取指接口参与,并根据AHB或AXI协议传输数据。所述MCU对所述cache存储器的读操作是突发读操作或单次读操作,所述MCU对所述cache存储器的写操作是突发写操作或单次写操作;其中,单次长度表示一次单次传输操作下传输的连续的地址单元的数量,即一次单次传输操作下传输的地址单元连续的数据的数量;所述单次长度小于所述突发长度,优选为2个;突发传输操作是突发读操作或突发写操作,单次传输操作是单次读操作或单次写操作;cache存储器被配置为以突发传输操作的方式访问DDR存储器。

需要说明的是,所述cache存储器一次性从所述DDR存储器中读取出一个突发长度的地址单元内的数据的方式是突发读操作,即所述cache存储器在一个读时钟周期内一次性从所述DDR存储器中读取出突发长度个数据,可以由所述cache存储器、MCU或DDR存储器内设的突发读模式状态机控制实现;所述cache存储器还支持通过突发写操作来将一个突发长度的数据一次性写入所述DDR存储器中,即所述cache存储器在一个写时钟周期内一次性向所述DDR存储器中写入突发长度个数据,可以由所述cache存储器、MCU或DDR存储器内设的突发写模式状态机控制实现。突发长度优选为64个、32个、16个、8个、或4个。

其中,所述突发长度表示一次突发传输操作下传输的连续的地址单元的数量;突发传输操作是突发读操作或突发写操作,因所述cache存储器所处的工作状态而作出相应的转换;突发读操作归属于突发读模式状态机在突发读模式下实施的操作,突发写操作归属于突发写模式状态机在突发写模式下实施的操作。突发读模式和突发写模式分别有专用的寄存器进行工作模式的配置。

优选地,cache存储器为SRAM存储器,对于cache存储器而言,所述突发传输操作和所述单次传输操作的访问速度之间没有区别;进而相对于MCU访问片外flash,不存在输入输出接口之间的速度差异,减少设置额外的缓存区来平衡速度差,减少对所述MCU外部的总线仲裁占用资源,简化所述MCU的访问控制逻辑。

综上,在以同类型传输操作方式进行访问的情况下,MCU访问cache存储器的速率是大于MCU访问DDR存储器的速率,以使得MCU在相同时钟周期内从cache存储器获取的数据是多于从DDR存储器获取的数据;又由于MCU在一个时钟周期内对所述cache存储器突发传输操作过的地址单元的数量等于MCU在一个时钟周期内对所述cache存储器单次传输操作过的地址单元的数量,以使得MCU采用突发传输操作访问所述cache存储器和采用单次传输操作的方式访问所述cache存储器在同一时钟周期内的传输过的数据的数量是一样,所以,MCU在不设置目标片内存储器的情况下通过cache存储器对DDR存储器的访问不会受到单次传输操作的影响(来源于单次传输操作的访问效率制约);在此基础上,cache存储器被配置为以突发传输操作的方式访问DDR存储器且MCU被配置为以单次传输操作的方式访问cache存储器的情况下,所述MCU访问系统访问DDR存储器产生的读写效率比内设SRAM的MCU以单次传输操作方式访问DDR存储器所产生的读写效率高。解决设置片内目标存储器的MCU以单次传输操作的方式直接访问DDR存储器存在的效率过低的问题。

作为一种实施例,在所述cache存储器中,每条缓存行中的地址单元的数量都是相等,而且,每个地址单元设置的数据位宽是相等,以使所述cache存储器由多行多列的数据块组成,某行某列的一个数据块等效于设置在该行处的一条缓存行中的对应列的地址单元,所述缓存行长度在此作为划分一行地址的标准,在外部访问读取或者存储数据时,要以这种划分为前提进行,划分出的地址的数据容量可以由每个时钟节拍传输的数据的宽度来决定;优选地,每个地址单元设置的数据位宽是64比特位、32比特位、或16比特位,可以作为所述MCU访问所述cache存储器的最小单位。

具体地,缓存行长度是一条缓存行当中设置的连续的地址单元的数量时,所述cache存储器的容量是等于缓存行的总条数、缓存行长度与预设数据位宽的乘积,其中,每条缓存行当中指示的连续的地址的数量是相等且固定;每个地址单元存储的数据都是预设数据位宽的指令,预设数据位宽可以设置为32比特位,当缓存行长度是设置为16时,一条缓存行存储16条32比特位的指令,进一步地,所述cache存储器设置有32条缓存行时,所述cache存储器的容量是32*16*32bit。

优选地,为了提高所述cache存储器的数据传输速度,所述cache存储器突发读操作时所采用的工作时钟的频率优选为大于所述MCU突发读操作时所采用的工作时钟的频率,还可以理解为在所述MCU访问系统内最大的时钟频率。

在本申请所提供的实施例中,应该理解到,所揭露的系统、芯片,可以通过其它的方式实现。例如,以上所描述的系统实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目。

- 一种基于MCU的双TFT屏显示系统及其显示方法

- 一种MCU外设访问系统及访问方法

- 一种多核MCU访问共享外设的控制系统及相关设备