一种基于厚薄膜电路基板的大功率开关设计方法

文献发布时间:2023-06-19 19:40:14

技术领域

本发明涉及电子信息技术领域,尤其涉及一种基于厚薄膜电路基板的大功率开关设计方法。

背景技术

大功率开关常用于雷达前端,用于收发切换或者工作模式切换。大功率开关需要在满足大功率条件的同时保证开关的插损和驻波等指标。开关插损会直接减小雷达的输出功率,降低雷达效率,同时插损带来的热损耗会增加雷达的散热负担。驻波是信号反射指标,驻波大对应信号的反射大,在大功率的条件下,较大的反射可能烧毁后端己方设备,同时,会减小输出功率,降低效率。

目前雷达趋向于小型化设计,而小型化设计对加工精度要求较高,因此如何实现大功率开关的小型化、高精度加工及小型化后提高散热效果,成为亟待解决的技术问题。

发明内容

本发明提供了一种基于厚薄膜电路基板的大功率开关设计方法,以解决上述现有技术的不足,该方法使用厚膜薄膜混合工艺,将电阻、电感等电子器件设置在内部的厚膜导体层,将用于控制电路的部件等设置在不同层,在表层放置了多个PIN二极管、驱动器、多个电容和多个射频传输线,各层之间通过金属化过孔实现连接,通过高度集成,可减小整个系统的尺寸,并方便进行高精度加工。

为了实现本发明的目的,拟采用以下技术:

一种基于厚薄膜电路基板的大功率开关设计方法,包括:

提供一层表层电路层,在其上设有驱动器、第一射频传输线、第二射频传输线、第三射频传输线、第四射频传输线、第一PIN二极管、第二PIN二极管、第三PIN二极管、第一电容、第二电容、第三电容及第四电容;

提供多层金属层,金属层至少包括第一金属层、第二金属层、第三金属层、第四金属层、第五金属层及第六金属层;在第二金属层上设置第一电感、第二电感、第三电感、第四电感;

在第四金属层上设置第一电阻及第二电阻;

在第五金属层上设置第一驱动器控制电路与第二驱动器控制电路;

提供多层陶瓷基板,在金属层的相邻两层之间架设一个陶瓷基板。

进一步地,还提供一层牺牲层,牺牲层设于表层电路层的下侧,且牺牲层位于第一金属层的上侧。牺牲层包括薄膜基板,薄膜基板的下侧至少设有一个厚膜牺牲层,薄膜基板设于表层电路层的下侧,厚膜牺牲层设于第一金属层的上侧,薄膜基板由氮化硅陶瓷制成。

进一步地,还在第六金属层的下侧设置钼铜层。在表层电路层上设置多个散热孔,散热孔贯穿过钼铜层。

进一步地,驱动器通过第一通道与第二通道分别连接至第一驱动器控制电路与第二驱动器控制电路上;驱动器还通过第三通道连接至第一金属层上;第一驱动器控制电路与第二驱动器控制电路分别通过第四通道与第五通道连接至表层电路层上。

进一步地,第一射频传输线通过第六通道连接至第一电感上;第二射频传输线通过第七通道连接至第三电感上;第三射频传输线通过第八通道连接至第四电感上;第四射频传输线通过第九通道连接至第二电感上。

进一步地,第一电感通过第十通道连接至第三金属层上;第三电感通过第十一通道连接至第三金属层上;第四电感通过第十二通道连接至第三金属层上;第二电感通过第十三通道连接至第三金属层上。

进一步地,第二电阻通过第十四通道与第十五通道连接至表层电路层上;第一电阻通过第十六通道与第十七通道连接至表层电路层上。

上述技术方案的优点在于:

一、由于采用了基于厚膜的多层结构,因此提供了多层布线基板,从而便于多线路的布线,同时设计走线可以更加灵活,并且通过这种方式可避免出现连接线的跨连、交叉等问题。

二、不同的电子器件模块均对应设置有独立的接地层,而用于连接各个器件之间的通道是通过金属化过孔与对应地层连接的,因此该通道存在着类似腔体隔离的状态,进而有利于对杂散信号进行屏蔽,并且能够使整个系统的电磁兼容性能更好。

三、各层陶瓷基板均采用氮化硅陶瓷作为制备材料,而这种制备材料具有相对介电常数高、导热性能良好等特点,从而便于满足系统小型化和大功率散热的需要。

四、表层采用氮化硅陶瓷制成的薄膜基板和呈薄膜状的表层电路层,并且在薄膜基板下设置至少两层厚膜基板作为厚膜牺牲层,并为了使其表面平整,在加工时需要对薄膜基板进行减薄、打磨、抛光等操作。通过改善薄膜基板表面的平整度,能够消除厚膜烧制过程中由于受热不均而带来的收缩或者膨胀等引发弯曲问题,同时平整后的薄膜基板可以和厚膜牺牲层实现良好叠合。

五、为了提高加工精度,表层电路层采用光刻技术进行精细化加工,而光刻技术的加工精度较高,因此,能够满足高密度集成后的小型化加工精度要求,同时由于表层电路层采用了薄膜工艺,而这种工艺能够使得表层电路形成光滑且平整的金属层,从而解决了厚膜加工精度不高、表面不平整的问题。同时,还解决了由于射频信号传输带来较大的损耗,在大功率信号下带来的发热、射频线间打火、介质击穿等问题。

六、在最底层添加钼铜层,并将钼铜层连接在金属壳体上,并且通过设置散热孔,从而方便进行系统散热。并且,其中各层电路层均采用钨合金制成,而壳体一般采用便于散热的合金制成,因此壳体和各层电路层之间的热膨胀系数不同,因此不能很好地使壳体和电路层之间直接相连,而钼铜层的引入不仅能起到散热作用,还能很好地和壳体相连,从而提高了系统和壳体之间的连接效果。

附图说明

为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明做进一步的详细描述。

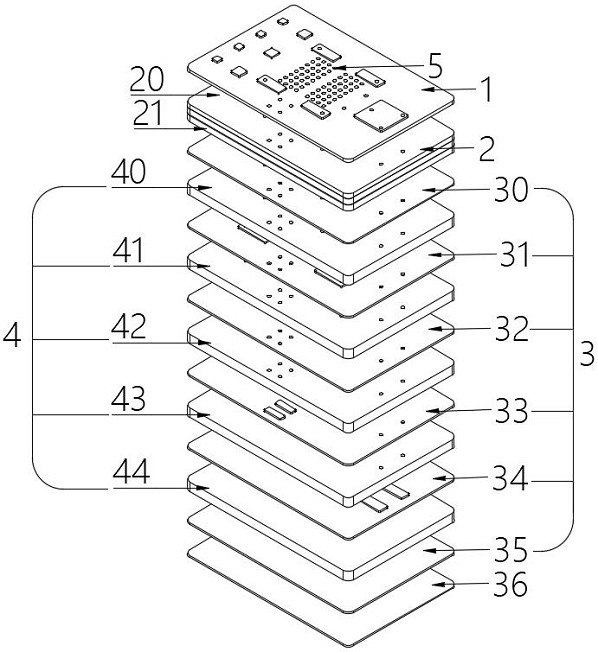

图1示出了实施例2的立体结构图。

图2示出了实施例2的立体结构图及通道连接图。

图3示出了实施例2中表层电路层的立体结构图。

图4示出了实施例2中第二金属层的立体结构图。

图5示出了实施例2中第四金属层的立体结构图。

图6示出了实施例2中第五金属层的立体结构图。

图7示出了实施例1中大功率开关的电路结构图。

附图标记说明:

表层电路层-1,驱动器-10,第一射频传输线-11,第二射频传输线-12,第三射频传输线-13,第四射频传输线-14,第一PIN二极管-15a,第二PIN二极管-15b,第三PIN二极管-15c,第一电容-16a,第二电容-16b,第三电容-16c,第四电容-16d,金属层-3,第一金属层-30,第二金属层-31,第三金属层-32,第四金属层-33,第五金属层-34,第六金属层-35,第一电感-310,第二电感-311,第三电感-312,第四电感-313,第一电阻-330,第二电阻-331,第一驱动器控制电路-340,第二驱动器控制电路-341,陶瓷基板-4,牺牲层-2,薄膜基板-20,厚膜牺牲层-21,钼铜层-36,散热孔-5,第一通道-60,第二通道-61,第三通道-64,第四通道-63,第五通道-62,第六通道-70,第七通道-71,第八通道-72,第九通道-73,第十通道-82,第十二通道-80,第十三通道-81,第十四通道-90,第十五通道-92,第十六通道-91,第十七通道-93,第一陶瓷基板-40,第二陶瓷基板-41,第三陶瓷基板-42,第四陶瓷基板-43,第五陶瓷基板-44。

具体实施方式

实施例1

如图7所示,为大功率开关的电路结构图,从图中不难看出,大功率开关包括输入端P1,输入端P1的另一端连接有电感L1,电感L1的另一端接地。

输入端P1的另一端还连接有PIN二极管D1,PIN二极管D1的负极端连接有PIN二极管D3,PIN二极管D3的正极端连接有电容C1,电容C1的另一端连接于输出端P2。

PIN二极管D1的负极端还连接有电感L2,电感L2的另一端连接有电阻R1,电阻R1的另一端连接有驱动器。

电感L2的另一端还连接有电容C2,电容C2的另一端接地,且电容C2位于电感L2与电阻R1之间。

PIN二极管D3的正极端还连接有电感L3,电感L3的另一端接地,且电感L3位于PIN二极管D3和电容C1之间。

输入端P1的另一端还连接有PIN二极管D2,PIN二极管D2的负极端连接有电容C4,电容C4的另一端连接于输出端P3。

PIN二极管D2的负极端还连接有电感L4,电感L4的另一端连接有电阻R2,电阻R2连接于驱动器上,电感L4位于电容C4与PIN二极管D2之间。

电感L4的另一端还连接有电容C3,电容C3的另一端接地,且电容C3位于电阻R2与电感L4之间。

驱动器的一端接地。

大功率信号从输入端P1输入,驱动器用于控制PIN二极管D1、PIN二极管D2及PIN二极管D3的开、关工作状态。

例如当驱动器提供-5V电压时,PIN二极管D1、PIN二极管D3处于导通状态,而电感L1、电感L2和电感L3此时阻断高频信号通过,因此信号只能从输出端P2经过电容C1滤波后输出。

当驱动器提供36V电压时,PIN二极管D2导通,电感L1、电感L4阻断高频信号通过,因此信号只能从下侧输出端P3经过电容C4滤波后输出。

电容C2、电阻R1为上侧或输出端P2所在侧驱动器电源的匹配电路。

电容C3、电阻R2为下侧或输出端P3所在侧驱动器电源电路的匹配电路。

实施例2

如图1~图2所示,一种基于厚薄膜电路基板的大功率开关设计方法,包括步骤:

提供一层表层电路层1,如图3所示,表层电路层1上设有驱动器10、第一射频传输线11、第二射频传输线12、第三射频传输线13、第四射频传输线14、第一PIN二极管15a、第二PIN二极管15b、第三PIN二极管15c、第一电容16a、第二电容16b、第三电容16c及第四电容16d。

提供一层牺牲层2,如图1所示,牺牲层2设于表层电路层1的下侧,且牺牲层2位于第一金属层30的上侧。牺牲层2包括薄膜基板20,薄膜基板20的下侧至少设有一个厚膜牺牲层21,薄膜基板20设于表层电路层1的下侧,厚膜牺牲层21设于第一金属层30的上侧,薄膜基板20由氮化硅陶瓷制成。

提供多层金属层3,如图1所示,金属层3至少包括第一金属层30、第二金属层31、第三金属层32、第四金属层33、第五金属层34及第六金属层35。

如图4所示,第二金属层31上设有第一电感310、第二电感311、第三电感312、第四电感313。

如图5所示,第四金属层33上设有第一电阻330及第二电阻331。

如图6所示,第五金属层34上设有第一驱动器控制电路340与第二驱动器控制电路341。

提供多层陶瓷基板4,在金属层3的相邻两层之间夹设一个陶瓷基板4。具体的,如图1所示,陶瓷基板4包括设于第一金属层30与第二金属层31之间的第一陶瓷基板40。第二金属层31与第三金属层32之间设有第二陶瓷基板41。第三金属层32与第四金属层33之间设有第三陶瓷基板42。第四金属层33与第五金属层34之间设有第四陶瓷基板43。

另外,如图1所示,第六金属层35的下侧设有钼铜层36,表层电路层1上设有多个散热孔5,散热孔5贯穿过钼铜层36,当散热孔5经过各层陶瓷基板4时,以金属过孔导通。而当散热孔5经过各层金属层3时,以过孔导通。通过将钼铜层36连接在金属壳体上,并且通过设置辅以散热的散热孔5,从而便于方便进行系统散热。并且,其中各层金属层均采用钨合金制成,而壳体一般采用便于散热的合金制成,因此壳体和各层电路层之间的热膨胀系数不同,因此不能很好地使壳体和电路层之间直接相连,而钼铜层36的引入不仅能起到散热作用,还能很好地和壳体相连,从而提高了系统和壳体之间的连接效果。

具体的,可采用薄膜厚膜工艺实施,其中,表层电路层1通过薄膜工艺在牺牲层2上形成,第一金属层30通过厚膜工艺形成于第一陶瓷基板40上、第二金属层31通过厚膜工艺形成于第二陶瓷基板41上、第三金属层32通过厚膜工艺形成于第三陶瓷基板42上、第四金属层33通过厚膜工艺形成于第四陶瓷基板43上、第五金属层34通过厚膜工艺形成于第五陶瓷基板44上,第六金属层35通过厚膜工艺形成于第五陶瓷基板44底面。然后在对应的层上设置对应的元器件,然后按照如图1所示的顺序,叠合各层,经烧制可制成。

结合图1~图6,具体地,驱动器10通过第一通道60与第二通道61分别连接至第一驱动器控制电路340与第二驱动器控制电路341上。驱动器10还通过第三通道64连接至第一金属层30上。第一驱动器控制电路340与第二驱动器控制电路341分别通过第四通道63与第五通道62连接至表层电路层1上。

具体地,第一射频传输线11通过第六通道70连接至第一电感310上。第二射频传输线12通过第七通道71连接至第三电感312上。第三射频传输线13通过第八通道72连接至第四电感313上。第四射频传输线14通过第九通道73连接至第二电感311上。

具体地,第一电感310通过第十通道82连接至第三金属层32上。第三电感312通过第十一通道连接至第三金属层32上。第四电感313通过第十二通道80连接至第三金属层32上。第二电感311通过第十三通道81连接至第三金属层32上。

具体地,第二电阻331通过第十四通道90与第十五通道92连接至表层电路层1上。第一电阻330通过第十六通道91与第十七通道93连接至表层电路层1上。

第一通道60、第二通道61、第三通道64、第四通道63、第五通道62、第六通道70、第七通道71、第八通道72、第九通道73、第十通道82、第十一通道、第十二通道80、第十三通道81、第十四通道90、第十五通道92、第十六通道91及第十七通道93当经过各层金属层3时以过孔的方式导通,当上述通道经过各层陶瓷基板4及牺牲层2时,通过金属过孔导通。

其中,驱动器10为实施例1中所提及的驱动器。

第一PIN二极管15a为实施例1中所提及的PIN二极管D1,第二PIN二极管15b为实施例1中所提及的PIN二极管D2,第三PIN二极管15c为实施例1中所提及的PIN二极管D3。

第一电容16a为实施例1中所提及的电容C1,第二电容16b为实施例1中所提及的电容C2,第三电容16c为实施例1中所提及的电容C3,第四电容16d为实施例1中所提及的电容C4。

第一电感310为实施例1中所提及的电感L1,第二电感311为实施例1中所提及的电感L2,第三电感312为实施例1中所提及的电感L3,第四电感313为实施例1中所提及的电感L4。

第一电阻330为实施例1中所提及的电阻R1,第二电阻331为实施例1中所提及的电阻R2。

其中,第一金属层30为驱动器10的接地层。

第三金属层32为第一电感310、第二电感311、第三电感312及第四电感313的接地层。

以上所述仅为本发明的优选实施例,并不用于限制本发明,显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

- 一种基于厚薄膜电路基板的大功率合成器实现方法

- 一种基于厚薄膜电路基板的大功率合成器实现方法