显示装置及用于制造显示装置的方法

文献发布时间:2023-06-19 09:57:26

技术领域

本发明涉及一种具有改善的可靠性的显示装置以及用于制造该显示装置的方法。

背景技术

显示装置可以包括发光元件。发光元件可以电连接到电极,并且可以根据施加到电极的电压发光。发光元件可以直接形成在电极上。可选地,发光元件可以单独形成,然后可以设置在电极上。当单独形成的发光元件设置在电极上时,根据发光元件的形状,发光元件与电极之间的连接可能不容易。另外,在用于连接发光元件和电极的连接电极中产生的裂纹会导致其中发光元件与电极之间的电阻增大的现象,这会导致发光效率降低。

发明内容

技术问题

本发明的示例性实施例提供了一种在发光元件与电极之间具有改善的连接稳定性的显示装置以及用于制造该显示装置的方法。

技术方案

根据本发明的一个示例性实施例的显示装置包括:第一电极;第二电极,与第一电极间隔开;发光元件,设置在第一电极和第二电极上;第一图案部分,设置为在平面上与其中第一电极和发光元件彼此叠置的第一区域相邻;第二图案部分,设置为在平面上与其中第二电极和发光元件彼此叠置的第二区域相邻;第一连接电极,覆盖发光元件和第一图案部分,并且电连接到发光元件和第一电极;以及第二连接电极,覆盖发光元件和第二图案部分,并且电连接到发光元件和第二电极。

第一图案部分和第二图案部分中的每个可以包括有机材料。

可以提供与所述发光元件相同的多个发光元件,并且所述多个发光元件可以并联连接。

发光元件的第一厚度可以大于第一图案部分的第一最大高度和第二图案部分的第二最大高度。

第一最大高度和第二最大高度中的每个可以是第一厚度的50%或更小。

第一电极与发光元件之间的倾斜角度可以为60°或更大。

设置在发光元件上的第一部分、设置在第一图案部分上的第二部分和设置在第一电极上的第三部分可以被限定在第一连接电极中,并且第一图案部分的与第二部分接触的倾斜表面与设置在第一图案部分下面的第一电极之间的角度可以是70°或更小。

显示装置还可以包括设置在发光元件上的保护部分,其中,保护部分在平面上设置在第一图案部分与第二图案部分之间。

保护部分可以包括第一保护部分和第二保护部分,第一保护部分包括无机材料,第二保护部分包括有机材料,并且第一保护部分可以设置在第二保护部分与发光元件之间。

显示装置还可以包括:第一无机图案部分,设置在第一图案部分与发光元件之间以及第一图案部分与第一电极之间;以及第二无机图案部分,设置在第二图案部分与发光元件之间以及第二图案部分与第二电极之间。

发光元件可以具有圆柱形状或多边形柱形状。

根据本发明的一个示例性实施例的显示装置包括:第一电极;第二电极,与第一电极间隔开;发光元件,设置在第一电极和第二电极上;第一连接电极,设置在第一电极和发光元件上,并且将第一电极和发光元件电连接;第二连接电极,设置在第二电极和发光元件上,并且将第二电极和发光元件电连接;第一图案部分,设置在第一连接电极与发光元件之间以及第一连接电极与第一电极之间,并且具有与第一连接电极接触的第一倾斜表面;以及第二图案部分,设置在第二连接电极与发光元件之间以及第二连接电极与第二电极之间,并且具有与第二连接电极接触的第二倾斜表面。

第一图案部分和第二图案部分中的每个可以包括有机材料。

第一图案部分可以在平面上围绕其中发光元件和第一电极彼此叠置的区域的至少一部分,第二图案部分可以在平面上围绕其中发光元件和第二电极彼此叠置的区域的至少一部分。

第一倾斜表面与第一电极之间的角度和第二倾斜表面与第二电极之间的角度中的每个可以是70°或更小。

根据一个示例性实施例的用于制造显示装置的方法包括:在绝缘层上形成第一电极和第二电极;在第一电极和第二电极上布置发光元件;形成覆盖发光元件、第一电极和第二电极的有机层;在有机层上布置掩模;通过使用掩模对有机层曝光和显影来形成有机图案;去除有机图案的一部分,以形成第一图案部分并形成第二图案部分,第一图案部分设置为在平面上与其中第一电极和发光元件彼此叠置的第一区域相邻,第二图案部分设置为在平面上与其中第二电极和发光元件彼此叠置的第二区域相邻;以及在第一图案部分上形成电连接到发光元件和第一电极的第一连接电极,并且形成电连接到发光元件和第二电极的第二连接电极。

掩模可以是包括半透明部分的半色调掩模,并且掩模可以设置为使得半透明部分设置于在平面上与第一电极和第二电极叠置的区域中。

方法还可以包括去除有机图案的一部分以形成设置在发光元件上的保护部分的步骤,其中,保护部分与第一图案部分和第二图案部分同时形成。

方法还可以包括:在形成有机层之前,形成覆盖发光元件、第一电极和第二电极的无机层;以及在形成第一图案部分和第二图案部分之后,去除暴露的无机层的一部分以形成设置在第一图案部分下面的第一无机图案部分,并且形成设置在第二图案部分下面的第二无机图案部分。

方法还可以包括:去除有机图案的一部分,以形成设置在发光元件上的有机保护部分;以及去除无机层的一部分,以形成设置在发光元件和有机保护部分之间的无机保护部分,其中,有机保护部分与第一图案部分和第二图案部分同时形成,并且无机保护部分与第一无机图案部分和第二无机图案部分同时形成。

有益效果

根据本发明的示例性实施例,在发光元件与将发光元件和电极连接的连接电极之间设置图案部分。图案部分可以设置为在平面上与发光元件和电极彼此叠置的区域相邻。连接电极的梯度的改变可以由于图案部分而减小。因此,能够减少其中连接电极断开或破裂的现象。结果,可以改善发光元件与电极之间的连接稳定性,并且可以改善显示装置的可靠性。由于降低了连接电极断开或破裂的可能性,所以可以减小连接电极的厚度。因此,随着连接电极的厚度减小,蚀刻工艺的工艺时间可以减少,这对于精细图案制造工艺会是有利的。

附图说明

图1是根据本发明的一个示例性实施例的显示装置的透视图。

图2是根据本发明的一个示例性实施例的显示装置的框图。

图3是根据本发明的一个示例性实施例的像素的等效电路图。

图4a是示出根据本发明的一个示例性实施例的像素的剖视图。

图4b是示出根据本发明的一个示例性实施例的像素的剖视图。

图5a是根据本发明的一个示例性实施例的发光元件的剖视图。

图5b是根据本发明的一个示例性实施例的发光元件的剖视图。

图5c是根据本发明的一个示例性实施例的发光元件的剖视图。

图5d是根据本发明的一个示例性实施例的发光元件的剖视图。

图6是根据本发明的一个示例性实施例的像素的平面图。

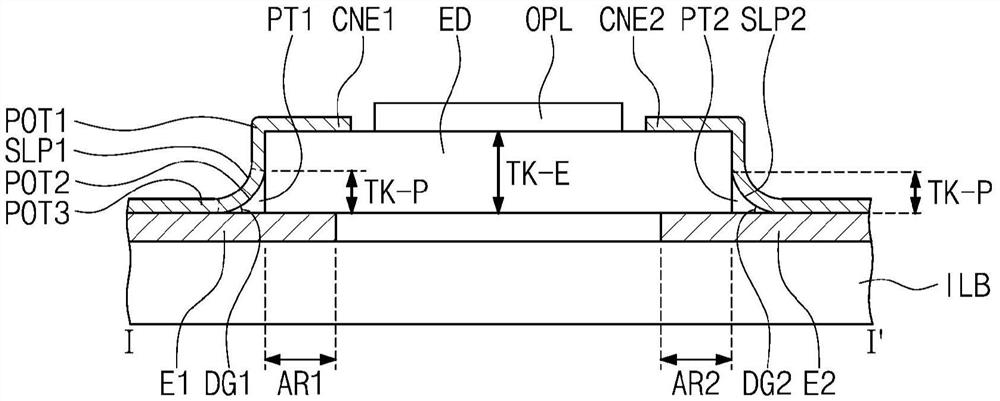

图7是沿着图6中所示的线I-I'截取的剖视图的示例。

图8是沿着图6中所示的线II-II'截取的剖视图的示例。

图9是沿着图6的线II-II'截取的剖视图的示例。

图10是沿着图6中所示的线II-II'截取的剖视图的示例。

图11a至图11h是示出根据本发明的一个示例性实施例的制造显示装置的工艺中的一些工艺的视图。

图12a至图12g是示出根据本发明的一个示例性实施例的制造显示装置的工艺中的一些工艺的视图。

具体实施方式

在本说明书中,还将理解的是,当一个组件(或区域、层、部分)被称为“在”另一组件“上”、“连接到”或“结合到”另一组件时,该组件可以直接在所述一组件上/直接连接到/直接结合到所述一组件,或者还可以存在一个或更多个中间组件。

同样的附图标记始终指代同样的组件。此外,在附图中,为了说明的清楚,夸大了组件的厚度、比例和尺寸。

术语“和/或”包括相关所列项中的一个或更多个的任何组合和所有组合。

尽管在此使用术语“第一”、“第二”等来描述各种组件,但是这些组件不应受这些术语的限制。术语仅用于将一个组件与另一组件区分开的目的。例如,在不脱离本发明的范围的情况下,第一组件可以被命名为第二组件,类似地,第二组件也可以被命名为第一组件。除非另外陈述,否则单数的表达形式旨在包括多个组件。

此外,术语“在……下面”、“在……下方”、“在……上方”、“上”等在此用于解释附图中所示的一个或更多个组件之间的关系。术语可以是描述附图中的组件的位置的相对术语。

除非另外定义,否则在此使用的所有术语(包括技术术语和科学术语)具有与本发明所属领域的普通技术人员通常理解的的含义相同的含义。还将理解的是,术语(诸如在通用词典中定义的术语)应当被解释为具有与它们在相关领域的背景下的含义一致的含义,并且将不以理想化或过于形式化的意思来解释,除非在此明确这样定义。

将理解的是,当在此使用术语“包括”、“包含”或其变型时,说明存在所陈述的特征、数量、步骤、操作、元件和/或组件,但不排除存在或添加一个或更多个其他特征、数量、步骤、操作、元件、组件和/或它们的组。

在下文中,将参照附图描述本发明的示例性实施例。

图1是根据本发明的一个示例性实施例的显示装置的透视图。

参照图1,显示装置DD可以通过显示区域DA显示图像。图1示例性示出了显示区域DA具有由第一方向DR1和与第一方向DR1交叉的第二方向DR2限定的表面。然而,在本发明的其他示例性实施例中,显示装置的显示区域可以具有弯曲形状。

显示装置DD的厚度方向由第三方向DR3指示。由第一方向至第三方向DR1、DR2和DR3指示的方向是相对概念,并且可以转换为其他方向。本说明书中的术语“在平面图中”可以指当在第三方向DR3上观察时。

在图1中,显示装置DD被示例性地示出为电视。然而,显示装置DD也可以用于中小尺寸电子装置(诸如个人计算机、笔记本计算机、个人数字终端、车辆导航单元、游戏机、智能电话、平板电脑和相机以及监视器)或大尺寸电子装置(诸如户外广告牌)。另外,所述装置仅仅是示例,并且显示装置DD也可以应用于其他电子装置,而不脱离本发明的精神和范围。

图2是根据本发明的一个示例性实施例的显示装置的框图。

参照图2,显示装置DD可以包括显示面板DP、信号控制器(或时序控制器)TC、数据驱动器DDV和扫描驱动器GDV。信号控制器TC、数据驱动器DDV和扫描驱动器GDV中的每个可以包括电路。

显示面板DP可以是包括微型发光元件的微型发光元件显示面板DP。例如,显示面板DP可以是微型发光二极管(LED)显示面板DP。

显示面板DP可以包括多条数据线DL1至DLm、多条扫描线SL1至SLn以及多个像素PX。

多条数据线DL1至DLm可以沿第一方向DR1延伸,并且可以沿与第一方向DR1交叉的第二方向DR2布置。多条扫描线SL1至SLn可以沿第二方向DR2延伸,并且可以沿第一方向DR1布置。

像素PX中的每个可以包括发光元件和电连接到发光元件的像素电路。像素电路可以包括多个晶体管。第一电力电压ELVDD和第二电力电压ELVSS可被供应到像素PX中的每个。

像素PX可以根据一定规则布置在显示面板DP的平面表面上。像素PX中的每个可以显示原色中的一种或混合色中的一种。原色可以包括红色、绿色和蓝色,并且混合色可以包括诸如黄色、青色、品红色和白色的各种颜色。然而,由像素PX显示的颜色不限于此。

信号控制器TC接收从外部源提供的图像数据RGB。信号控制器TC通过转换图像数据RGB产生转换的图像数据R'G'B'以适于显示面板DP的操作,并且向数据驱动器DDV输入转换的图像数据R'G'B'。

另外,信号控制器TC可以接收从外部源提供的控制信号CS。控制信号CS可以包括垂直同步信号、水平同步信号、主时钟信号、数据使能信号等。信号控制器TC向数据驱动器DDV提供第一控制信号CONT1,并且向扫描驱动器GDV提供第二控制信号CONT2。第一控制信号CONT1是用于控制数据驱动器DDV的信号,并且第二控制信号CONT2是用于控制扫描驱动器GDV的信号。

数据驱动器DDV可以响应于从信号控制器TC接收的第一控制信号CONT1来驱动多条数据线DL1至DLm。数据驱动器DDV可以被实现为独立的集成电路并且电连接到显示面板DP的一侧,或者可以直接安装在显示面板DP上。另外,数据驱动器DDV可以被实现为单个芯片,或者可以包括多个芯片。

扫描驱动器GDV响应于从信号控制器TC接收的第二控制信号CONT2来驱动扫描线SL1至SLn。扫描驱动器GDV可以被集成在显示面板DP的某区域中。在这种情况下,扫描驱动器GDV可以包括通过与像素PX的驱动电路相同的工艺(例如,低温多晶硅(LTPS)工艺或低温多晶氧化物(LTPO)工艺)形成的多个薄膜晶体管。另外,扫描驱动器GDV可以被实现为独立的集成电路芯片,并且电连接到显示面板DP的一侧。

当向多条扫描线SL1至SLn中的一条扫描线施加栅极导通电压时,连接到该扫描线的一行中的像素中的每个的开关晶体管导通。在这种情况下,数据驱动器DDV向数据线DL1至DLm提供数据驱动信号。提供到数据线DL1至DLm的数据驱动信号通过导通的开关晶体管被施加到对应的像素。数据驱动信号可以是与多个图像数据的灰度值对应的模拟电压。

图3是根据本发明的一个示例性实施例的像素的等效电路图。

参照图3,像素PX可以连接到多条信号线。在本示例性实施例中,示例性地示出了信号线之中的扫描线SL、数据线DL、第一电力线PL1和第二电力线PL2。然而,信号线是示例性地示出的。根据本发明的一个示例性实施例的像素PX可以额外地连接到各种信号线,并且本发明不限于任何一个示例性实施例。

像素PX可以包括发光元件ED和像素电路PXC。像素电路PXC可以包括第一薄膜晶体管TR1、电容器CAP和第二薄膜晶体管TR2。

第一薄膜晶体管TR1可以是控制像素PX的导通或截止的开关晶体管。第一薄膜晶体管TR1可以响应于通过扫描线SL传递的栅极信号来传输或阻挡通过数据线DL传递的数据信号。

电容器CAP连接到第一薄膜晶体管TR1和第一电力线PL1。电容器CAP充有与从第一薄膜晶体管TR1传递的数据信号和施加到第一电力线PL1的第一电力电压ELVDD之间的差对应的电荷量。

第二薄膜晶体管TR2连接到第一薄膜晶体管TR1、电容器CAP和发光元件ED。第二薄膜晶体管TR2响应于存储在电容器CAP中的电荷量来控制在发光元件ED中流动的驱动电流。第二薄膜晶体管TR2的导通时间可以根据电容器CAP中充有的电荷量来确定。

第一薄膜晶体管TR1和第二薄膜晶体管TR2可以是N型薄膜晶体管或P型薄膜晶体管。此外,在本发明的另一示例性实施例中,第一薄膜晶体管TR1和第二薄膜晶体管TR2中的一个可以是N型薄膜晶体管,并且它们中的另一个可以是P型薄膜晶体管。

发光元件ED连接到第二薄膜晶体管TR2和第二电力线PL2。发光元件ED以与通过第二薄膜晶体管TR2传递的信号和通过第二电力线PL2接收的第二电力电压ELVSS之间的差对应的电压发光。

发光元件ED可以是微型LED元件。微型LED元件可以是具有在几纳米至几百微米的范围内的长度的LED元件。然而,微型LED元件的长度仅被描述为示例,并且微型LED元件的长度不限于上面的数值范围。

虽然图3示出了一个发光元件ED连接在第二薄膜晶体管TR2与第二电力线PL2之间的示例,但是可以设置多个发光元件ED。多个发光元件ED可以并联地彼此连接。

图4a是示出根据本发明的一个示例性实施例的像素的剖视图。图4a示出了第一薄膜晶体管TR1、第二薄膜晶体管TR2和发光元件ED的剖面。

参照图4a,基体层BL可以是硅基底、塑料基底、玻璃基底、绝缘膜或包括多个绝缘层的堆叠结构。

第一薄膜晶体管TR1和第二薄膜晶体管TR2中的每个可以设置在基体层BL上。第一薄膜晶体管TR1可以包括第一控制电极CE1、第一输入电极IE1、第一输出电极OE1和第一半导体图案SP1。第二薄膜晶体管TR2可以包括第二控制电极CE2、第二输入电极IE2、第二输出电极OE2和第二半导体图案SP2。

第一控制电极CE1和第二控制电极CE2可以设置在基体层BL上。第一控制电极CE1和第二控制电极CE2可以包括导电材料。第一绝缘层L1可以设置在基体层BL上,并且可以覆盖第一控制电极CE1和第二控制电极CE2。即,第一控制电极CE1和第二控制电极CE2可以设置在第一绝缘层L1与基体层BL之间。

第一半导体图案SP1和第二半导体图案SP2可以设置在第一绝缘层L1上。第一半导体图案SP1和第二半导体图案SP2中的每个可以包括半导体材料。例如,第一半导体图案SP1和第二半导体图案SP2可以包括相同的半导体材料并且也可以包括不同的半导体材料。半导体材料可以包括例如选自非晶硅、多晶硅、单晶硅、氧化物半导体和化合物半导体中的至少一种。第一半导体图案SP1和第二半导体图案SP2中的每个可以包括用作电子或空穴移动通过的路径的沟道区以及设置成沟道区介于它们之间的第一离子掺杂区和第二离子掺杂区。

第一输入电极IE1和第一输出电极OE1可以设置在第一半导体图案SP1上,并且第二输入电极IE2和第二输出电极OE2可以设置在第二半导体图案SP2上。

第二绝缘层L2可以设置在第一绝缘层L1上,并且可以覆盖第一半导体图案SP1和第二半导体图案SP2、第一输入电极IE1和第二输入电极IE2以及第一输出电极OE1和第二输出电极OE2。即,第一半导体图案SP1和第二半导体图案SP2、第一输入电极IE1和第二输入电极IE2以及第一输出电极OE1和第二输出电极OE2可以设置在第一绝缘层L1与第二绝缘层L2之间。

第三绝缘层L3可以设置在第二绝缘层L2上。例如,第一绝缘层L1和第二绝缘层L2可以包括无机材料,并且第三绝缘层L3可以包括有机材料。第三绝缘层L3可以提供平坦表面。无机材料可以是例如氮化硅、氮氧化硅、氧化硅、氧化钛或氧化铝,但是本发明不限于此。

连接电极CCE可以设置在第三绝缘层L3上。连接电极CCE可以将第一输出电极OE1和第二控制电极CE2连接。可以在第二绝缘层L2和第三绝缘层L3中形成通孔,并且第一输出电极OE1可以被该通孔暴露。连接电极CCE可以电连接到暴露的第一输出电极OE1。可以在第一绝缘层至第三绝缘层L1、L2和L3中形成通孔,并且第二控制电极CE2可以被该通孔暴露。连接电极CCE可以电连接到暴露的第二控制电极CE2。

第一电极E1可以设置在第三绝缘层L3上。可以在第二绝缘层L2和第三绝缘层L3中形成通孔,并且第二输出电极OE2可以被该通孔暴露。第一电极E1可以电连接到暴露的第二输出电极OE2。

第二电极E2可以设置在第三绝缘层L3上。虽然未示出,但是第二电极E2可以电连接到第二电力线PL2(见图3)。即,第二电力电压ELVSS(见图3)可以被供应到第二电极E2。

连接电极CCE、第一电极E1和第二电极E2可以包括相同的导电材料。例如,导电材料可以包括选自氧化铟锌(IZO)、氧化铟锡(ITO)、氧化铟镓(IGO)、氧化铟锌镓(IGZO)及其混合物/复合物中的一种。然而,本发明不限于此。例如,导电材料可以是金属材料,并且金属材料可以包括例如钼、银、钛、铜、铝或其合金。

在本发明的一个示例性实施例中,第一电极E1和第二电极E2中的每个可以包括反射材料。因此,第一电极E1和第二电极E2可以反射从发光元件ED发射的光。例如,第一电极E1和第二电极E2中的每个可以包括反射电极和覆盖反射电极的盖电极。反射电极可以具有其中氧化铟锡(ITO)、银(Ag)和氧化铟锡(ITO)顺序堆叠的结构,盖电极可以包括氧化铟锌(IZO)并且可以覆盖反射电极。

凹槽GRV可以形成在第一绝缘层至第三绝缘层L1、L2和L3中。第一电极E1和第二电极E2可以延伸为设置在凹槽GRV中。发光元件ED可以设置在第一电极E1和第二电极E2上。发光元件ED可以电连接到第一电极E1和第二电极E2。像素发射区域PXA可以被限定为这样的区域:该区域包括与其中设置有发光元件ED的区域对应的区域。

在本发明的另一示例性实施例中,可以省略凹槽GRV,第一电极E1和第二电极E2可以设置在第三绝缘层L3上,并且发光元件ED可以设置于设置在第三绝缘层L3上的第一电极E1和第二电极E2上。

第一图案部分PT1可以设置于在平面图中与其中第一电极E1和发光元件ED彼此叠置的区域相邻的区域中,并且第二图案部分PT2可以设置于在平面图中与其中第二电极E2和发光元件ED彼此叠置的区域相邻的区域中。术语“在平面图中”可以指当在显示面板DP的厚度方向上(即,在第三方向DR3(见图1)上)观察显示面板DP时。下面将给出第一图案部分PT1和第二图案部分PT2的详细描述。

第一连接电极CNE1可以设置在第一图案部分PT1上,并且第一连接电极CNE1可以将发光元件ED和第一电极E1电连接。第二连接电极CNE2可以设置在第二图案部分PT2上,并且第二连接电极CNE2可以将发光元件ED和第二电极E2电连接。

第一连接电极CNE1和第二连接电极CNE2可以包括相同的导电材料。例如,导电材料可以包括选自氧化铟锌(IZO)、氧化铟锡(ITO)、氧化铟镓(IGO)、氧化铟锌镓(IGZO)及其混合物/复合物中的一种。然而,本发明不限于此。例如,导电材料可以是金属材料,并且金属材料可以包括例如钼、银、钛、铜、铝或其合金。

保护部分OPL可以设置在发光元件ED上。保护部分OPL可以覆盖发光元件ED的至少一部分以保护发光元件ED。保护部分OPL可以包括与第一图案部分PT1和第二图案部分PT2相同的材料,并且保护部分OPL、第一图案部分PT1和第二图案部分PT2可以通过同一工艺同时形成。第一图案部分PT1、第二图案部分PT2和保护部分OPL可以包括有机材料。另外,虽然未示出,但是覆盖层(未示出)、偏振功能层(未示出)、波长转换层(未示出)或滤色器(未示出)可以设置在保护部分OPL上。

图4b是示出根据本发明的一个示例性实施例的像素的剖视图。

参照图4b,缓冲层BFL可以设置在基体层BL上。

第一薄膜晶体管TR1a和第二薄膜晶体管TR2a中的每个可以设置在缓冲层BFL上。

第一薄膜晶体管TR1a可以包括第一控制电极CE1a、第一输入电极IE1a、第一输出电极OE1a和第一半导体图案SP1a。第二薄膜晶体管TR2a可以包括第二控制电极CE2a、第二输入电极IE2a、第二输出电极OE2a和第二半导体图案SP2a。

第一半导体图案SP1a和第二半导体图案SP2a可以设置在缓冲层BFL上。缓冲层BFL可以向第一半导体图案SP1a和第二半导体图案SP2a提供改性的表面。在这种情况下,与第一半导体图案SP1a和第二半导体图案SP2a直接形成在基体层BL上时相比,第一半导体图案SP1a和第二半导体图案SP2a对于缓冲层BFL可以具有较高的粘附性。可选地,缓冲层BFL可以是保护第一半导体图案SP1a和第二半导体图案SP2a中的每个的下表面的阻挡层。在这种情况下,缓冲层BFL可以阻挡引入到基体层BL自身中或通过基体层BL引入的污染物或湿气渗透到第一半导体图案SP1a和第二半导体图案SP2a中。

第一绝缘层L1a可以设置在缓冲层BFL上,并且可以覆盖第一半导体图案SP1a和第二半导体图案SP2a。第一绝缘层L1a可以包括无机材料。

第一控制电极CE1a和第二控制电极CE2a可以设置在第一绝缘层L1a上。第二绝缘层L2a可以设置在第一绝缘层L1a上,并且可以覆盖第一控制电极CE1a和第二控制电极CE2a。第二绝缘层L2a可以包括无机材料。信号线(例如,扫描线或数据线)中的至少一些可以设置在第二绝缘层L2a上。

第三绝缘层L3a可以设置在第二绝缘层L2a上,并且可以覆盖信号线中的至少一些。

第一输入电极IE1a、第一输出电极OE1a、第二输入电极IE2a和第二输出电极OE2a可以设置在第三绝缘层L3a上。第一输入电极IE1a和第一输出电极OE1a可以通过穿过第一绝缘层至第三绝缘层L1a、L2a和L3a的通孔连接到第一半导体图案SP1a。第二输入电极IE2a和第二输出电极OE2a可以通过穿过第一绝缘层至第三绝缘层L1a、L2a和L3a的通孔连接到第二半导体图案SP2a。

第四绝缘层L4a可以设置在第三绝缘层L3a上,并且可以覆盖第一输入电极IE1a、第一输出电极OE1a、第二输入电极IE2a和第二输出电极OE2a。第四绝缘层L4a可以设置为单层或多层,并且第四绝缘层L4a可以包括有机材料和/或无机材料。

第一分隔壁BR1和第二分隔壁BR2可以设置在第四绝缘层L4a上。第一分隔壁BR1和第二分隔壁BR2可以设置为彼此间隔开。

第一电极E1a可以覆盖第一分隔壁BR1,并且可以设置在第四绝缘层L4a上。可以在第四绝缘层L4a中形成通孔,并且第二输出电极OE2a可以被该通孔暴露。第一电极E1a可以电连接到暴露的第二输出电极OE2a。

第二电极E2a可以覆盖第二分隔壁BR2,并且可以设置在第四绝缘层L4a上。虽然未示出,但是第二电极E2a可以电连接到第二电力线PL2(见图3)。即,第二电力电压ELVSS(见图3)可以被供应到第二电极E2a。

发光元件ED可以设置在第一电极E1a和第二电极E2a上。发光元件ED可以电连接到第一电极E1a和第二电极E2a。

图4b示出了其中发光元件ED设置在第四绝缘层L4a上的示例,但是本发明不限于此。在本发明的另一示例性实施例中,凹槽(未示出)可以设置在第一绝缘层至第四绝缘层L1a、L2a、L3a和L4a中。凹槽的形状可以与图4a中所示的凹槽GRV的形状类似。第一电极E1a和第二电极E2a可以延伸为设置在被凹槽暴露的缓冲层BFL上,并且发光元件ED可以设置在延伸的第一电极E1a和第二电极E2a上。

图5a是根据本发明的一个示例性实施例的发光元件的剖视图。

参照图5a,发光元件ED可以具有各种形状,诸如圆柱形状和多边形柱形状。

发光元件ED可以包括N型半导体层SCN、P型半导体层SCP和活性层AL。活性层AL可以设置在N型半导体层SCN与P型半导体层SCP之间。

可以通过向半导体层中掺杂N型掺杂剂来提供N型半导体层SCN,并且可以通过向半导体层中掺杂P型掺杂剂来提供P型半导体层SCP。半导体层可以包括半导体材料,并且半导体材料可以是例如GaN、AlN、AlGaN、InGaN、InN、InAlGaN或AlInN,但不限于此。N型掺杂剂可以是硅(Si)、锗(Ge)、锡(Sn)、硒(Se)、碲(Te)或其组合,但不限于此。P型掺杂剂可以是镁(Mg)、锌(Zn)、钙(Ca)、锶(Sr)、钡(Ba)或其组合,但不限于此。

活性层AL可以形成为具有单量子阱结构、多量子阱结构、量子线结构和量子点结构中的至少一种。活性层AL可以是通过N型半导体层SCN注入的电子和通过P型半导体层SCP注入的空穴在其中复合的区域。活性层AL是发射具有由材料的本征能带所确定的能量的光的层。活性层AL的位置可以根据二极管的类型而各种地改变。

发光元件ED的长度LT可以在几纳米至几百微米的范围内。例如,发光元件ED的长度LT可以在1微米至100微米的范围内。

图5b是根据本发明的一个示例性实施例的发光元件的剖视图。

参照图5b,与图5a的发光元件ED相比,发光元件EDa还可以包括第一电极层ECL1和第二电极层ECL2。

第一电极层ECL1可以与N型半导体层SCN相邻,并且第二电极层ECL2可以与P型半导体层SCP相邻。例如,第一电极层ECL1、N型半导体层SCN、活性层AL、P型半导体层SCP和第二电极层ECL2可以顺序地堆叠。

第一电极层ECL1和第二电极层ECL2中的每个可以由金属或金属的合金制成。例如,第一电极层ECL1和第二电极层ECL2中的每个可以由选自钼(Mo)、铬(Cr)、镍(Ni)、金(Au)、铝(Al)、钛(Ti)、铂(Pt)、钒(V)、钨(W)、铅(Pd)、铜(Cu)、铑(Rh)和铱(Ir)中的至少一种金属制成,或者可以由所述金属的合金制成。第一电极层ECL1和第二电极层ECL2可以包括相同的材料或者也可以包括不同的材料。

图5c是根据本发明的一个示例性实施例的发光元件的剖视图。

参照图5c,与图5a的发光元件ED相比,发光元件EDb还可以包括绝缘膜IL。例如,发光元件EDb可以具有核壳结构。

绝缘膜IL可以覆盖N型半导体层SCN、P型半导体层SCP和活性层AL,以保护N型半导体层SCN、P型半导体层SCP和活性层AL的外表面。在本发明的另一示例性实施例中,绝缘膜IL也可以仅覆盖活性层AL。

图5d是根据本发明的一个示例性实施例的发光元件的剖视图。

参照图5d,与图5b的发光元件EDa相比,发光元件EDc还可以包括绝缘膜ILa。

绝缘膜ILa可以覆盖N型半导体层SCN、P型半导体层SCP和活性层AL,并且可以不覆盖第一电极EL1和第二电极EL2。然而,在本发明的另一示例性实施例中,绝缘膜ILa可以覆盖第一电极EL1和第二电极EL2中的至少一些或者可以覆盖第一电极EL1和第二电极EL2两者。

图6是根据本发明的一个示例性实施例的像素的平面图。具体地,图6可以是与像素发射区域PXA对应的部分的平面图。

第一电极E1和第二电极E2可以设置为彼此间隔开。发光元件ED的一部分可以与第一电极E1接触,并且发光元件ED的另一部分可以与第二电极E2接触。在平面图中,其中发光元件ED和第一电极E1彼此叠置的区域被定义为第一区域AR1,并且其中发光元件ED和第二电极E2彼此叠置的区域被定义为第二区域AR2。

第一图案部分PT1可以设置为与第一区域AR1相邻,并且第二图案部分PT2可以设置为与第二区域AR2相邻。第一图案部分PT1可以围绕第一区域AR1的至少一部分,并且第二图案部分PT2可以围绕第二区域AR2的至少一部分。例如,在平面图中,第一图案部分PT1可以围绕发光元件ED的一个端部,并且第二图案部分PT2可以围绕发光元件ED的另一端部。第一图案部分PT1和第二图案部分PT2可以包括有机材料。

多个发光元件ED可以设置在一个像素发射区域PXA中。多个发光元件ED可以彼此并联连接。在本发明的另一示例性实施例中,可以在一个像素发射区域PXA中仅设置单个发光元件ED。

第一连接电极CNE1可以在平面图中覆盖多个发光元件ED的一个端部。第二连接电极CNE2可以在平面图中覆盖多个发光元件ED的另一端部。另外,第一连接电极CNE1可以设置为与第一电极E1叠置,并且第二连接电极CNE2可以设置为与第二电极E2叠置。即,第一连接电极CNE1可以将多个发光元件ED的一个端部和第一电极E1电连接,并且第二连接电极CNE2可以将多个发光元件ED的另一端部和第二电极E2电连接。

保护部分OPL可以设置在第一电极E1与第二电极E2之间。保护部分OPL可以覆盖设置在像素发射区域PXA中的多个发光元件ED。保护部分OPL可以用于保护多个发光元件ED,并且保护部分OPL可以包括有机材料。

图7是沿着图6中所示的线I-I'截取的剖视图的示例,并且图8是沿着图6中所示的线II-II'截取的剖视图的示例。

参照图7和图8,第一电极E1和第二电极E2设置在基体绝缘层ILB上。基体绝缘层ILB可以是参照图4a描述的基体层BL或参照图4b描述的第四绝缘层L4a。

发光元件ED设置在第一电极E1和第二电极E2上。第一图案部分PT1可以设置在第一电极E1上,并且第二图案部分PT2可以设置在第二电极E2上。发光元件ED可以具有圆柱形状。因此,发光元件ED可以在图8中所示的剖面中具有圆形形状。

第一图案部分PT1可以具有第一倾斜表面SLP1,并且第二图案部分PT2可以具有第二倾斜表面SLP2。图7示出了将第一图案部分PT1中具有最大高度的点和第一图案部分PT1的端部连接的第一倾斜表面SLP1。第一倾斜表面SLP1可以具有多个梯度。例如,第一倾斜表面SLP1可以具有曲率。第一图案部分PT1的端部可以表示第一图案部分PT1的在其处第一倾斜表面SLP1和第一电极E1彼此接触的端部。第二图案部分PT2的第二倾斜表面SLP2也可以具有多个梯度。

第一连接电极CNE1可以设置在发光元件ED、第一电极E1和第一图案部分PT1上,并且第二连接电极CNE2可以设置在发光元件ED、第二电极E2和第二图案部分PT2上。

第一连接电极CNE1可以与第一倾斜表面SLP1接触,并且第二连接电极CNE2可以与第二倾斜表面SLP2接触。在第一连接电极CNE1中,可以限定覆盖发光元件ED的上表面的一部分和发光元件ED的侧表面的一部分的第一部分POT1、以及覆盖第一图案部分PT1的第二部分POT2以及覆盖第一电极E1的一部分的第三部分POT3。第一部分POT1可以与发光元件ED接触,第二部分POT2可以与第一倾斜表面SLP1接触,并且第三部分POT3可以与第一电极E1接触。

根据其中未设置第一图案部分PT1的对比示例,对比连接电极CNE-C可以沿着发光元件ED的外表面形成。为了便于理解,在图8中用虚线示出了对比连接电极CNE-C。对比连接电极CNE-C与第二电极E2的接触部分同对比连接电极CNE-C与发光元件ED的接触部分之间的部分可以具有弯折形状。另外,虽然未示出,但是在图7的剖面中,对比连接电极CNE-C与发光元件ED的接触部分同对比连接电极CNE-C与第一电极E1的接触部分之间的角度可能接近90°。

当省略第一图案部分PT1和第二图案部分PT2时,对比连接电极CNE-C会断开,以致不将第一电极E1和发光元件ED连接或者会在对比连接电极CNE-C中产生裂纹从而使对比连接电极CNE-C的电阻增大。当对比连接电极CNE-C断开时,发光元件ED不会发光,并且当在对比连接电极CNE-C中产生裂纹时,发光元件ED的发光效率会降低。为了解决这样的问题,当对比连接电极CNE-C形成为相对厚时,图案化对比连接电极CNE-C的蚀刻工艺的工艺时间会增加,由于工艺时间会增加,所以会发生蚀刻歪斜。当图案均匀性由于蚀刻歪斜而降低时,元件的特性会改变。具体地,在精细图案工艺的情况下,图案会由于蚀刻歪斜而断开。

根据本发明的一个示例性实施例,第一图案部分PT1设置在第一连接电极CNE1与发光元件ED之间。第一连接电极CNE1的梯度的改变由于第一图案部分PT1而可以是相对平缓的。因此,能够减少其中第一连接电极CNE1由于梯度的突然改变而断开或破裂的现象。因此,第一连接电极CNE1可以形成得比对比连接电极CNE-C薄。结果,还可以减少图案化第一连接电极CNE1的蚀刻工艺的工艺时间。由于蚀刻工艺的工艺时间减少,蚀刻歪斜的概率也可以减少,这在形成精细图案方面会是有利的。由于第二图案部分PT2具有与第一图案部分PT1的形状基本相同的形状,因此省略对第二图案部分PT2的描述。在本说明书中,梯度的改变是平缓的表示彼此不同的第一梯度与第二梯度之间的差是减小的。

第一图案部分PT1和第二图案部分PT2中的每个的最大高度TK-P可以小于发光元件ED的厚度TK-E。最大高度TK-P可以与第一图案部分PT1和第二图案部分PT2中的每个在其处与发光元件ED接触的部分的高度对应。例如,第一图案部分PT1和第二图案部分PT2中的每个的最大高度TK-P可以是发光元件ED的厚度TK-E的50%或更小。当第一图案部分PT1和第二图案部分PT2中的每个的高度增加时,发光元件ED与第一连接电极CNE1的接触面积以及发光元件ED与第二连接电极CNE2的接触面积会减小,这会导致发光效率的降低。因此,考虑到这一点,最大高度TK-P可以在发光元件ED的厚度TK-E的1%至50%的范围内。

第一倾斜表面SLP1与第一电极E1之间的角度DG1以及第二倾斜表面SLP2与第二电极E2之间的角度DG2可以是70°或更小。随着角度DG1和DG2增大,第一连接电极CNE1和第二连接电极CNE2中的每个的第二部分POT2与第三部分POT3之间的梯度会突然改变。梯度的突然改变会导致第一连接电极CNE1和第二连接电极CNE2的裂纹或断开。考虑到这一点,角度DG1和DG2可以在1°至70°的范围内。

根据本发明的一个示例性实施例,由于第一图案部分PT1和第二图案部分PT2,可以防止其中第一连接电极CNE1和第二连接电极CNE2断开或破裂的现象。结果,可以改善产品制造良率,并且发光元件ED可以稳定地结合到第一电极E1和第二电极E2,从而改善产品可靠性。

图9是沿着图6的线II-II'截取的剖视图的示例。

参照图9,发光元件ED-1可以具有多边形柱形状。例如,发光元件ED-1可以具有矩形柱形状。在发光元件ED-1的一侧与第二电极E2之间形成的角度AG-1可以是90°。

根据本发明的示例性实施例,图案部分PT-1设置在发光元件ED-1与连接电极CNE-1之间。连接电极CNE-1的梯度在其处突然改变的部分可以由于图案部分PT-1而被去除。例如,当省略图案部分PT-1时,连接电极CNE-1的梯度会从第一部分POT1-1的梯度直接改变为第三部分POT3-1的梯度。然而,根据本发明的示例性实施例,连接电极CNE-1的梯度可以从第一部分POT1-1的梯度改变为第二部分POT2-1的梯度,然后可以改变为第三部分POT3-1的梯度。

图10是沿着图6中所示的线II-II'截取的剖视图的示例。

参照图10,发光元件ED-2可以具有多边形柱形状。例如,发光元件ED-2可以具有梯形柱形状。在发光元件ED-2的一侧与第二电极E2之间形成的角度AG-2可以是70°。

在本发明的一个示例性实施例中,当角度AG-2在60°至180°的范围内时,例如,在70°至180°的范围内时,可以应用图案部分PT-2。当角度AG-2增大时,连接电极CNE-2的梯度会突然改变。因此,可以通过应用图案部分PT-2来使连接电极CNE-2的梯度的改变平缓。

图11a至图11h是示出根据本发明的一个示例性实施例的制造显示装置的工艺中的一些工艺的视图。

参照图11a,在基体绝缘层ILB上形成第一电极E1和第二电极E2。

将发光元件ED设置或转移到第一电极E1和第二电极E2上。例如,可以提供多个发光元件ED,可以同时转移多个发光元件ED,或者可以逐个转移单个发光元件ED。

将发光元件ED转移到第一电极E1和第二电极E2上的方法可以包括直接转移法和印刷转移法。直接转移法可以是将发光元件ED直接转移到第一电极E1和第二电极E2的方法。印刷转移法可以是使用静电头、平印模或辊印模将发光元件ED转移到第一电极E1和第二电极E2的方法。另外,可以将包含发光元件ED的溶剂(诸如墨水或浆糊)供应到第一电极E1和第二电极E2上以转移发光元件ED。溶剂可以是在室温下可以蒸发或通过加热可以蒸发的材料。向第一电极E1和第二电极E2施加电力,以在第一电极E1与第二电极E2之间形成电场。可以通过电场在发光元件ED中引起双极性,并且可以通过介电泳力使发光元件ED在第一电极E1和第二电极E2上对准。

形成覆盖发光元件ED、第一电极E1和第二电极E2的有机层OL。可以通过涂覆工艺形成有机层OL,并且形成有机层OL的工艺不限于此。有机层OL可以是光致抗蚀剂层。

参照图11b,在有机层OL上设置掩模MK。掩模MK可以是包括半透明部分HTP、透明部分TP和遮光部分BP的半色调掩模。

有机层OL可以是正性光致抗蚀剂层或负性光致抗蚀剂层。在图11b中,作为示例描述了其中有机层OL是正性光致抗蚀剂层的情况。

半透明部分HTP的至少一部分可以在平面图中与第一电极E1和第二电极E2叠置。遮光部分BP可以设置为与发光元件ED的不与第一电极E1和第二电极E2叠置的部分叠置。透明部分TP可以设置在其他区域中。在将掩模MK设置在有机层OL上之后,照射光。

参照图11c,将曝光的有机层OL(见图11b)显影以形成有机图案OP。有机图案OP可以包括第一有机图案部分OP1和第二有机图案部分OP2。第一有机图案部分OP1可以是由于光被阻挡而保留的部分,并且第二有机图案部分OP2可以是其中由于部分地照射光而在有机层OL(见图11b)的厚度方向上去除了有机层OL的一部分的部分。形成有机图案OP,然后烘烤有机图案OP。

第二有机图案部分OP2的设置在发光元件ED上的部分的厚度TKx可以不同于第二有机图案部分OP2的设置在第一电极E1和第二电极E2上的部分的厚度TKy。第二有机图案部分OP2的厚度差可以由于由发光元件ED形成的台阶部分而产生。

参照图11d和图11e,示出了去除有机图案OP的一部分的操作。图11d示出了其中有机图案OP(见图11c)的一部分正在被去除的状态,并且图11e示出了其中有机图案OP的一部分被完全去除的状态。

可以使用灰化工艺来去除有机图案OP的一部分。可以使第一有机图案部分OP1-s的厚度和第二有机图案部分OP2-s的厚度逐渐减小。

第二有机图案部分OP2-s的一部分可以由于第二有机图案部分OP2-s的各自区域的厚度差异而保留而不被去除。剩余部分可以构成第一图案部分PT1和第二图案部分PT2。第一有机图案部分OP1-s的厚度可以减小以构成保护部分OPL。第一图案部分PT1、第二图案部分PT2和保护部分OLP可以通过同一工艺同时形成。

图11f是图11e的平面图。第一图案部分PT1可以通过围绕发光元件ED的一个端部而保留,并且第二图案部分PT2可以通过围绕发光元件ED的另一端部而保留。

保护部分OPL可以覆盖发光元件ED的上表面的至少一部分。保护部分OPL可以用于防止发光元件ED的阵列扭曲,并且保护部分OPL还可以用于在后续工艺期间保护发光元件ED。

参照图11g,在形成保护部分OPL、第一图案部分PT1和第二图案部分PT2之后,形成导电层MTL。导电层MTL可以包括选自氧化铟锌(IZO)、氧化铟锡(ITO)、氧化铟镓(IGO)、氧化铟锌镓(IGZO)及其混合物/复合物中的一种。然而,本发明不限于此。例如,导电层MTL可以包括钼、银、钛、铜、铝或其合金。

参照图11h,图案化导电层MTL,以形成第一连接电极CNE1和第二连接电极CNE2。根据本发明的示例性实施例,第一连接电极CNE1和第二连接电极CNE2的梯度的改变可以由于第一图案部分PT1和第二图案部分PT2而是平缓的。因此,能够减少其中第一连接电极CNE1和第二连接电极CNE2断开或破裂的现象。由于降低了断开或裂纹发生的可能性,所以可以减小第一连接电极CNE1和第二连接电极CNE2的厚度。因此,可以减少蚀刻工艺的工艺时间,这对于精细图案制造工艺会是有利的。

图12a至图12g是示出根据本发明的一个示例性实施例的制造显示装置的工艺中的一些工艺的视图。在参照图12a至图12g的描述中,将详细描述与图11a至图11f中的部分不同的部分,相同的附图标记将用于相同的组件,并且将省略对相同组件的描述。

参照图12a,形成覆盖发光元件ED、第一电极E1和第二电极E2的无机层IOL,并且在形成无机层IOL之后形成有机层OL。

参照图12b,在有机层OL上设置掩模MK,并且将光照射到有机层OL上。

参照图12c,将曝光的有机层OL显影以形成有机图案OP。有机图案OP可以设置在无机层IOL上。

参照图12d,灰化有机图案OP以形成有机保护部分OPLa、第一图案部分PT1a和第二图案部分PT2a。有机保护部分OPLa可以被称为第二保护部分。

参照图12e,去除无机层IOL(见图12d)的未被有机保护部分OPLa、第一图案部分PT1a和第二图案部分PT2a覆盖的部分。可以去除无机层IOL的一部分以形成第一无机图案部分IPT1、第二无机图案部分IPT2和无机保护部分IOPLa。即,可以通过同一工艺同时形成第一无机图案部分IPT1、第二无机图案部分IPT2和无机保护部分IOPLa。无机保护部分IOPLa可以被称为第一保护部分。保护部分PTP可以包括第二保护部分OPLa和包含无机材料的第一保护部分IOPLa。

第一无机图案部分IPT1可以设置在第一图案部分PT1a下面,并且第二无机图案部分IPT2可以设置在第二图案部分PT2a下面。例如,第一无机图案部分IPT1可以设置在第一图案部分PT1a与发光元件ED之间以及第一图案部分PT1a与第一电极E1之间,并且第二无机图案部分IPT2可以设置在第二图案部分PT2a与发光元件ED之间以及第二图案部分PT2a与第二电极E2之间。

参照图12f和图12g,形成导电层MTL。导电层MTL可以覆盖第一电极E1、第二电极E2、第一图案部分PT1a、第二图案部分PT2a、第一无机图案部分IPT1、第二无机图案部分IPT2、第一保护部分IOPLa和第二保护部分OPLa中的全部。

图案化导电层MTL以形成第一连接电极CNE1和第二连接电极CNE2。第一连接电极CNE1可以将发光元件ED和第一电极E1电连接,并且第二连接电极CNE2可以将发光元件ED和第二电极E2电连接。

在图12f和图12g中,已经描述了同时形成第一连接电极CNE1和第二连接电极CNE2,但是本发明不限于此。例如,在本发明的另一示例性实施例中,图案化导电层MTL以形成第一连接电极CNE1,并且形成覆盖第一连接电极CNE1的绝缘层(未示出)。之后,可以在绝缘层上形成导电层,并且可以图案化该导电层以形成第二连接电极CNE2。即,第一连接电极CNE1和第二连接电极CNE2可以不同时形成。

根据本发明的示例性实施例,第一连接电极CNE1和第二连接电极CNE2的梯度的改变可以由于第一图案部分PT1a和第二图案部分PT2a而平缓。因此,能够减少其中第一连接电极CNE1和第二连接电极CNE2中的每个断开或破裂的现象。另外,由于降低了断开或裂纹发生的可能性,所以可以减小第一连接电极CNE1和第二连接电极CNE2的厚度。因此,可以减少蚀刻工艺的工艺时间,这对于精细图案制造工艺会是有利的。

尽管已经参照示例性实施例描述了本发明,但是理解的是,本领域普通技术人员可以在如下文中所要求保护的本发明的精神和范围内对本发明进行各种改变和修改。因此,本发明的技术范围不限于在此描述的示例性实施例,而是应当由权利要求来确定。

工业实用性

由于在将发光元件和电极连接的连接电极中产生的裂纹,发光元件与电极之间的电阻会增加,这会导致发光效率降低。本发明提供了一种在发光元件与电极之间具有改善的连接稳定性的显示装置以及用于制造该显示装置的方法。因此,显示装置以及与该显示装置相关的本发明具有高的工业实用性。

- 显示装置用基板、显示装置用基板的制造方法、显示装置、液晶显示装置、液晶显示装置的制造方法和有机电致发光显示装置

- 薄膜晶体管用感光性树脂组合物、固化膜、薄膜晶体管、液晶显示装置或有机场致发光显示装置、固化膜的制造方法、薄膜晶体管的制造方法以及液晶显示装置或有机场致发光显示装置的制造方法