存储器系统中的动态链路差错保护

文献发布时间:2024-04-18 19:48:15

本申请是申请日为2018年6月28日、申请号为201880053866.5的题为“存储器系统中的动态链路差错保护”的发明专利申请的分案申请。

技术领域

所公开的主题内容的领域涉及存储器系统。具体而言,所公开的主题内容的领域涉及存储器系统中的动态链路差错保护。

背景技术

在主机与存储器之间的数据传递中可存在差错。随着存储器链路操作变得更快以满足更高的带宽要求,存储器设备与主机(例如,片上系统(SoC)、CPU)之间的链路中的数据传输差错的概率变得更大。一个原因是高速链路更容易受到时钟抖动、PDN(功率递送网络)噪声等的影响。

为了增强可靠性,可以将差错保护方案应用于存储器链路。例如,常规存储器子系统可以包括主机侧的纠错码(ECC)编码器和解码器以及存储器设备侧的互补ECC编码器和解码器。当主机希望将数据写入存储器设备时,主机发送写命令并通过链路向存储器设备提供写数据。为了保护写数据,主机侧的ECC编码器在通过链路发送写数据之前对写数据进行编码。存储器设备侧的ECC解码器对经编码的写数据进行解码,并且将经解码的写数据存储在存储器设备的存储器单元中。

当主机希望从存储器设备读取数据时,主机通过链路向存储器设备发送读命令。存储器设备从存储器单元检索读数据,并通过链路将检索到的读数据发送到主机。为了保护读数据,存储器设备的ECC编码器在将读数据发送给主机之前对读数据进行编码。主机侧的ECC解码器对经编码的读数据进行解码,并且将经解码的读数据提供给请求方(诸如,CPU)。

遗憾的是,提供这样的保护方案通常会由于编码和解码开销而增加性能等待时间。此外,在移动系统中可能特别重要的是需要附加功率。

发明内容

本概述标识了一些示例方面的特征,并且不是对所公开的主题内容的排他性或穷尽性描述。各特征或各方面是被包括在本概述中还是从本概述中省略不旨在指示这些特征的相对重要性。描述了附加特征和方面,并且这些附加特征和方面将在阅读以下详细描述并查看形成该详细描述的一部分的附图之际变得对本领域技术人员显而易见。

公开了一种示例性装置。该装置可包括存储器设备,其被配置为通过链路与主机进行通信。该存储器设备可包括多个存储器单元和存储器链路接口。该存储器链路接口可以被配置为通过链路从主机接收读命令或写命令。响应于读命令,存储器链路接口可以被配置为从多个存储器单元检索读数据,并根据所应用的链路保护模式通过链路向主机提供读数据。响应于写命令,存储器链路接口可以被配置为通过链路从主机接收写数据,并根据所应用的链路保护模式将写数据存储到多个存储器单元。该存储器设备可以被配置为实现包括第一链路保护模式和第二链路保护模式的多个链路保护模式。可应用链路保护模式而以不同的保护级别保护通过链路传送的读数据或写数据免于差错。该存储器设备可以被配置为响应于从主机收到的链路保护模式改变通知而从应用第一链路保护模式改变为应用第二链路保护模式。

公开了另一示例性装置。该装置可包括主机,其被配置为通过链路与存储器设备进行通信。该主机可以包括主机链路接口,其被配置为与链路对接;以及存储器控制器,其被配置为通过主机链路接口与存储器设备进行通信。该存储器控制器可以被配置为通过链路向存储器设备发出读命令或写命令。在发出读命令之际,存储器控制器可以被配置为根据所应用的链路保护模式通过链路从存储器设备接收读数据。在发出写命令之际,存储器控制器可以被配置为根据所应用的链路保护模式通过链路向存储器设备提供写数据。该主机可以被配置为实现包括第一链路保护模式和第二链路保护模式的多个链路保护模式。可应用链路保护模式而以不同的保护级别保护通过链路传送的读数据或写数据免于差错。该主机可以被配置为响应于链路速度改变而从应用第一链路保护模式改变为应用第二链路保护模式。

公开了一种装置的示例性方法。该装置可包括被配置为通过链路彼此通信的主机和存储器设备。该方法可以包括响应于链路速度改变而将装置从应用第一链路保护模式改变为应用第二链路保护模式。该方法可以包括由主机通过链路向存储器设备发出读命令,并且响应于该读命令,根据所应用的链路保护模式由存储器设备通过链路向主机提供读数据。该方法可以包括由主机通过链路向存储器设备发出写命令,并且在发出该写命令之际,根据所应用的链路保护模式由主机通过链路向存储器设备提供写数据。该装置可以被配置为实现包括第一和第二链路保护模式的多个链路保护模式。可应用链路保护模式而以不同的保护级别保护通过链路传送的读数据或写数据免于差错。

公开了又一示例性装置。该装置可包括被配置为通过链路彼此通信的主机和存储器设备。该存储器设备可包括多个存储器单元。该存储器设备可以包括用于通过链路从主机接收读命令的装置,用于响应于读命令从多个存储器单元检索读数据的装置,以及用于响应于读命令,根据所应用的链路保护模式通过链路向主机提供读数据的装置。替换地或附加地,该存储器设备可以包括用于通过链路从主机接收写命令的装置,用于响应于写命令通过链路从主机接收写数据的装置,以及用于响应于写命令,根据所应用的链路保护模式将写数据存储到多个存储器单元的装置。该主机可以包括用于通过链路向存储器设备发出读命令的装置,以及用于在发出读命令之际通过链路从存储器设备接收读数据的装置。替换地或附加地,该主机可以包括用于通过链路向存储器设备发出写命令的装置,以及用于在发出写命令之际,根据所应用的链路保护模式通过链路向存储器设备提供写数据的装置。该装置可以被配置为实现包括第一链路保护模式和第二链路保护模式的多个链路保护模式。可应用链路保护模式而以不同的保护级别保护通过链路传送的读数据或写数据免于差错。该装置可以被配置为响应于链路速度改变而从应用第一链路保护模式改变为应用第二链路保护模式。

附图说明

给出附图以帮助对所公开的主题内容的一个或多个方面的示例进行描述,并且提供这些附图仅仅是为了解说各示例而非对其进行限制:

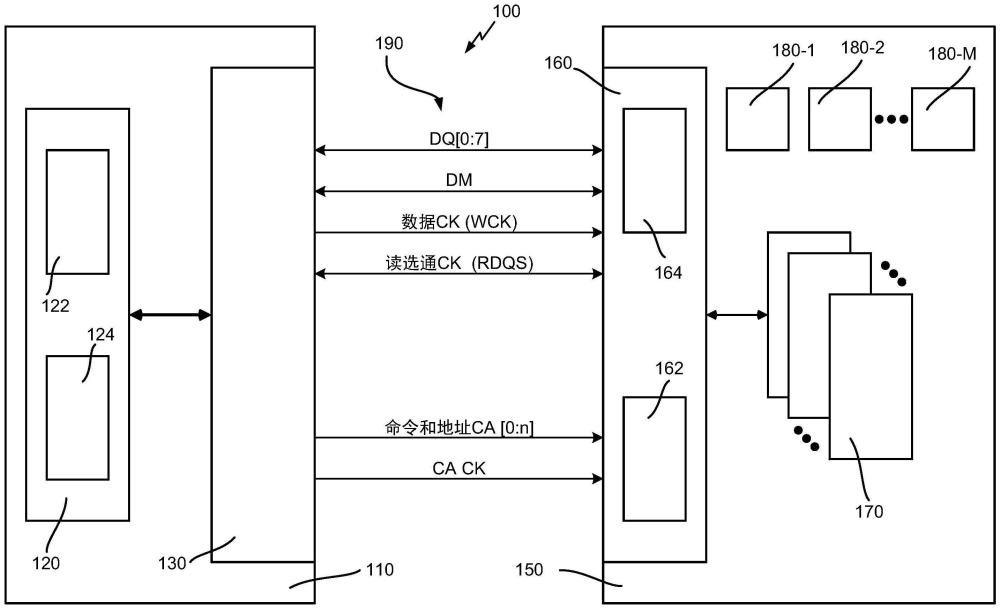

图1解说了示例存储器子系统的示图;

图2解说了用于实现频率设定点寄存器的模式寄存器的示例;

图3解说了频率设定点寄存器针对不同链路速度的设置的示例;

图4解说了动态改变链路保护模式的示例方法的流程图;

图5解说了用于执行读操作的示例方法的流程图;

图6解说了用于执行写操作的示例方法的流程图;以及

图7解说了其中集成有存储器子系统的设备的示例。

具体实施方式

主题内容的各方面在以下针对所公开的主题内容的特定示例的描述和相关附图中提供。可以设计出替换方案而不会脱离所公开的主题内容的范围。另外,众所周知的元素将不被详细描述或将被省去以免混淆相关细节。

措辞“示例性”在本文中用于表示“用作示例、实例、或解说”。本文中描述为“示例性”的任何实施例不必被解释为优于或胜过其他实施例。同样,术语“实施例”并不要求所公开主题内容的所有实施例都包括所讨论的特征、优点、或操作模式。

本文所使用的术语仅出于描述特定示例的目的,而并不旨在限定。如本文所使用的,单数形式的“一”、“某”和“该”旨在也包括复数形式,除非上下文另有明确指示。还将理解,术语“包括”、“具有”、“包含”和/或“含有”在本文中使用时指明所陈述的特征、整数、过程、操作、元素、和/或组件的存在,但并不排除一个或多个其他特征、整数、过程、操作、元素、组件和/或其群组的存在或添加。

此外,许多示例以将由例如计算设备的元件执行的动作序列的形式来描述。将认识到,本文中所描述的各种动作能由专用电路(例如,专用集成电路(ASIC))、由正被一个或多个处理器执行的程序指令、或由这两者的组合来执行。另外,本文描述的这些动作序列可被认为是完全体现在任何形式的计算机可读存储介质内,该计算机可读存储介质内存储有一经执行就将使相关联的处理器执行本文所描述的功能性的对应计算机指令集。由此,各个方面可以用数种不同的形式来体现,所有这些形式都已被构想落在所要求保护的主题内容的范围内。另外,对于本文描述的每个示例,任何此类示例的对应形式可在本文中被描述为例如“被配置成执行所描述的动作的逻辑”。

本公开的一个或多个方面可应用于移动或计算系统中的低功率存储器子系统,以用检错和/或纠错码来保护高速存储器链路(接口)。例如,一个或多个方面可与移动或计算芯片组中的下一代低功率DDR SPEC和DDR PHY相关。

在一个或多个方面,提议在主机和存储器设备两者中结合编码和解码能力(例如,ECC、汉明单纠错双检错(SECDED)、奇偶校验等)。与常规存储器子系统不同,提议包括范围从无链路差错保护到全链路差错保护以及其间的任意点(即,部分链路差错保护)的动态链路差错保护切换方案。通过将动态链路差错保护方案纳入存储器设备中以及主机中,可解决与常规技术相关联的一些或全部问题。例如,可以动态地调整所提供的链路差错保护的级别,以便可以在提供链路差错保护的利益和成本之间进行最佳权衡。

图1解说了提供动态链路差错保护的所提出的存储器子系统100的示例。该存储器子系统100可以包括通过链路190进行通信的片上系统(SoC)110和存储器设备150。这是简化的解说,其中示出了单个存储器设备150。然而,单个SoC 110可以与多个存储器设备150进行通信。在一些示例中,SoC 110可以是用于移动设备的处理器或应用处理器。该SoC 110可以被称为主机110,用于向存储器设备150提供存储器命令。

在一些示例中,链路190可以在主机110和存储器设备150之间提供芯片到芯片链路。例如,链路190可以包括多个信号线,包括用于从主机110向存储器设备150传送单向信号(例如,时钟(CK)、芯片选择(CS)、命令和地址(CA)等等)和双向定向信号(数据(DQ)、数据选通(DQS)等等)的线。主机110和存储器设备150之间的信令可以根据JEDEC DRAM规范。

主机110可以包括存储器控制器120、主机链路接口130(例如,存储器PHY块)、主机编码器122和主机解码器124。虽然未解说,但是主机110还可以包括其他组件,诸如数字信号处理器(DSP)、图形处理单元(GPU)、多媒体引擎和向存储器控制器120发送读和写请求的多核中央处理单元(CPU)。

存储器控制器120可以通过主机链路接口130向存储器设备150发出读和写命令,例如,以满足从DSP、GPU等收到的请求。当存储器控制器120发出读命令时,它可以从主机链路接口130接收读数据,并且进而将读数据发送给请求方。当存储器控制器120发出写命令时,它可以从请求方接收写数据,并且进而将写数据提供给主机链路接口130。

在读操作期间,主机链路接口130可以代表存储器控制器120通过链路190将读命令发送到存储器设备150。随后,主机链路接口130可通过链路190从存储器设备150接收读数据,并将收到的读数据提供给存储器控制器120。读数据可以是经编码的或未经编码的。如果读数据是经编码的,则主机解码器124可以解码读数据,并且存储器控制器120可以将经解码的读数据发送到请求方。主机解码器124还可以检测甚至纠正可能存在于读数据中的差错。例如,主机解码器124可以纠正可能在读数据的传输中引入的一个或多个比特差错。存储器控制器120可以被配置为将经纠正的读数据发送回请求方。

在写操作期间,主机链路接口130可以代表存储器控制器120通过链路190将写命令和写数据发送到存储器设备150。当被启用时,主机编码器122(例如,ECC、汉明SECDEC、奇偶校验等)可以对写数据进行编码,使得经编码的写数据通过链路190被发送。对写数据进行编码允许存储器设备150检测甚至纠正写数据中可能存在的差错。例如,可以纠正在写数据通过链路190的传输中引入的一个或多个比特差错。

在图1中,主机编码器122和主机解码器124被解说为纳入存储器控制器120中。这仅仅是示例,并且不应被视为限定。可以构想,主机编码器122和/或主机解码器124可以是独立的或被纳入主机110内的其他组件(诸如,主机链路接口130)中。此外,虽然个体地解说了主机编码器122和主机解码器124,但两者可被实现在单个设备中。还可以构想,主机编码器122和/或主机解码器124可被实现在多个设备中。实际上,在某个(些)方面,主机编码器122和/或主机解码器124的实现可散布在主机110内的多个组件之中。

存储器设备150可包括存储器链路接口160(例如,输入/输出(I/O)块)、一个或多个存储器组170、存储器编码器162、以及存储器解码器164。该存储器组170可包括多个存储器单元。存储器链路接口160可以通过链路190从主机110接收读和写命令。当存储器链路接口160接收读命令时,它可以向主机110提供读数据。当存储器链路接口160接收写命令时,它还可以从主机110接收写数据。

在读操作期间,存储器链路接口160可通过链路190从主机110接收读命令。响应于该读命令,存储器链路接口160可从在存储器组170中的多个存储器单元检索读数据,并将所检索的读数据通过链路190提供给主机110。当被启用时,存储器编码器162可以对读数据进行编码,使得经编码的读数据通过链路190被发送。对读数据进行编码允许主机110检测甚至纠正读数据中可能存在的差错。

在写操作期间,存储器链路接口160可通过链路190从主机110接收写命令和写数据。响应于写命令,存储器链路接口160可以将写数据存储在存储器组170(例如,多个存储器单元)中。写数据可以是经编码的或未经编码的。如果写数据是经编码的,则存储器解码器164可以解码写数据,并且存储器链路接口160可以将经解码的写数据存储在存储器组170中。存储器解码器164还可以检测甚至纠正可能在写数据中存在的差错,并且存储器链路接口160可以将经纠正的写数据存储在存储器组170中。

在图1中,存储器编码器162和存储器解码器164被解说为纳入存储器链路接口160中。这仅仅是示例,并且不应被视为限定。可以构想,存储器编码器162和/或存储器解码器164可以是独立的或被纳入存储器设备150内的其他组件中。此外,虽然个体地解说了存储器编码器162和存储器解码器164,但两者可被实现在单个设备中。还可以构想,存储器编码器162和/或存储器解码器164可被实现在多个设备中。实际上,在某个(些)方面,存储器编码器162和/或存储器解码器164的实现可散布在多个组件之中。

在一方面,主机编码器122和存储器编码器162可操作用于:当被提供有相同的未经编码数据时生成经相同地编码的写数据和读数据(例如,相同的ECC)。在另一方面,也有可能写数据可以与读数据被不同地编码。然而,只要存储器和主机解码器164、124分别与主机和存储器编码器122、162互补地操作,就可以进行正确的数据交换。

如上所指示,提议将动态链路差错保护切换能力纳入存储器子系统100中。在一方面,所提议的技术使得能够动态地调整链路差错保护级别,以便可基于操作环境提供适当的保护量。例如,链路差错的概率可以与链路190上的操作速度强相关。因此,可基于链路速度动态地调整链路差错保护的级别。也就是说,当存储器子系统100的链路速度改变时,链路差错保护的级别也可以适当地改变。链路差错保护的级别可以在无保护和完全保护之间的任何范围内。

为了便于讨论,将假设存储器子系统100可以实现可被应用于防止链路190上的差错的多个链路保护模式。例如,每个链路保护模式可以包括多个保护参数并定义应用于保护通过链路190传送的读数据和写数据免于差错的保护级别。随后,当链路速度从第一链路速度变为第二链路速度时,存储器子系统100可以从应用第一链路保护模式变为应用第二链路保护模式。换而言之,所应用的链路保护改变。

回想起可编码读数据和写数据中的一者或两者。在存储器设备150处对读数据进行编码允许主机110检测和/或纠正通过链路190传送的读数据中的任何差错。相反,在主机110处对写数据进行编码允许存储器设备150检测和/或纠正通过链路190传送的写数据中的任何差错。因此,在一方面,每个链路保护模式可以指定读差错检测参数、读差错纠正参数、写差错检测参数、写差错纠正参数中的每一者是否被启用/禁用。读差错检测参数可以是用于指示是否应检测读数据中的(诸)差错的保护参数,读差错纠正参数可以是用于指示是否应纠正读数据中(诸)差错的保护参数,写差错检测参数可以是用于指示是否应检测写数据中的(诸)差错的保护参数,写差错纠正参数可以是用于指示是否应纠正写数据中(诸)差错的保护参数。在该方面,每个链路保护模式可以指定保护参数被启用/禁用的不同组合。

提供示例场景以实现更详细的理解。假设在第一示例场景中,存储器子系统100是具有数据时钟(WCK)的低功率双倍数据率5(LPDDR5)存储器子系统,其可以在20Mhz到3.2Ghz之间的频率中操作,这转换为速度范围在40Mbps到6400Mbps之间的链路传输。如果链路190以低速(例如,WCK处于或低于1.6Ghz)操行,则在链路190上发生传输差错的机会可以足够低,使得未经编码的数据(读数据、写数据)可以充分的可靠性被传送。在可以可靠地传送未经编码数据的这种操作环境中,实现链路差错保护最多只能提供传输可靠性的微小改进,使得实现链路差错保护的成本可能超过收益。

因此,在第一示例场景下的低链路速度环境中,可以完全关闭(即完全禁用)保护。例如,对应于低链路速度的链路保护模式可以指定所有保护参数(读差错检测参数、读差错纠正参数、写差错检测参数和写差错纠正参数)被禁用。如果低速链路保护模式是所应用的链路保护模式,则主机编码器122、主机解码器124、存储器编码器162和存储器解码器164都可以被禁用,并且未经编码的读数据和写数据可以通过链路190被传送。通过禁用主机编码器122、主机解码器124、存储器编码器162和存储器解码器164,可以避免功率和等待时间惩罚。

在另一极端,如果链路190以高速(例如,WCK高于1.6Ghz)操作,则在链路190上发生传输差错的机会可使得未经编码的数据不可能通过链路190以充分的可靠性被传送。在无法通过链路190可靠地传送未经编码数据的这种操作环境中,实现链路差错保护可以提高传输可靠性,从而证明成本(例如,开销、功率等)是合理的。

因此,在第一示例场景下的高链路速度环境中,链路差错保护可被完全启用。例如,高速链路保护模式可以指定所有保护参数(读差错检测参数、读差错纠正参数、写差错检测参数和写差错纠正参数)被启用。如果该高速链路保护模式是所应用的链路保护模式,则对于读操作,可使存储器编码器162能够对通过链路190提供的读数据进行编码,并且可使主机解码器124能够对经编码的读数据进行解码。在一方面,可以使得主机解码器124能够检测在经编码的读数据中是否存在任何差错(例如,比特差错)。如果没有差错被检测到,则可将经解码的读数据提供给请求方。在另一方面,即使在经编码的读数据中存在差错,也可使主机解码器124能够纠正差错,使得可将经纠正的读数据提供给请求方。主机解码器124可以纠正达特定数目(读阈值数目)的差错。

对于写操作,当所应用的链路保护模式是高速链路保护模式时,可使主机编码器122能够对通过链路190提供的写数据进行编码,并且可使存储器解码器164能够对经编码的写数据进行解码,使得可将经解码的写数据存储在存储器组170的多个存储器单元中。在一方面,可以使得存储器解码器164能够检测在经编码的写数据中是否存在任何差错(例如,比特差错)。如果没有差错被检测到,则可以存储经解码的写数据。在另一方面,即使在检测到差错时,也可以使存储器解码器164能够纠正差错,从而可以存储经纠正的写数据。存储器解码器164可以纠正达特定数目(写阈值数目)的差错。读阈值数目和写阈值数目可以相同或不同。

在该第一示例场景中,描述了两种链路保护模式(例如,低速和高速链路保护模式)。在一方面,链路保护模式可以通过频率设定点(FSP)寄存器在存储器设备150中实现。随后,对于第一示例场景,可以使用两个FSP寄存器(FSP[0]和FSP[1])。以下将在描述图2和3时提供关于FSP寄存器的细节。

虽然在第一示例场景中仅讨论了两种链路保护模式,但是可以存在任何数目个链路保护模式。为了解说,假设在第二示例场景中,存在三种链路保护模式:分别对应于低速范围(例如,20Mhz≤WCK频率≤1.33Ghz)、中速范围(例如,1.33Ghz 还假设对于该第二示例场景中的低速链路保护模式,读差错检测参数、读差错纠正参数、写差错检测参数和写差错纠正参数全部被禁用。因此,当链路190以低速范围内的速度(例如,1Ghz)操作时,低速链路保护模式变为所应用的链路保护模式,并且主机编码器122、主机解码器124、存储器编码器162和存储器解码器164都不被启用。因此,当应用低速链路保护模式时,可以通过链路190传递未经编码的读数据和写数据。 进一步假设对于高速链路保护模式,读差错检测参数、读差错纠正参数、写差错检测参数和写差错纠正参数全部被启用。因此,当链路190以高速范围内的速度(例如,3Ghz)操作时,高速链路保护模式变为所应用的链路保护模式,并且主机编码器122、主机解码器124、存储器编码器162和存储器解码器164都被启用以进行检测和纠正。因此,当应用高速链路保护模式时,可以通过链路190传递经编码的读数据和写数据。 如上所描述,第二示例场景的低速和高速链路保护模式类似于第一示例场景的低速和高速链路保护模式。但与第一示例场景不同,第二示例场景还包括中速链路保护模式,其中可以假设读差错检测参数被禁用,读差错纠正参数被启用,写差错检测参数被禁用,以及写差错纠正参数被启用。因此,当链路190以中速范围内的速度(例如,2Ghz)操作时,中速链路保护模式变为所应用的链路保护模式。在该模式中,存储器编码器162对读数据进行编码,而主机编码器122对写数据进行编码。补充地,主机解码器124纠正读数据中读阈值数目个的比特差错,而存储器解码器164纠正写数据中写阈值数目个的比特差错。 当应用中速链路保护模式时,相对于低速链路保护模式,读和写等待时间可能增加。功耗也可能更高。但是,相对于高速链路保护模式,由于禁用差错检测,因此可以消耗更少的功率。 注意,可将差错检测与差错纠正分开。也就是说,读差错纠正参数可与读差错检测参数被分开地启用/禁用。同样,写差错纠正参数可与写差错检测参数被分开地启用/禁用。简而言之,可以独立地启用和禁用每个保护参数。结果,主机编码器122、主机解码器124、存储器编码器162和存储器解码器164的许多使能级别的组合是可能的,这允许微调多个链路保护模式。 在第一和第二示例场景两者中,应用低速链路保护模式意味着禁用所有链路差错保护特征,而应用高速链路保护模式意味着启用所有链路差错保护特征。然而,即使在低链路速度下,也可能存在期望某个最小保护的情况。即使在最高链路速度下,也可能存在不期望完全保护的情况。 例如,假设在第三示例场景中,存在三种链路保护模式,并且低速和中速链路保护模式与第二示例场景相同。但是高速链路保护模式与第二示例场景的不同之处在于写差错检测参数被禁用。此链路保护模式可适用于在写操作中检测到多个链路差错的情况。在此情景中,主机110(例如,SoC)可以重试对存储器设备150的相同写操作以恢复原始写数据。遗憾的是,这可能需要显著的实现复杂性并且通过写重试招致大的性能损失。在此情形中,针对写仅启用链路纠错可以是写重试导致的性能损失与较好的链路差错保护能力之间的权衡。 当然,完全可以将第三示例场景的高速链路保护模式纳入在第二示例场景的高速和中速链路保护模式之间。一般而言,主机110和存储器设备150可以被配置为实现多个链路保护模式。链路保护模式可以彼此不同。每个链路保护模式可以对应于链路速度。对应于一个链路保护模式的链路速度可以与对应于其他链路保护模式的链路速度不同。更宽泛地,每个链路保护模式可以对应于链路速度的范围,而对应于一个链路保护模式的链路速度的范围可以与对应于其他链路保护模式的链路速度的范围不交叠。 每个链路保护模式可以包括多个保护参数,其用于定义应用于保护通过链路190传送的读数据和写数据免于差错的特定保护级别。例如,每个链路保护模式可以定义主机编码器122、主机解码器124、存储器编码器162和存储器解码器164的使能级别的特定组合。此外,每个链路保护模式可以与其他链路保护模式中的每一者不同。例如,为一个链路保护模式定义的使能级别的组合可以与为其他链路保护模式定义的组合不同。以此方式,当链路速度改变时(例如,从第一链路速度改变到第二链路速度),链路保护模式也可以动态地改变(例如,从第一链路保护模式(对应于第一链路速度)改变到第二链路保护模式(对应第二链路速度))。 回想在存储器设备150中,可以利用频率设定点(FSP)寄存器来实现链路保护模式。存储器设备150可以包括对应于多个链路保护模式的多个FSP寄存器。FSP寄存器可以例如是寄存器或其他存储元件。对于第一示例场景,存储器设备150可以包括至少两个FSP寄存器FSP[0](例如,用于低速链路保护模式)和FSP[1](例如,用于高速链路保护模式)。对于第二和第三示例场景,存储器设备150可以包括至少三个FSP寄存器FSP[0](例如,用于低速链路保护模式),FSP[1](例如,用于中速链路保护模式)和FSP[2](例如,用于高速链路保护模式)。 在一方面,就每个链路保护模式对应于速度或速度范围这点来说,一种含义是每个FSP寄存器也对应于链路速度或链路速度范围。每个FSP寄存器可以反映对应链路保护模式的读差错检测、读差错纠正、写差错检测和写差错纠正保护参数的组合。例如,每个FSP寄存器可以包括多个保护比特,包括读差错检测比特、读差错纠正比特、写差错检测比特和写差错纠正比特。当被置位/未被置位时,读差错检测比特可以指示读差错检测参数被启用/禁用。当被置位/未被置位时,读差错纠正比特可以指示读差错纠正参数被启用/禁用。当被置位/未被置位时,写差错检测比特可以指示写差错检测参数被启用/禁用。当被置位/未被置位时,写差错纠正比特可以指示写差错纠正参数被启用/禁用。 在一方面,可以通过一个或多个模式寄存器(MR)180-1...180-M来实现多个FSP寄存器。如图1所见,存储器设备150可包括多个模式寄存器180-1...180-M。模式寄存器180-1...180-M可定义存储器设备150的行为。可以存在M个模式寄存器180-1…180-M,其中M可以是大于零的任何整数。每个模式寄存器180-1...180-M可以是写类型、读类型、或读/写类型。存储器控制器120可发出模式寄存器写(MRW)命令以指定特定的写或读/写类型模式寄存器以及模式值,并且存储器链路接口160可将收到的模式值写入所指定的模式寄存器180-1…180-M。存储器控制器120还可发出模式寄存器读(MRR)命令以指定特定的读或读/写类型模式寄存器,并且存储器链路接口160可从所指定的模式寄存器180-1…180-M读取并将所读取的值提供给存储器控制器120。 图2解说了可以用于实现FSP寄存器的模式寄存器(诸如模式寄存器180-1...180-M中的一者)的示例。在该示例中,假设FSP寄存器的模式寄存器包括8个操作数(OP)比特,其中比特OP[3]、OP[2]、OP[1]和OP[0]分别用于实现读差错检测比特、读差错纠正比特、写差错检测比特和写差错纠正比特,以反映保护参数。对于用于实现FSP寄存器的每个模式寄存器,存储器控制器120可发出MRW命令以及对应的模式值。进而,存储器链路接口160可将对应的模式值写入该模式寄存器。以此方式,读差错检测比特、读差错纠正比特、写差错检测比特和写差错纠正比特的不同组合可以被置位/未被置位,以反映不同的链路保护模式。 图3解说了针对不同链路速度的FSP寄存器的设置的示例。在此特定示例中,三个模式寄存器用于实现三个FSP寄存器FSP[0]、FSP[1]和FSP[2]。这些FSP中的设置反映了上述第三示例场景。 图4解说了用于动态地改变存储器子系统100中的链路保护模式的示例方法400的流程图。在图4中,主机110可以执行偶数框410-430,而存储器设备150可以执行奇数框415-435。在框410中,主机110(例如,存储器控制器120)可以(例如,通过链路190)向存储器设备150发出MRW命令连同模式值。在框415中,存储器设备150(例如,存储器链路接口160)可以用从主机110收到的模式值对用于实现FSP寄存器的模式寄存器180进行编程。在框420中,主机110可以向存储器设备150通知要应用的链路保护模式。在一方面,当链路速度从第一链路速度改变到第二链路速度时,主机110可以向存储器设备150指示要应用从第一链路保护模式到第二链路保护模式的链路保护模式的改变。例如,主机110可以向存储器设备150指示对应于第二链路保护模式的当前FSP寄存器。在框425中,存储器设备150可应用当前FSP寄存器。在框430和435中,主机110和存储器设备150可以协调以根据第二链路保护模式执行读和写操作。 图5解说了用于执行读操作的示例方法500的流程图。主机110可以执行偶数框510-580,而存储器设备150可以执行奇数框515-555。在框510中,存储器控制器120可以通过链路190向存储器设备150发出读命令。例如,存储器控制器120可以对来自请求方(例如,DSP、GPU、CPU等)的读请求作出反应。随后,在框520中,存储器控制器120可以通过链路190从存储器设备150接收读数据。 在框510和520之间,存储器链路接口160可以在框515中接收读命令。在框525中,存储器链路接口160可以从多个存储器单元检索读数据。在框535中,存储器设备150可以确定是否应对读数据进行编码。在一方面,在当前FSP寄存器的读差错检测比特和读差错纠正比特中的一者或两者被置位时,可以对读数据进行编码。当启用所应用的链路保护模式的读差错检测参数和读差错纠正参数中的一者或两者时,这可以被视为等同于确定对读数据进行编码。 如果确定不需要对读数据进行编码(例如,如果读差错检测和读差错纠正保护比特两者都未被置位(即,禁用)),则在框555中,存储器链路接口160可以在没有加密的情况下通过链路190发送检索到的读数据。另一方面,如果确定应该对读数据进行编码(例如,如果一个或两个保护比特被置位(即,启用)),则在框545中,存储器编码器162可以对检索到的读数据进行编码,以及随后在框555中,存储器链路接口160可以通过链路190发送经编码的读数据。 回到主机侧,在框530中,主机110可以确定是否应该对通过链路190收到的读数据进行解码。例如,由于当启用所应用的链路保护模式的读差错检测和读差错纠正参数中的一者或两者时,存储器设备150对读数据进行编码,因此主机110可以确定,当启用所应用的链路保护模式的读差错检测和读差错纠正参数中的一者或两者时,也应当对读数据进行解码。当确定收到的读数据是未经编码的时(例如,如果两个参数都被禁用),则在框580中,存储器控制器120可以在不解密的情况下向请求方提供读数据。 然而,如果在框530中确定收到的读数据是经编码的并因此应被解码,则在框540中,主机解码器124可以对收到的读数据进行解码。从框540,如果所应用的链路保护模式的读差错检测参数被启用,则该方法可以进行到框550。在该框中,主机110可以检测收到的读数据中是否存在任何差错。如果没有差错被检测到,则存储器控制器120可以在框580中将经解码的读数据提供给请求方。 然而,如果在框550中检测到任何差错,则可以采取其他选项(例如,从顶部引出的“是(Y)”分支)。一个选项可以是什么也不做,并且请求方可能在某个超时后再次尝试相同的请求。另一种选项可以是向请求方报告差错。又一种选项可以是存储器控制器120将读命令重新发送到存储器设备150。这些仅仅是示例,并不意味着穷举。 替换地从框540,如果所应用的链路保护模式的读差错纠正参数被启用,则该方法500可以进行到框560。在该框中,主机解码器124可以纠正可能存在于读数据中的任何差错。在一方面,应注意,在应用纠正过程之前不需要确定是否存在差错。也就是说,纠正过程可以使得它不会引入任何附加差错。因此,在应用纠正过程之后,无差错的读数据可以保持无差错。 在框570中,主机110可以确定读数据是否已被完全纠正。例如,可能存在对于主机解码器124可以纠正多少比特差错的限制。换言之,主机解码器124可以能够在读数据中纠正达“读阈值”数目个比特差错。如果确定已经纠正读数据(例如,差错的数目小于读阈值数目),则在框580中,存储器控制器120可以将经纠正的读数据提供给请求方。 然而,如果在框570中确定读数据未被完全纠正(例如,差错的数目可能超过读阈值数目),则可以采取其他选项(例如,从左侧引出的“否(N)”分支)。该选项可以类似于参考框550列出的选项。 在框540的另一替换方案中,可以启用读差错检测和读差错纠正保护参数两者。由于启用读差错检测参数,因此该方法可以进行到框550,其中主机110可以检测收到的读数据中是否存在任何差错。如上所描述,当在框550中没有检测到差错时,存储器控制器120可以在框580中将经解码的读数据提供给请求方。然而,在该情形中,如果在框550中检测到差错,则该方法可以进行到框560,其中主机解码器124可以纠正差错(例如,达读阈值数目)。这是因为还启用了读差错纠正保护参数。 图6解说了用于执行写操作的示例方法600的流程图。主机110可以执行偶数框610-640,而存储器设备150可以执行奇数框615-685。在框610中,存储器控制器120可以通过链路190向存储器设备150发出写命令。例如,存储器控制器120可以对来自请求方(例如,DSP、GPU、CPU等)的写请求作出反应。 在框620中,主机110可以在将(例如,也在请求方的写请求中接收的)写数据提供给存储器设备150之前确定是否应该对该写数据进行编码。在一方面,当所应用的链路保护模式的写差错检测和写差错纠正参数中的一者或两者都被启用时,可以确定应对写数据进行编码。 如果确定不需要对写数据进行编码(例如,如果写差错检测和写差错纠正保护比特两者都被禁用(这里应该原文错)),则在框640中,存储器链路接口160可以在没有加密的情况下通过链路190发送写数据。另一方面,如果确定应该对写数据进行编码(例如,如果一个或两个保护参数被启用),则在框630中,主机编码器122可以对写数据进行编码,以及随后在框640中,主机链路接口130可以通过链路190发送经编码的写数据。 在框615和625中,存储器链路接口160可通过链路190分别从主机110接收写命令和写数据。在框635中,存储器设备150可以确定通过链路190收到的写数据是否应该被解码。例如,由于当启用所应用的链路保护模式的写差错检测和写差错纠正参数中的一者或两者时,主机110对写数据进行编码,因此存储器设备150可以确定,当启用所应用的链路保护模式的写差错检测和写差错纠正参数中的一者或两者时,也应当对写数据进行解码。当确定收到的写数据是未经编码的时,存储器链路接口160可以在框685中将写数据存储在多个存储器单元中。 然而,如果在框635中确定收到的写数据是经编码的并因此应被解码,则在框645中,存储器解码器164可以对收到的写数据进行解码。从框645,如果所应用的链路保护模式的写差错检测参数被启用,则该方法可以进行到框655。在该框中,存储器设备150可以确定在收到的写数据中是否存在任何差错。如果没有差错被检测到,则存储器链路接口160可以在框685中将经解码的写数据存储在多个存储器单元中。 然而,如果在框655中检测到任何差错,则可以采取其他选项(例如,从顶部引出的“Y”分支)。一个选项可以是什么也不做,并且主机110可在某个超时后再次尝试。另一种选项可以是向主机110报告差错。这些仅仅是示例,并不意味着穷举。 替换地从框645,如果所应用的链路保护模式的写差错纠正参数被启用,则该方法600可以进行到框665。在该框中,存储器解码器164可以纠正可能存在于写数据中的任何差错。再次,应注意,在应用纠正处理之前不需要确定是否存在差错。 在框675中,存储器设备150可以确定写数据是否已被完全纠正。例如,存储器解码器164可以能够在写数据中纠正达“写阈值”数目个比特差错。如果确定已经纠正写数据(例如,差错的数目小于写阈值数目),则在框685中,存储器链路接口160可以将经纠正的写数据提供给多个存储器单元。 然而,如果在框675中确定写数据未被完全纠正(例如,差错的数目可能超过写阈值数目),则可以采取其他选项(例如,从右侧引出的“N”分支)。该选项可以类似于参考框655列出的选项。 在框645的另一替换方案中,可以假设启用写差错检测和写差错纠正保护参数两者。由于启用写差错检测参数,因此该方法可以进行到框655,其中存储器设备150可以检测在收到的读数据中是否存在任何差错,而当在框655中没有检测到差错时,存储器链路接口160可在框685中存储经解码的写数据。然而,在该情形中,如果在框655中检测到差错,则该方法可以进行到框655,其中由于写差错纠正保护参数也被启用,存储器解码器164可以纠正差错。 图7解说了可集成有前述存储器子系统100的各种电子设备。例如,需要小的形状因子、非常低剖面的移动电话设备702、膝上型计算机设备704、终端设备706、以及可穿戴设备、便携式系统可包括纳入如本文所描述的存储器子系统100的器件/封装700。器件/封装700可以是例如本文所描述的集成电路、管芯、集成器件、集成器件封装、集成电路器件、器件封装、集成电路(IC)封装、层叠封装器件、系统级封装器件中的任一者。图7中所解说的设备702、704、706仅是示例性的。其它电子设备也能以器件/封装700为其特征,此类电子设备包括但不限于包括以下各项的一组设备(例如,电子设备):移动设备、手持式个人通信系统(PCS)单元、便携式数据单元(诸如个人数字助理)、启用全球定位系统(GPS)的设备、导航设备、机顶盒、音乐播放器、视频播放器、娱乐单元、固定位置数据单元(诸如仪表读数装备)、通信设备、智能电话、平板计算机、计算机、可穿戴设备、服务器、路由器、实现在机动车辆(例如,自主车辆)中的电子设备、或者存储或检索数据或计算机指令的任何其它设备,或者其任何组合。 本领域技术人员将领会,信息和信号可使用各种不同技术和技艺中的任何一种来表示。例如,贯穿上面说明始终可能被述及的数据、指令、命令、信息、信号、比特、码元和码片可由电压、电流、电磁波、磁场或磁粒子、光场或光粒子、或其任何组合来表示。 此外,本领域技术人员将领会,结合本文所公开的各示例描述的各种解说性逻辑块、模块、电路和算法可被实现为电子硬件、计算机软件、或两者的组合。为清楚地解说硬件与软件的这一可互换性,各种解说性组件、块、模块、电路、以及方法在上面是以其功能性的形式作一般化描述的。此类功能性是被实现为硬件还是软件取决于具体应用和施加于整体系统的设计约束。技术人员可针对每种特定应用以不同方式来实现所描述的功能性,但此类实现决策不应被解读为致使脱离本公开的范围。 结合本文公开的各示例描述的方法、序列和/或算法可直接在硬件中、在由处理器执行的软件模块中、或在这两者的组合中体现。软件模块可驻留在RAM存储器、闪存、ROM存储器、EPROM存储器、EEPROM存储器、寄存器、硬盘、可移动盘、CD-ROM或者本领域中所知的任何其他形式的存储介质中。示例性存储介质与处理器耦合以使得该处理器能从/向该存储介质读写信息。替换地,存储介质可以被整合到处理器。 因此,一个方面可包括实施上述器件中的任一者的计算机可读介质。因此,所公开的主题内容的范围不限于所解说的示例且任何用于执行本文中所描述的功能性的手段均被包括。 尽管上述公开示出了解说性示例,但是应当注意,在其中可作出各种变更和修改而不会脱离如所附权利要求定义的所公开的主题内容的范围。根据本文中所描述的示例的方法权利要求的功能、过程和/或动作不必按任何特定次序来执行。此外,尽管所公开的主题内容的要素可能是以单数来描述或主张权利的,但是复数也是已料想了的,除非显式地声明了限定于单数。