MEMS器件和电路器件的集成结构及其制造方法

文献发布时间:2023-06-19 11:13:06

技术领域

本发明涉及微机电系统领域,尤其涉及一种MEMS器件和电路器件的集成结构及其制造方法。

背景技术

微机电系统(Micro Electro Mechanical System,简称为MEMS)领域涉及制造微机电器件和纳米机电器件的技术。特别的,该技术可应用于在同一个衬底上制作高性能处理电路和微机电系统器件或者纳米机电系统器件。例如,MEMS速度计、陀螺仪、麦克风、谐振器等都应用了MEMS领域的加工制造技术。MEMS加工制造技术和IC(Integrated Circuit)制造技术类似,都会应用到光刻、注入、刻蚀等高精度加工工艺,同时还需要使用到如体硅刻蚀、掩膜层释放等MEMS专门的加工技术,这些加工技术用于在衬底上,比如典型的单晶硅衬底上形成三维的机械结构,如梁、桥、膜等,这些结构的尺寸一般在微米量级,甚至到纳米量级。

这些微小的机械结构常常需要一个容纳的腔体来提供机械保护,比如使用TO-8管壳通过金属焊接工艺来将微机械结构密封到腔体里面,或者通过将其键合到具有空腔的基板上,该空腔用于容纳机械结构。这些方法都很难低成本的与高性能电路的加工制造工艺兼容,从而实现单片集成的MEMS微系统产品。尤其是MEMS结构需要在真空环境下工作的情况下,这些方式无法提供一种和电路进行单片集成的加工制造方法。

发明内容

有鉴于此,本发明提出一种MEMS器件和电路器件的集成结构及其制造方法,以实现MEMS器件和电路器件的单片集成,提高器件的集成度,降低工艺复杂度。

根据本发明的第一方面,提出一种MEMS器件和电路器件的集成结构的制作方法,其中,包括:提供一衬底,包括下层的支撑层,上层的器件层以及位于所述支撑层和器件层之间的绝缘层;在所述器件层中形成微机械结构,所述微机械结构包括固定部分和可动部分;提供一上基板,将所述上基板通过键合的技术形成在所述器件层上以形成一个密封的腔体,所述腔体用于容纳所述微机械结构的可动部分;以及在所述上基板中形成电路器件。

优选地,还包括在所述上基板中形成连接至所述微机械结构的导电通道,以将所述微机械结构电连接至所述腔体之外。

优选地,形成所述微机械结构的方法包括:在所述衬底上形成第一介质层;形成图案化的光刻胶,以所述图案化的光刻胶为掩膜刻蚀所述第一介质层和所述器件层直至所述绝缘层的顶部,以在所述器件层中形成多个沟槽;以及去除部分所述第一介质层和所述绝缘层以形成所述微机械结构。

优选地,形成所述图案化的光刻胶之前,所述方法还包括在所述第一介质层上形成图案化的掩膜层,所述图案化的掩膜层至少具有形成所述微机械结构的可动部分的第一窗口,所述图案化的光刻胶至少位于被所述第一窗口裸露的所述第一介质层上。

优选地,去除部分所述第一介质层和所述绝缘层方法包括:以所述图案化的掩膜层为保护层,采用腐蚀的方法去除所述第一介质层和所述绝缘层,至少直至所述微机械结构的可动部分上表面的所述第一介质层和其下表面的所述绝缘层被完全去除。

优选地,所述方法还包括去除所述图案化的掩膜层。

优选地,形成所述导电通道的方法包括:在所述上基板中形成裸露所述第一介质层的第一接触孔;在所述第一接触孔的内表面和所述上基板的上表面形成第二介质层;去除所述第一接触孔底部的第一介质层;以及在侧壁覆盖有所述第二介质层的所述第一接触孔中和所述上基板的部分上表面沉积第一导电材料以形成所述导电通道。

优选地,形成所述电路器件的方法包括:在所述上基板中形成第一掺杂类型的阱区;在所述第二介质层上形成栅极导体;以及自对准离子注入工艺在所述阱区中形成第二掺杂类型的漏区和第二掺杂类型的源区。

优选地,在形成所述第二介质层之前,先形成所述阱区。

优选地,所述第二介质层作为所述电路器件的栅介质层。

优选地,所述第一导电材料和所述栅极导体同步工艺形成。

优选地,形成所述第一导电材料和形成所述栅极导体的方法包括:在所述第一接触孔中和所述上基板的上表面沉积导电层;选择性的刻蚀部分位于所述上基板的上表面的导电层,以形成所述第一导电材料和位于所述阱区上方的栅极导体。

优选地,所述方法还包括:在所述导电通道,所述第二介质层以及所述栅极导体上形成第三介质层;在所述第三介质层中形成分别部分裸露所述导电通道,所述栅极导体,所述漏区和源区的第二接触孔;在所述第二接触孔中沉积第二导电材料。

优选地,所述上基板为硅基板,所述第一介质层为氧化硅。

优选地,所述上基板通过硅硅熔融键合的技术键合至所述第一介质层上表面。

优选地,在形成所述导电通道之前,还包括采用化学机械抛光的工艺减薄所述上基板。

优选地,所述上基板被减薄至10-15um。

优选地,所述图案化的掩膜层为氮化硅层。

优选地,采用深硅刻蚀工艺刻蚀所述器件层。

优选地,采用气体状态的氢氟酸或缓冲氧化物腐蚀剂腐蚀所述第一介质层和所述绝缘层。

优选地,所述第一导电材料为高掺杂的多晶硅或导电金属。

优选地,所述器件层的厚度范围为5-15um。

优选地,所述衬底为SOI衬底。

根据本发明的第二方面,提出一种MEMS器件和电路器件的集成结构,其中,包括:衬底,包括下层的支撑层,上层的器件层以及位于所述支撑层和器件层之间的绝缘层,在所述器件层中包括微机械结构,所述微机械结构包括固定部分和可动部分;第一介质层,至少位于所述微机械结构的固定部分的上表面;上基板,通过键合的技术键合在所述第一介质层上;以及电路器件,位于所述上基板中,其中,所述上基板与所述衬底形成一个密封的腔体,用于容纳所述微机械结构的可动部分。

优选地,还包括导电通道,位于所述上基板中,用以将所述微机械结构电连接至所述腔体之外。

优选地,所述微机械结构的可动部分包括至少两个分离的悬空结构,所述微机械结构的可动部分的上表面与上基板之间不包括第一介质层,所述微机械结构的可动部分的下表面与支撑层之间不包括绝缘层。

优选地,所述微机械结构的固定部分与所述微机械结构可动部分的至少一个悬空结构连接。

优选地,所述微机械结构的可动部分位于所述微机械结构的固定部分之间。

优选地,所述导电通道包括位于所述上基板中的第一接触孔和填充所述第一接触孔以及位于所述上基板的至少上表面上的第一导电材料。

优选地,还包括位于所述第一接触孔的侧壁以及所述上基板的上表面的第二介质层。

优选地,所述电路器件包括;位于所述上基板中的第一掺杂类型的阱区;位于所述第二介质层上的栅极导体;以及位于所述阱区中的第二掺杂类型的源区和第二掺杂类型的漏区。

优选地,还包括位于所述导电通道,所述第二介质层以及所述栅极导体上的第三介质层。

优选地,所述第一介质层为氧化硅。

优选地,所述上基板为硅基板。

优选地,所述第一导电材料为高掺杂的多晶硅或导电金属。

优选地,所述上基板的厚度范围为10-15um。

优选地,所述器件层的厚度范围为5-15um。

优选地,所述衬底为SOI衬底。

根据本发明提供的MEMS器件和电路器件的集成结构的制造方法,先提供一种包括器件层,绝缘层,支撑层的衬底,刻蚀所述器件层形成微机械结构;然后通过键合的方式将上基板键合至所述衬底上形成一个密封的腔体,用于容纳所述微机械结构的可动部分;最后在所述上基板中形成电路器件以及形成将所述微机械结构电连接至腔体外的导电通道。本发明通过键合的方式形成的腔体具有低张应力,还可调节腔体内的环境压力,且腔体的密封性能在后续的工艺中不会发生退化,不会影响腔体内的微机械结构的性能。另外,本发明将MEMS器件和电路器件进行单片集成,实现了在同一衬底上制造出高性能的电路器件和MEMS器件,提高了集成度,降低了工艺复杂度以及制造成本。

附图说明

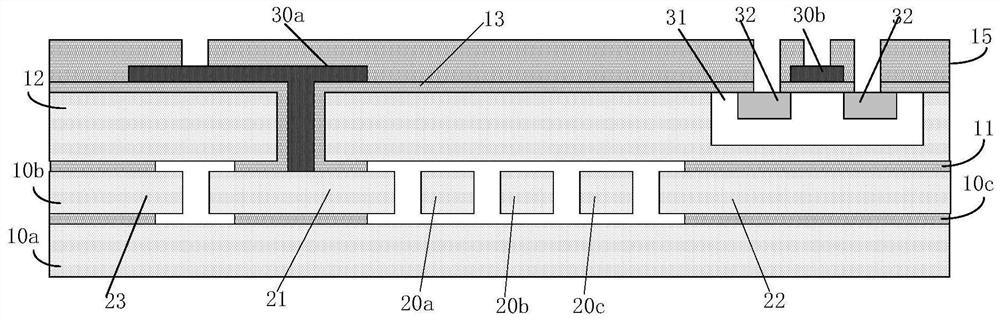

图1为根据本发明的实施例的MEMS器件和电路器件的集成结构的截面图;

图2A-2J为根据本发明的实施例的制造MEMS器件和电路器件的集成结构的方法的部分阶段截面图。

具体实施方式

以下将参照附图更详细地描述本发明。在各个附图中,相同的组成部分采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。为了简明起见,可以在一幅图中描述经过数个步骤后获得的结构。在下文中描述了本发明的许多特定的细节,例如每个组成部分的结构、材料、尺寸、处理工艺和技术,以便更清楚地理解本发明。但正如本领域的技术人员能够理解的那样,可以不按照这些特定的细节来实现本发明。

图1为根据本发明的实施例的MEMS器件和电路器件的集成结构的截面图。

所述集成结构包括衬底,微机械结构,第一介质层11,上基板12,电路器件以及导电通道30a。其中,所述衬底包括下层的支撑层10a,上层的器件层10b以及位于所述支撑层10a和器件层10b之间的绝缘层10c,在所述器件层10b中包括所述微机械结构,所述微机械结构包括固定部分21,22和可动部分。所述第一介质层11至少位于所述微机械结构的固定部分的上表面,在本实施例中,所述第一介质层11还位于所述器件层10b的其他部分23上。所述上基板12通过键合的技术键合在所述第一介质层11上,所述上基板12与所述衬底形成一个密封的腔体,用于容纳所述微机械结构的可动部分。所述导电通道30a位于所述上基板中,用以将所述微机械结构电连接至所述腔体之外。所述电路器件位于所述上基板12中。在本实施例中,所述衬底为SOI(silicon-on-insulator)衬底,所述支撑层10a和器件层10b为半导体硅材料,绝缘层10c为二氧化硅。所述第一介质层11为氧化硅,所述上基板12为硅基板,所述上基板12和所述第一介质层11通过硅硅键合的方式键合。其中,所述上基板12的厚度范围为10-15um。所述器件层10b的厚度范围为5-15um,所述器件层10b的掺杂电阻率的范围为1ohm.cm~0.01ohm.cm。

所述微机械结构的可动部分包括至少两个分离的悬空结构,所述微机械结构的可动部分的上表面与上基板之间不包括第一介质层,所述微机械结构的可动部分的下表面与支撑层之间不包括绝缘层。在本实施例中,所述微机械结构的可动部分包括三个分离的悬空结构,分别是20a,20b,20c。所述微机械结构的固定部分的也部分悬空,具体地,所述微机械结构的固定部分的边缘部分悬空。

所述微机械结构的固定部分21,22与所述微机械结构可动部分的至少一个悬空结构连接。在本实施例中,所述微机械结构的固定部分21与所述可动部分20a和20c连接,所述微机械结构的固定部分22与所述可动部分20b连接。所述微机械结构的可动部分20a,20b,20c位于所述微机械结构的固定部分21和22之间。所述微机械结构的固定部分21与所述器件层10b的其他部分23之间隔开。需要注意的是,所述微机械结构的固定部分与可动部分的连接并不限于本发明公开的方式,本领域的技术人员可以根据实际的工艺和器件要求连接,在此不做任何限制。

所述导电通道30a包括位于所述上基板12中的第一接触孔和填充所述第一接触孔以及位于所述上基板的部分上表面上的第一导电材料。在本实施例中,所述导电通道30a延伸至所述微机械结构的固定部分的上表面,以将所述微机械结构电连接至腔体外。所述第一接触孔的侧壁以及所述上基板的上表面还包括第二介质层13,所述第一接触孔中所述第二介质层用于将所述导电通道和上基板12中的其他器件结构或导电结构隔离。所述第一导电材料为高掺杂的多晶硅或导电金属。

其中,所述电路器件包括位于所述上基板中的第一掺杂类型的阱区31;位于所述第二介质层13上的栅极导体30b;以及位于所述阱区31中的第二掺杂类型的源区32和第二掺杂类型的漏区32。所述集成结构还包括位于所述导电通道30a,所述第二介质层13以及所述栅极导体30b上的第三介质层15;位于所述第三介质层15中,并分别部分裸露所述导电通道30a,所述栅极导体30b,所述源漏区32的第二接触孔;以及位于所述第二接触孔中的第二导电材料(图中未示出)。

其中,第一掺杂类型为N型或P型中的一种,所述第二掺杂类型为N型或P型中的另一种。

图2A-2H为根据本发明的实施例的制造MEMS器件和电路器件的集成结构的方法的部分阶段截面图。

如图2A所示,提供一衬底,在本实施例中,所述衬底片为SOI衬底。所述SOI衬底包括下层支撑层10a、上层器件层10b以及位于所述支撑层10a和器件层10b之间的绝缘层10c。其中,支撑层10a和器件层10b为半导体硅材料,绝缘层10c为二氧化硅,器件层10b的掺杂电阻率优选为1ohm.cm~0.01ohm.cm,器件层10b的厚度优选为5-15um。

如图2B所示,先在所述SOI衬底上生长一层第一介质层11,再在所述第一介质层11上形成一层掩膜层。其中,所述第一介质层的厚度优选为1um,所述掩膜层12的厚度优选为0.25um。随后,图形化所述掩膜层,采用常规的光刻、刻蚀工艺获得图案化的掩膜层12,所述图案化的掩膜层12至少具有形成后续的微机械结构的可动部分的窗口1201。在本实施例中,所述掩膜层12还包括窗口1202,用以后续形成将微机械结构的固定部分和器件层的其他部分隔开的沟槽。本步骤的刻蚀工艺优选为湿法腐蚀刻蚀工艺。所述第一介质层11选为氧化层,优选地,为氧化硅。

如图2C所示,至少在所述窗口1201中形成图案化的光刻胶(在图中未显示),以所述图案化的光刻胶作为掩膜层,刻蚀所述第一介质层11和所述器件层10b直至所述绝缘层10c的上表面,以在所述器件层10b中形成多个沟槽。本步骤中的刻蚀器件层10b的刻蚀工艺为深硅刻蚀工艺,是一种干法刻蚀工艺,可以形成近乎垂直的侧壁。本步骤刻蚀所述第一介质层11的工艺为湿法腐蚀工艺。

如图2D所示,以所述图案化的掩膜层12作为保护层,腐蚀所述第一介质层11和所述绝缘层10c以形成微机械结构,所述微机械结构包括可动部分20a,20b和20c以及固定部分21和22。其中,腐蚀所述第一介质层11和所述绝缘层10c至少直至所述微机械结构的可动部分上表面的第一介质层11和其下表面的绝缘层10c被完全去除掉。在本实施例中,采用缓冲氧化物腐蚀剂(BOE)或VHF(vapour HF acid)进行腐蚀,其中,VHF这种气体状态的氢氟酸,腐蚀之后不会造成结构粘到支撑层上。最后去除所述图案化的掩膜层12。

如图2E所示,提供一上基板12,将所述上基板12键合至所述第一介质层11上,与所述衬底形成一个密闭的腔体,以容纳所述微机械结构的可动部分。在本实施例中,所述上基板12优选为硅材料,所述上基板12可通过硅硅熔融键合技术键合至所述第一介质层11上,所述键合温度约为1100-1300℃,优选地,为1200℃。因为是硅硅键合,其材料的热失配比小,使得键合界面的应力比较小,且键合的非常牢固。另外,通过调节键合工艺的环境,可以相应调节所述腔体中的环境气体种类和压力,以使该腔体里面包含一定压强的流体以提供器件工作需要的阻尼。工作过程中,该微机械结构的一部分或者某几部分可以在腔体内进行相关的运动。

如图2F所示,将上基板12减薄到所需要的厚度,以进行后续的加工制造。所述需要的厚度优选为10-15um。这步减薄一般是通过CMP(Chemical Mechanical Polishing,化学机械抛光)工艺来实现,这种技术可以在减薄之后得到非常平整光滑的表面,从而可以在这个表面上进行电路器件的加工制造。

如图2G所示,在所述上基板12中形成阱区31,所述阱区31采用离子注入的工艺形成,然后通过高温扩散使杂质扩散至所述上基板内部。所述阱区31为第一掺杂类型的阱区。然后采用刻蚀工艺在所述上基板12中形成第一接触孔14,所述第一接触孔14裸露所述第一介质层11的上表面。由于第一介质层11的刻蚀速率很低,因此该步刻蚀工艺可以实现自停止。本步骤的刻蚀工艺可采用干法刻蚀工艺。在本实施例中,所述第一接触孔是在形成所述阱区31的步骤之后形成。当然,在其他实施例中,所述第一接触孔也可在形成所述阱区31的步骤之前形成,在此并不做限制。

如图2H所示,在所述第一接触孔14的内表面和所述上基板12的上表面形成一层第二介质层13。所述第二介质层13也覆盖所述阱区31的上表面。在本实施例中,采用热氧化生长或者淀积的工艺形成所述第二介质层13。

如图2I所示,去除所述第一接触孔底部的第一介质层11,并在所述第一接触孔中和在所述上基板12上的第二介质层13上表面沉积第一导电材料。并对所述上基板上的第二介质层上表面的第一导电材料进行刻蚀以形成导电通道30a和栅极导体30b。其中,所述导电通道用以将所述微机械结构电连接至腔体之外,所述栅极导体位于所述阱区31的上方,所述栅极导体下方的所述第二介质层13为所述电路器件的栅介质层,所述第一接触孔中的第二介质层还用于将所述导电通道和上基板12中的其他器件结构或导电结构隔离。在本实施例中,所述第一导电材料可以选择为高掺杂的多晶硅或者导电金属材料。

如图2J所示,在所述阱区31中形成第二掺杂类型的源漏区32,所述源漏区32通过自对准离子注入工艺形成。在本实施例中,所述第一掺杂类型为N型或P型中的一种,所述第二掺杂类型为N型或P型中的另一种。

如图1所示,还包括在所述导电通道30a,所述栅极导体30b以及所述第二介质层13上形成第三介质层15,并在所述第三介质层15中形成分别部分裸露所述导电通道30a,所述栅极导体30b,所述源漏区32的第二接触孔;最后在所述第二接触孔中沉积第二导电材料(图中未示出),以将所述微结构和所述电路器件的电极引出。

根据本发明提供的制造MEMS器件的方法,先提供一种包括器件层,绝缘层,支撑层的衬底,刻蚀所述器件层形成微机械结构;然后通过键合的方式将上基板键合至所述衬底上形成一个密封的腔体,用于容纳所述微机械结构的可动部分;最后在所述上基板中形成电路器件以及形成将所述微机械结构电连接至腔体外的导电通道。本发明通过键合的方式形成的腔体具有低张应力,还可调节腔体内的环境压力,且腔体的密封性能在后续的工艺中不会发生退化,不会影响腔体内的微机械结构的性能。另外,本发明将MEMS器件和电路器件进行单片集成,实现了在同一衬底上制造出高性能的电路器件和MEMS器件,提高了集成度,降低了工艺复杂度以及制造成本。

依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

- MEMS器件和电路器件的集成结构及其制造方法

- MEMS器件中的拱形结构及其制造方法、MEMS器件