发光二极管装置

文献发布时间:2023-06-19 11:17:41

技术领域

本揭露是有关于一种具有发光二极管的装置。

背景技术

此段落仅用以提供与本揭露相关的背景资料,而非用以限定本揭露的先前技术。

传统显示器的制程多延续标准化的制程。近年来,已有越来越多新式的显示器,像是微发光二极管显示器、次毫米发光二极管显示器以及量子点发光二极管显示器等,皆有希望占据未来的显示器市场。因此,标准化的显示器制程仍有待设立。显示器的制程中往往包含诸多步骤,而若能省略其中任一步骤则有望降低成本并提升效率。

发明内容

根据本揭露一些实施例,发光二极管装置包括基板、第一导电垫及第二导电垫、发光二极管、金属突出物、高分子层以及上部电极。基板包含上表面。第一导电垫及第二导电垫位于基板上。发光二极管位于第一导电垫上。金属突出物位于第二导电垫上。高分子层覆盖基板的上表面、第一导电垫、第二导电垫、金属突出物以及发光二极管,其中自金属突出物的顶部至基板的上表面的距离大于高分子层的厚度。上部电极覆盖发光二极管、高分子层以及金属突出物,使得发光二极管电性连接第二导电垫。

在本揭露一实施例中,发光二极管包含下部电极、位于下部电极上的第一型半导体层、位于第一型半导体层上的主动层以及位于主动层上的第二型半导体层,自金属突出物的顶部至基板的上表面的距离大于自第二型半导体层与主动层之间的界面至基板的上表面的距离。

在本揭露一实施例中,高分子层的厚度大于自第二型半导体层与主动层之间的界面至基板的上表面的距离。

在本揭露一实施例中,下部电极的厚度与第一导电垫的厚度的总和小于或等于2微米。

在本揭露一实施例中,第二型半导体层的厚度与第一型半导体层的厚度之间的比例大于或等于1.5。

在本揭露一实施例中,第一型半导体层为P型半导体层,且第二型半导体层为N型半导体层。

在本揭露一实施例中,上部电极接触发光二极管的上表面以及金属突出物。

在本揭露一实施例中,高分子层为正光阻层。

在本揭露一实施例中,上部电极为透明的。

在本揭露一实施例中,上部电极为银纳米线。

在本揭露一实施例中,高分子层包含二氧化钛(TiO

在本揭露一实施例中,高分子层的厚度大于或等于2微米。

在本揭露一实施例中,发光二极管的横向长度小于或等于50微米。

在本揭露一实施例中,金属突出物的横向长度小于或等于50微米。

借由上述技术方案,本发明至少具有以下优点效果:本发明发光二极管装置可降低制造成本并提升制造效率。

附图说明

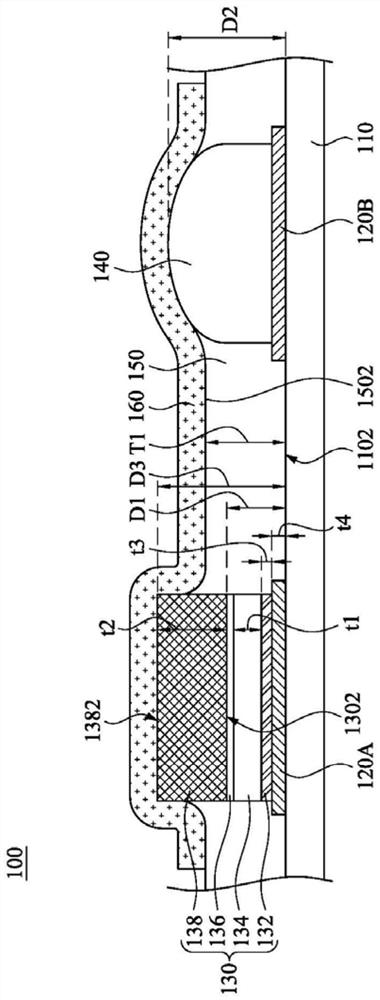

图1A为根据本揭露一些实施例的具有发光二极管的装置的剖面图。

图1B为图1A的装置在制造过程中的剖面图。

图2A为根据本揭露一些实施例的具有发光二极管的装置的剖面图。

图2B为图2A的装置在制造过程中的剖面图。

【主要元件符号说明】

100,200:装置 110:基板

1102:上表面 120A:第一导电垫

120B:第二导电垫 130:发光二极管

1302:界面 132:下部电极

134:第一型半导体层 136:主动层

138:第二型半导体层 1382:上表面

140,240:金属突出物 150,150’,250,250’:高分子层

1502:上表面 152:第一部份

154:第二部份 156:第三部份

160,260:上部电极 D1,D2,D3,D4:距离

T1,T2,T3,T4,t1,t2,t3,t4:厚度

具体实施方式

以下将结合附图形式公开本发明的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些公知惯用的结构与元件在图式中将以简单示意的方式绘示之。

在本文中对“一个实施例”、“实施例”、“一些实施例”等的引用指示所描述的实施例可以包括特定的特征、结构或特性,但是每个实施例可能不一定包括该特定的特征、结构或特性。而且,这样的短语不一定指相同的实施例。此外,当结合实施例描述特定特征、结构或特性时,无论是否明确描述,结合其他实施例来实现这样的特征、结构或特性都会在相关领域的技术人员的知识范围内。

在此使用的“上方”、“至”、“之间”以及“上”等用词,指的是一层相对于其它层的相对位置。一层位于另一层“上方”或“上”或接合“至”另一层的描述,可能是直接接触另一层或隔着一个或多个中间层。一层位于多层“之间”的描述,可能是直接接触所述多层或隔着一个或多个中间层。

图1A为根据本揭露一些实施例的具有发光二极管130的装置100的剖面图。装置100包括基板110、第一导电垫120A及第二导电垫120B、发光二极管130、金属突出物140、高分子层150以及上部电极160。基板110包含上表面1102。第一导电垫120A及第二导电垫120B位于基板110的上表面1102上。发光二极管130接合在第一导电垫120A上。金属突出物140位于第二导电垫120B上。

发光二极管130包含下部电极132、第一型半导体层134、主动层136以及第二型半导体层138。第一型半导体层134位于下部电极132上。主动层136位于第一型半导体层134上。第二型半导体层138位于主动层136上。当发光二极管130接合至第一导电垫120A上之后,下部电极132接触第一导电垫120A。在本实施例中,发光二极管130为直立式发光二极管。

高分子层150覆盖基板110的上表面1102、第一导电垫120A、第二导电垫120B、金属突出物140以及发光二极管130。高分子层150具有厚度T1,且厚度T1等于自高分子层150的上表面1502至基板110的上表面1102的距离。

上部电极160覆盖发光二极管130、高分子层150以及金属突出物140,使得发光二极管130电性连接第二导电垫120B。具体来说,上部电极160接触第二型半导体层138的上表面1382以及金属突出物140。在一些实施例中,上部电极160为透明的,使得来自发光二极管130的光线可穿透上部电极160以增强光取出效率(light extraction efficiency)。在一些实施例中,上部电极160可为氧化铟锡(ITO)或包含金属纳米线。

自金属突出物140的顶部至基板110的上表面1102的距离D2(也就是金属突出物140的最大纵向高度)大于高分子层150的厚度T1。除此之外,自第二型半导体层138的上表面1382至基板110的上表面1102的距离D3大于厚度T1。换句话说,第二型半导体层138的上表面1382与金属突出物140的顶部并非完全地被高分子层150覆盖,且第二型半导体层138的上表面1382与金属突出物140的顶部皆与上部电极160接触。由于距离D2及距离D3大于厚度T1,因此无需形成开口在高分子层150中以曝露第二型半导体层138与第二导电垫120B。除此之外,上部电极160可直接地形成在第二型半导体层138的上表面1382、金属突出物140的顶部以及高分子层150的上表面1502。因此,无需将上部电极160形成在电性连接效率受到深宽比影响的开口中。根据上述可知,制造成本可被降低且制造效率可被提升。

高分子层150的厚度T1大于第二型半导体层138与主动层136之间的界面1302至基板110的上表面1102的距离D1。因此,主动层136与第一型半导体层134被高分子层150覆盖,以维持第一型半导体层134与第二型半导体层138之间的电性绝缘。

图1B为图1A的装置100在制造过程中的剖面图。图1B的装置100是在上部电极160形成之前且高分子层150’被蚀刻前的状态。参阅图1A及图1B。在本实施例中,金属突出物140的距离D2小于距离D3的约0.8倍,且距离D2大于自第二型半导体层138与主动层136之间的界面1302至基板110的上表面1102的距离D1。在高分子层150’被蚀刻之前,第二型半导体层138的上表面1382与金属突出物140的顶部皆被高分子层150’覆盖。高分子层150’包含位于发光二极管130上方的第一部份152、与发光二极管130及第二导电垫120B无重叠的第二部份154以及位于金属突出物140上的第三部份156。第一部份152具有厚度T3,第二部份154具有厚度T4,且厚度T4为自金属突出物140的顶部至高分子层150’的上表面的最小纵向距离。在本实施例中,厚度T4可大于厚度T3。

在一些实施例中,蚀刻可通过灰化及等离子蚀刻执行,但本揭露并不以此为限。高分子层150’的最上表面的蚀刻速率大致相等。换句话说,第一部份152、第二部份154以及第三部份156自高分子层150’的最上表面等量地被蚀刻。在一些其他实施例中,高分子层150’可为正光阻层,且蚀刻可接续地通过部分曝光及显影制程执行。举例来说,高分子层150’可借由紫外光弱曝,但本揭露并不以此为限。具体来说,第一部份152的光敏感材料全部被降解,而第二部份154及第三部份156中远离基板110的部份被降解。

因此,在高分子层150’被蚀刻后,高分子层150’的厚度T2缩减至图1A中所示的厚度T1,且厚度T1最大等同于厚度T2与厚度T4的差值。也就是说,在高分子层150’被蚀刻后,第二型半导体层138的上表面1382及金属突出物140的顶部自高分子层150曝露。由此可知,借由上述的厚度及距离的设计,第二型半导体层138的上表面1382及金属突出物140的顶部可在单一步骤中被曝露,且形成光罩以图案化高分子层150的步骤可被省略。因此,制造成本可被降低,且制造效率可被提升。

在一些实施例中,高分子层150’可借由旋转涂布或狭缝涂布而形成,借此在单一的涂布步骤中形成高分子层150’的型态并满足关系式:T2-T4>D1。在一些实施例中,高分子层150包含二氧化钛(TiO

在一些其他实施例中,厚度T3可大于厚度T4。在此状况下,举例来说,距离D2可大于距离D3的0.8倍但小于距离D3的1.2倍。在高分子层150’被蚀刻前,第二型半导体层138的上表面1382及金属突出物140的顶部皆被高分子层150’覆盖。在高分子层150’被蚀刻后,高分子层150’的厚度T2缩减至图1A中所示的厚度T1,且厚度T1最大等同于厚度T2与厚度T3的差值。

在曝光过程中,曝光光线可部分地被金属突出物140反射。如此一来,对于高分子层150’的第三部份156的材料的曝光效率被降低,使得第三部份156中被降解的材料的深度可小于第一部份152及第二部份154中被降解的材料的深度。因此,金属突出物140具有较大的距离D2,可避免曝光效率被金属突出物140的反射特性所影响。

在一些实施例中,第一型半导体层134为P型半导体层,且第二型半导体层138为N型半导体层。在此状况下,N型半导体层为较厚的层,且相较于P型半导体层具有较低的电阻率。由于在发光二极管130接合至第一导电垫120A之前,电阻率及接触电阻较高的P型半导体层完全接触下部电极132,因此本实施例可具有较佳的发光效率。在一些实施例中,P型半导体层的厚度(也就是第一型半导体层134的厚度t1)约为250纳米且主动层136的厚度约为150纳米。在一些实施例中,发光二极管130进一步包含位于主动层136及第一型半导体层134之间的电子阻障层(图未示),用以避免电子(自N型半导体层流向主动层136)自主动层136流出,因此可提升发光效率。

在一些实施例中,第二型半导体层138的厚度t2与第一型半导体层134的厚度t1之间的比例约大于或等于1.5。当第二型半导体层138比第一型半导体层134厚时,高分子层150的厚度T1大于距离D1的机率较大。因此,第二型半导体层138及第一型半导体层134之间的厚度关系可增加如前所述的T1>D1的规范的容忍度。在一些实施例中,由于距离D1可能的最大值是等于或小于约2微米,且高分子层150的厚度T1是约大于或等于2微米,因此可较佳地维持第一型半导体层134与第二型半导体层138之间的电性绝缘。

除此之外,在一些实施例中,当发光二极管130大量地被转移到基板110上时,若发光二极管130因缺陷而未设置在第一导电垫120A上,借由前述形成高分子层150的方法可使一部份位于第一导电垫120A上的高分子层150较厚。举例来说,一部份位于第一导电垫120A上的高分子层150可能与第三部份156等厚,且第一导电垫120A仍可在显影制程后被剩余的高分子层150覆盖。因此,上部电极160与第一导电垫120A之间的电性绝缘可被维持,以避免传统制程中可能发生的短路现象。

图2A为根据本揭露一些实施例的具有发光二极管的装置200的剖面图。图2B为图2A的装置200在制造过程中的剖面图。图2B的装置200是在上部电极260形成之前且高分子层250’被蚀刻前的状态。参阅图2A及图2B。图2A的装置200与图1A中的装置100相似,其差异在于自金属突出物240的顶部至基板110的上表面1102的距离D4大于自发光二极管130的第二型半导体层138的上表面1382至基板110的上表面1102的距离D3。图2B的结构与图1B的结构相似,其差异在于当高分子层250’被蚀刻前,金属突出物240的顶部并未完全的被高分子层250’覆盖。换句话说,当高分子层250’被蚀刻前,金属突出物240已经自高分子层250’曝露。由此可知,借由上述的厚度及距离的设计,第二型半导体层138的上表面1382及金属突出物240的顶部可在单一步骤中被曝露,且形成光罩以图案化高分子层250’的步骤可被省略。因此,制造成本可被降低,且制造效率可被提升。除此之外,由于在高分子层250’被蚀刻前,金属突出物240的顶部并未完全的被高分子层250’覆盖,电性连接品质不会被金属突出物240反射的曝光光线影响。

在一些实施例中,发光二极管130为具有横向长度约小于50微米的微发光二极管。应理解到,优选条件是底部电极132的厚度t3与第一导电垫120A的厚度t4的总和约小于或等于2微米。2微米(也就是横向长度≤约50微米)可使得发光二极管的尺寸以及当微发光二极管接合至第一导电垫120A后的下部电极132与第一导电垫120A之间的格隙扩散能力达到平衡。如此一来,在接合过程中可无需执行熔融制程,可较佳地避免微发光二极管在接合过程中被破坏,且微发光二极管相对于第一导电垫120A的位置可较好的被控制。

由于微发光二极管的尺寸微小,在传统制程中要将微发光二极管与用以曝露微发光二极管的第二型半导体层的开口对准将变得更具挑战性。因此,借由在单一步骤中曝露微发光二极管的第二型半导体层以及第二导电垫可取代形成开口以曝露的第二型半导体层的上表面的步骤,借此避免因为上述开口与微发光二极管之间错位而导致的短路。除此之外,在传统制程中,形成上部电极160在具有小尺寸的开口(例如接触开口)中更加困难。因此,本揭露的方法可省略形成上部电极160在用以曝露第二型半导体层以及第二导电垫的开口中的步骤,借此提升电性连接品质。根据上述可知,形成具有微发光二极管的显示装置的设计规范可较容易被达成,且间距可被缩减,借此避免错位问题并提升电性连接品质。

综上所述,本揭露的具有发光二极管的装置提供了金属突出物,自此金属突出物的顶部至基板的上表面之间的距离大于蚀刻后的高分子层的厚度,使得此装置可借由在单一步骤中从位于上方的高分子层中曝露发光二极管的第二型半导体层的上表面以及金属突出物的顶部而形成。因此,传统制程中形成光罩以图案化用以曝露第二导电垫的开口的步骤可被省略,制造成本可被降低,且制造效率可被提升。

虽然本揭露已以实施方式揭露如上,然其并非用以限定本揭露,任何熟习此技艺者,在不脱离本揭露的精神和范围内,当可作各种的更动与润饰,因此本揭露的保护范围当视申请专利范围所界定者为准。

- 触控微发光二极管显示装置、操作触控微发光二极管显示装置的方法,以及制造触控微发光二极管显示装置的方法

- 高功率发光二极管的发光二极管装置及制造发光二极管装置的方法