具有环绕式外基极的晶体管

文献发布时间:2023-06-19 19:27:02

技术领域

本公开涉及半导体结构,更具体地说,涉及具有环绕式外基极的晶体管和制造方法。

背景技术

异质结双极型晶体管(HBT)是一种双极结型晶体管(BJT),其使用不同的半导体材料作为发射极和基极区或集电极和基极区,从而形成异质结。HBT用在功率放大器和蜂窝应用等中,并要求低集电极-基极电容(Ccb)、低基极电阻(Rb)、高截止频率(fT/fMAX)和高击穿电压(BVceo)。然而,当前的用于制造HBT的集成方案可能导致高Ccb(寄生电容)和高Rb,这是双极技术中的一个问题,因为它限制了用于改善的fT/fMAX的器件缩放。

发明内容

在本公开的一方面,一种结构包括:衬底;集电极区,其位于所述衬底内;发射极区,其位于所述衬底上方并且包括基于单晶硅的材料;内基极,其位于所述发射极区下方并且包括半导体材料;以及外基极,其围绕所述发射极并且位于所述内基极上方。

在本公开的一方面,一种结构包括:集电极区,其位于衬底内;升高的内基极,其位于所述衬底上方;发射极,其位于所述升高的内基极上方并包括单晶半导体材料;绝缘体材料,其位于所述发射极的侧壁上;外基极,其围绕所述发射极和所述升高的内基极并包括单晶半导体材料,所述外基极通过所述绝缘体材料与所述发射极分隔;以及硅化物,其位于所述外基极上方。

在本公开的一方面,一种方法包括:形成位于衬底内的集电极区;形成位于所述衬底上方并包括基于单晶硅的材料的发射极区;形成位于所述发射极区下方并包括半导体材料的内基极;以及形成围绕所述发射极并位于所述内基极上方的外基极。

附图说明

在下面的详细描述中,通过本公开的示例性实施例的非限制性示例,参考所提到的多个附图来描述本公开。

图1示出了根据本公开的一些方面的除其他特征之外的具有集电极区的衬底以及相应的制造工艺。

图2示出了根据本公开的一些方面的除其他特征之外的位于衬底上的帽层和硬掩模以及相应的制造工艺。

图3示出了根据本公开的一些方面的除其他特征之外的位于硬掩模上的半导体材料以及相应的制造工艺。

图4示出了根据本公开的一些方面的除其他特征之外的发射极区以及相应的制造工艺。

图5示出了根据本公开的一些方面的除其他特征之外的围绕发射极区的间隔物以及相应的制造工艺。

图6示出了根据本公开的一些方面的除其他特征之外的围绕发射极区的外基极以及相应的制造工艺。

图7示出了根据本公开的一些方面的除其他特征之外的位于外基极和发射极区上的硅化物和到硅化物的接触以及相应的制造工艺。

具体实施方式

本公开涉及半导体结构,更具体地说,涉及具有环绕式外(extrinsic)基极的晶体管和制造方法。更具体地说,晶体管是异质结双极型晶体管,其具有环绕式外基极和位于外基极上的硅化物。有利地,环绕式外基极环绕内(intrinsic)基极并允许用于硅化物和欧姆接触形成的更高表面积,从而导致与常规的集成方案相比较低的R

在实施例中,晶体管是异质结双极型晶体管,其具有位于内基极上方的环绕式外基极。环绕式外基极(和硅化物)可以被设置在内基极上方并围绕发射极区。在实施例中,环绕式外基极包括外延生长的Si材料,以及发射极包括例如Si的单晶半导体材料。外基极也可以是其他半导体材料,例如SiGe。外基极的硅化物也可以环绕外基极。内基极可以是包括SiGe材料的升高的(raised)内基极。

本公开的晶体管可以使用多种不同的工具,以多种方式来制造。然而,通常,使用方法和工具形成具有微米和纳米级尺寸的结构。已经根据集成电路(IC)技术采用了用于制造本公开的晶体管的方法(即,技术)。例如,这些结构建立在晶片上,并在晶片顶部上借助光刻工艺图案化的材料膜中实现。特别地,晶体管的制造使用三个基本构造块:(i)在衬底上沉积材料薄膜;(ii)通过光刻成像在膜顶部上施加图案化掩模;以及(iii)对掩模有选择性地蚀刻膜。

图1示出了除其他特征之外的具有集电极区的衬底以及相应的制造工艺。更具体地说,图1结构10包括包含半导体材料的衬底12。在实施例中,衬底12可以是绝缘体上半导体(SOI)衬底或由任何合适的材料构成的体衬底,该合适的材料包括但不限于Si、SiGe、SiGeC、SiC、GaAs、InAs、InP和其他III/V或II/VI族化合物半导体。衬底12可以是具有任何合适的晶体取向(例如(100)、(110)、(111)或(001)晶体取向)的单晶衬底。

仍参考图1,集电极区14可以设置在衬底12内。例如,集电极区14可以掩埋在衬底12内(例如,掩埋集电极),并且可以包括N+掺杂的注入物。在实施例中,n型掺杂剂可以是例如砷(As)、磷(P)和Sb,以及其他合适的示例。

集电极区14可以通过将一浓度的掺杂剂引入到衬底12中的离子注入工艺形成。例如,在离子注入工艺中,可以使用图案化的注入掩模来限定暴露于注入的选定区域。注入掩模可以包括一层光敏材料,例如有机光致抗蚀剂,其通过旋涂工艺施加、然后进行预烘烤、暴露在通过光掩模投射的光、在曝光后烘烤并用化学显影剂进行显影。每个注入掩模具有足以阻止掩蔽区域接收一剂量的注入离子的厚度和阻止能力。

深沟槽隔离结构16和浅沟槽隔离结构18可以形成在衬底12中。深沟槽隔离结构16和浅沟槽隔离结构18可以通过单独的光刻、蚀刻和沉积工艺形成。例如,将在衬底12上形成的抗蚀剂暴露于能量(光)下以形成图案(开口)。例如反应离子蚀刻(RIE)的具有选择性化学(chemistry)的蚀刻工艺将被用来将图案从光致抗蚀剂转移到衬底12,以在衬底12内形成一个或多个沟槽。在通过常规氧灰化工艺或其他已知的剥离剂去除抗蚀剂之后,可以通过例如化学气相沉积(CVD)工艺的任何常规沉积工艺在沟槽内沉积绝缘体材料(例如,基于氧化物的材料)。衬底12的表面上的任何残留绝缘体材料可通过常规化学机械抛光(CMP)工艺来去除。

可以在浅沟槽隔离结构18之间在衬底12中形成多个阱20。在实施例中,阱20可以通过如本文已经描述的离子注入工艺形成。作为示例,阱20可以是N+掺杂阱。N型掺杂剂可以是例如As或Ph。阱20可用于电连接(例如直接接触)到例如集电极区14的掩埋n+阱。

在图2中,可以在衬底12上形成帽层22和硬掩模24。在实施例中,帽层22可以是SiO

图3示出了多种半导体材料26、28、30,它们的全部都形成在硬掩模24上方和开口26内。在实施例中,多种半导体材料26、28、30可以通过选择性或非选择性的外延生长工艺形成。半导体材料26、30可以是未掺杂的Si材料,以及半导体材料28可以是SiGe材料。SiGe材料28可用于形成升高的SiGe内基极。半导体材料26可用作内发射极区,半导体材料30可用作内集电极区。升高的SiGe内基极位于浅沟槽隔离结构18上/与浅沟槽隔离结构18重叠。在其他实施例中,升高的SiGe内基极延伸到两个浅沟槽隔离结构18。

图4示出了发射极区以及相应的制造工艺。具体地,如图4进一步所示,可以在半导体材料30上方形成基于硅的材料38和帽材料40。基于硅的材料38可以是高度掺杂的N+单晶硅材料。帽材料40可以形成在材料38上方。半导体材料38可以通过外延生长工艺形成;而帽材料40可以通过本领域技术人员已知的毯式沉积工艺形成。帽层40可以是SiN层。可以使用常规光刻和蚀刻工艺对半导体材料38和帽材料40进行图案化,以在半导体材料30上形成发射极区,如参考标号41所示。

在图5中,在发射极区41,即,在半导体材料38和帽层40的侧壁上形成侧壁间隔物材料42。在实施例中,侧壁间隔物材料42可以是SiN材料。通过各向异性蚀刻工艺,可以从结构的水平表面,即,从帽层40和半导体材料30上方去除侧壁间隔物材料42,从而在发射极区41的侧壁上形成间隔物42。

在图6中,通过例如RIE的常规蚀刻工艺对材料22、24、26、28、30进行图案化。例如,SiGe材料28被图案化成升高的SiGe内基极(例如,单晶半导体材料)。外延半导体材料44可以被设置在暴露的材料上,例如,被设置在图案化的材料22、24、26、28、30和阱20上。外延半导体材料44可以是充当外基极的P+掺杂的半导体材料,例如Si材料或SiGe材料。根据本文所述的一些方面,外延半导体材料44围绕发射极区41,例如,围绕发射极材料38。此外,外延半导体材料44可以是Si材料或SiGe材料。外延半导体材料44可以通过间隔物42与发射极材料38分隔。

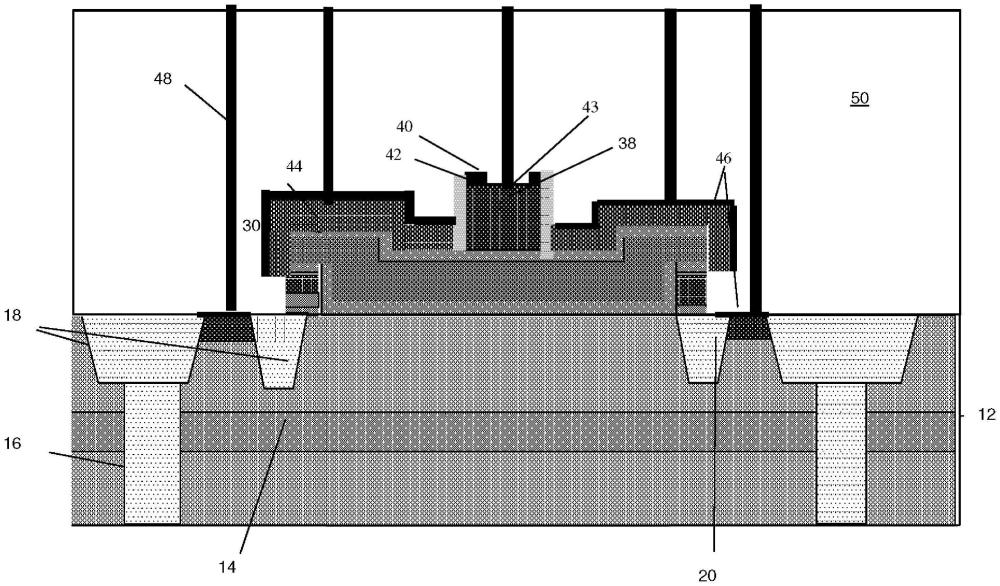

如图7进一步所示,在半导体材料44(例如,外基极)和阱20上形成硅化物46。另外,硅化物46围绕或环绕半导体材料44(例如,外基极)、内基极材料(例如,半导体材料26)和内集电极材料(例如,半导体材料28)。在硅化物工艺之前,可以在帽层40中形成开口43以暴露发射极区41的半导体材料38。这可以通过本文已经描述的常规光刻和蚀刻工艺执行此操作。

本领域技术人员应当理解,硅化物工艺开始于在半导体材料44、多晶硅发射极区41和阱20上方沉积薄过渡金属层,例如,镍、钴或钛。在材料的沉积之后,对结构加热以使过渡金属与暴露的硅(或本文所述的其他半导体材料)发生反应,从而形成低电阻过渡金属硅化物。在反应之后,通过化学蚀刻去除任何剩余的过渡金属,从而在例如阱20、多晶硅发射极区41和外基极44的器件的有源区中留下硅化物接触46。

图7进一步示出了与硅化物46接触并且更具体地与阱20、发射极区41和外基极44接触的互连或接触48。为了形成接触48,层间电介质材料或层间电介质材料的堆叠50(例如SiN和SiO

可以在片上系统(SoC)技术中利用晶体管。SoC是将电子系统的所有部件集成在单个芯片或衬底上的集成电路(也称为“芯片”)。由于部件集成在单个衬底上,因此与具有等效功能的多芯片设计相比,SoC消耗的功率少得多,占用的面积也小得多。因此,SoC正成为移动计算(例如智能手机)和边缘计算市场中的主导力量。SoC也用于嵌入式系统和物联网。

上述方法用于集成电路芯片的制造。所得到的集成电路芯片可以由制造商以原始晶片形式(即,作为具有多个未封装芯片的单个晶片),作为裸芯或以封装形式分发。在后一种情况下,芯片以单芯片封装(例如塑料载体,其引线固定到主板或其它更高级别的载体)或多芯片封装(例如陶瓷载体,其具有表面互连和/或掩埋互连)的形式被安装。在任何情况下,芯片然后与其它芯片、分立电路元件和/或其它信号处理器件集成,作为(a)中间产品(例如主板)或(b)最终产品的一部分。最终产品可以是包括集成电路芯片的任何产品,从玩具和其它低端应用到具有显示器、键盘或其它输入设备以及中央处理器的高级计算机产品。

本公开的各种实施例的描述已经出于说明的目的给出,但并非旨在是穷举的或限于所公开的实施例。在不脱离所描述的实施例的范围和精神的情况下,许多修改和变化对于本领域普通技术人员将是显而易见的。本文中所用术语的选择旨在最好地解释各实施例的原理、实际应用或对市场中发现的技术的技术改进,或者使本技术领域的其他普通技术人员能够理解本文公开的实施例。

- 具有环绕式外基极的晶体管

- 用于具有与FET栅极对准的外基极的双极型晶体管的集成电路结构和方法