GAN垂直型器件中的再生长均匀性

文献发布时间:2023-06-19 11:54:11

相关申请的交叉引用

本申请要求于2020年1月2日提交的题为“GaN垂直型器件中的再生长均匀性”(Regrowth Uniformity in GaN Vertical Devices)的第62/956467号美国临时专利申请的优先权, 该美国临时专利申请的公开内容在此通过引用将其全部内容并入本文,以用于所有目的。

背景技术

目前,包括晶体管和二极管的功率半导体器件已广泛地用于工业电源、电机驱动、消费 者电子设备等应用中。功率半导体晶体管的常见应用是将其用作开关模式电源或电机驱动器 中的开关。在这些应用中,开关的寄生电阻以及开关速度对于电源或电机驱动器的效率而言 是至关重要的。

尽管在功率半导体器件领域取得了一些进展,但相关领域仍需要与再生长均匀性相关的 改进方法和改进系统。

发明内容

本发明涉及半导体制造技术,更具体地,涉及在基于垂直鳍片的FET结构中形成和均匀 地再生长栅极区的大阵列的半导体结构和方法。一种这样的半导体结构包括鳍片阵列,该鳍 片阵列具有由凹陷区包围的多个鳍片,所述凹陷区填充有外延再生长栅极层,该外延再生长 栅极层具有覆盖整个凹陷区的大致均匀的平坦表面。

在本公开的一个方面中,半导体器件可以包括具有第一导电类型的半导体衬底、耦合至 半导体衬底的第一导电类型的漂移层、具有在漂移层上的第一行鳍片和第二行鳍片的鳍片阵 列、以及在第一行鳍片与第二行鳍片之间的间隔。第一行鳍片包括多个第一细长鳍片,所述 多个第一细长鳍片沿着第一行方向彼此平行地布置并且通过第一距离进行分隔,并且第二行 鳍片包括多个第二细长鳍片,所述多个第二细长鳍片沿着第二行方向彼此平行地布置并且通 过第二距离进行分隔。

在第一列中的第一细长鳍片的第一部分和第二细长鳍片的第一部分可以具有在第二列中 的第一细长鳍片的第二部分和第二细长鳍片的第二部分的第二长度的两倍的第一长度。在另 一实施例中,在第一列中的第一细长鳍片的第一部分和第二细长鳍片的第一部分可以具有在 第二列中的第一细长鳍片的第二部分和第二细长鳍片的第二部分的长度的一半的第一长度。 多个第一细长鳍片和多个第二细长鳍片可以具有相同的长度或者可以具有不相等或不均匀的 长度。

在本公开的另一个方面中,用于形成半导体器件的方法可以包括:提供衬底结构,该衬 底结构具有:第一导电类型的半导体衬底、在半导体衬底上的漂移层、在漂移层上并由凹陷 区包围的鳍片阵列。所述鳍片阵列包括彼此平行并且通过一定间隔彼此分隔的第一行鳍片和 第二行鳍片,所述第一行鳍片包括在第一方向上彼此平行地延伸并且以彼此之间的第一距离 布置的多个第一细长鳍片,并且所述第二行鳍片包括在平行于所述第一方向的第二方向上彼 此平行地延伸并且以彼此之间的第二距离布置的多个第二细长鳍片。

该方法还可以包括在漂移层上外延再生长第二导电类型的填充凹陷区的栅极层,所述第 二导电类型与所述第一导电类型相反,所述栅极层围绕所述第一行鳍片和所述第二行鳍片。

与传统技术相比,通过本发明实现了许多益处。例如,本发明的实施例利用鳍片阵列, 该鳍片阵列具有横跨衬底以预定物理布局布置的多行鳍片和多列鳍片,以获得关于鳍片的上 表面(即,FinFET结构)的外延再生长半导体层的均匀平坦表面。

本发明的实施例提供了提供栅极层的均匀再生长的半导体结构和制造该半导体结构的方 法。平坦的再生长栅极层可以减少不同栅极上的厚度变化,因此,栅极电阻率的变化以及基 于鳍片的FET结构之间的等沟道长度提高了半导体器件可靠性。结合下面的正文和附图更详 细地描述本发明的这些和其他实施例及其许多优点和特征。

附图说明

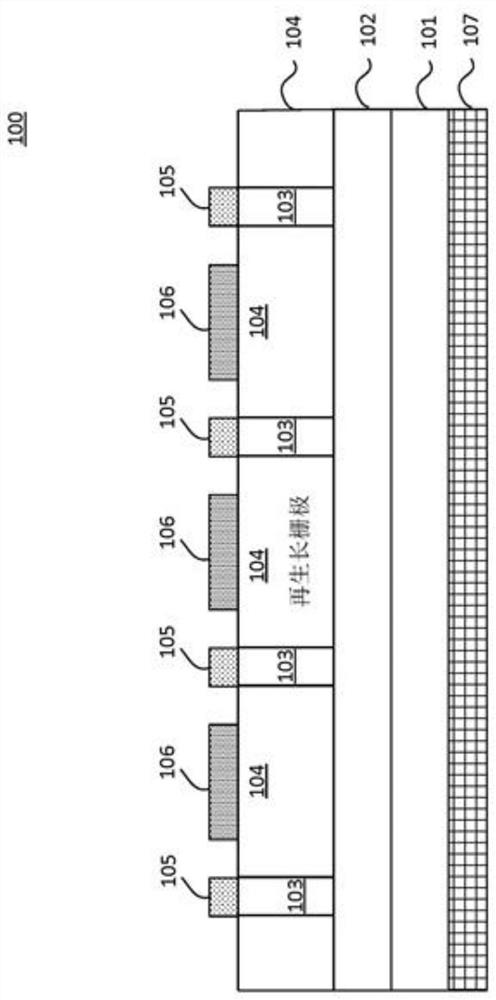

图1是示出了根据本公开实施例的半导体器件的简化截面图;

图2A至图2D是示出了根据本公开实施例的制造半导体器件的简化截面图,所述半导体 器件包括由多个再生长栅极所包围的多个半导体鳍片;

图3是示出了再生长栅极沿半导体鳍片的侧壁变化的简化截面图;

图4A至图4G示出了根据本公开实施例的在相应的200nm、400nm、500nm、550nm、600nm、650nm和800nm再生长晶片上的再生长剖面的结果;

图5是解释了在本公开中所使用术语的鳍片图案布局的平面图;

图6是示出了根据本公开实施例的具有更短长度的半导体鳍片的鳍片图案布局的平面图;

图7A示出了根据本公开实施例的600nm再生长晶片上的生长厚度变化;

图7B示出了根据本公开实施例的800nm再生长晶片上的生长厚度变化;

图8A示出了根据本公开实施例的基于FIB数据的600nm再生长晶片上的生长厚度变化;

图8B示出了根据本公开实施例的基于FIB数据的800nm再生长晶片上的生长厚度变化;

图9A至图9D是示出了根据本公开实施例的800nm再生长晶片的不同鳍片长度的效果 的诺马斯基(Nomarski)对比显微照片图像;

图10A和图10B是示出了根据本公开实施例的25μm鳍片和1000μm鳍片的不同鳍片长 度对800nm再生长晶片(wafer)的影响的高分辨率诺马斯基对比显微照片图像;

图11A至图11D是根据本公开实施例的在800nm再生长晶片上分别示出25μm、50μm、100μm和1000μm鳍片长度的变化(标准偏差σ,范围)的诺马斯基对比显微照片图像;

图12是根据本公开实施例的在500nm再生长晶片上具有2μm节距的0.3μm×25μm(宽 度×长度)鳍片阵列的SEM图像斜视图;

图13是示出了根据本公开实施例的具有短长度的半导体鳍片的鳍片图案布局的平面图;

图14是示出了根据本公开的另一实施例的具有短长度的半导体鳍片的鳍片图案布局的 平面图;

图15是示出了根据本公开的又一实施例的具有短长度的半导体鳍片的鳍片图案布局的 平面图;以及

图16是示出了根据本公开实施例的制造具有鳍片阵列的半导体器件的方法的简化流程 图。

具体实施方式

本发明涉及半导体制造技术,更具体地,涉及在垂直型FET晶体管中形成和均匀地再生 张栅极区的大阵列的半导体结构和方法。Kiziyalli等人在美国申请号9,117,839的文献中描述 了基于垂直鳍片的FET(Field Effect Transistor,场效应晶体管)晶体管结构(“839结构”)。 在“839结构”中,使用半导体鳍片形成晶体管导电沟道,其中该半导体鳍片是通过将周围 材料图案化并将其蚀刻至一定深度来形成的。将具有相反掺杂类型的半导体材料外延再生长 (例如,使用金属有机气相外延法,或MOVPE),以与半导体鳍片的顶部大致平坦。再生 张的材料作为垂直型FET的栅电极,并且施加至栅电极的控制电压对在鳍片顶部(“源极”) 和鳍片底部(通常,漂移区经由半导体衬底进一步连接到“漏”电极)之间的垂直型鳍片沟 道中的电流传导进行调制。

FET的沟道长度由沿垂直型鳍片侧壁的再生长栅极区的高度(厚度)来确定。在典型的 开关晶体管中,许多鳍片被布置成行和列的大的x×y阵列,并且所有鳍片在相同的晶向上对 齐。这样的阵列可能包含数百到数万个平行的鳍片。

由于期望的外延生长发生在鳍片之间的区域中并且在由硬掩膜保护的鳍的顶部上不期望 进行生长,因此栅极材料的再生长需要本领域已知的作为选择性区域生长的技术。

已知的是选择性区域生长的外延生长速率受到许多参数的影响,包括硬掩膜和再生长区 的相对面积。在Tomonari Shioda等人于2009年的量子电子学中所选主题的IEEE期刊中公开 的“用于多色发射的氮化物半导体的选择性区域有机金属气相外延”(SelectiveArea Metal-Organic Vapor Phase Epitaxy of Nitride Semiconductors forMulticolor Emission)中描述了 氮化物半导体的选择性外延生长,其全部内容通过引用并入本文。

用于构建均匀选择性生长的技术涉及在大硬掩膜中构建大体上等轴形状(例如,圆孔、 六边形环形物)的开口的规则阵列。在这种设计中,硬掩膜在面积上与发生外延生长的开口 相应或者更大。

可以利用通常小于总表面积30%的硬掩膜来形成基于垂直鳍片的FET器件结构阵列。此 外,硬质掩膜具有非常细长的矩形形状,其中该矩形的长/宽比通常大于50:1。另外,阵列可 以在每个方向上延伸超过1mm(毫米),并且在横跨该区的再生长的期望不均匀性小于标称 再生长厚度的2%。

本发明人已经发现,生长的局部均匀性(从栅极区到栅极区的鳍片之间再生长的高度(厚 度)的均匀性)进一步由鳍片阵列的物理布局来确定,具体地,由鳍片在长维度上相对于由 再生长条件确定的特征长度的长度来确定。因此,本发明人提供了构建鳍片阵列设计的最佳 方法,以实现栅极再生长的最佳均匀性,并因此实现横跨大面积的阵列中不同鳍片之间的沟 道长度的最小变化。

如上所述,对于给定阈值电压,垂直型JFET沟道导电性随着导电沟道(即,垂直鳍片) 的厚度(或高度)的减少而得以改善。为了获得大的驱动电流,鳍片阵列包括多个垂直鳍片, 期望的是接触仅为垂直鳍片宽度的大小(例如,自对准接触)。形成这种接触需要对表面的 局部形貌进行良好的控制,这将在下面详细说明。

为了减少开关的电阻并且减少限制开关速度的寄生电容,所期望的是增加单位面积的导 电性。电流主要是垂直的开关晶体管提供了减少的单位面积电阻。通过将晶体管的控制沟道 布置成位于垂直方向上(例如,“沟槽”沟道晶体管),可以进一步改善这种益处。晶体管 的电阻具有几个部分,包括晶体管沟道的电阻(电流由输入栅极电压直接地控制的区)、“漂 移”区的电阻(被设计成保持晶体管的击穿电压的区)以及起始衬底、接触、金属等的电阻。

可以通过将半导体材料从硅改变为宽带隙材料(例如氮化镓)来提供更高的击穿临界场, 从而改善开关电阻和电容。与类似硅器件相比,更高的临界电场允许器件的高电压漂移区做 得更薄,且被更重度地掺杂,从而减少漂移区的比电阻(电阻×面积),以及减少对于给定 管芯尺寸的器件导通电阻。

需要减少晶体管的沟道电阻以满足漂移区的比电阻的改善,以避免对开关性能的限制。 对于氮化镓器件,这包括在沟道(垂直方向上的控制区,其确定沟道导通电阻)的垂直长度 上提供具有良好控制的开关晶体管沟道的密集阵列。类似地,对于给定阈值电压,垂直型JFET 沟道导电性随着导电沟道宽度的降低而得以改善,因为掺杂浓度必须增加为~√(1/W

图1是示出了根据本公开实施例的半导体器件100的简化截面图。参考图1,半导体器 件100包括:半导体衬底101(其可以形成JFET器件的漏极)、半导体衬底101上的外延漂移区102、外延漂移区102上的多个鳍片103、以及围绕多个鳍片103的再生长栅极区104。 半导体器件100还包括位于多个鳍片103的上表面上的源极金属层105、位于再生长栅极区104上的栅极金属层106以及位于半导体衬底101的底表面上的漏极金属层107。在一个实施例中,再生长栅极区104的上表面基本上与多个鳍片103的上表面齐平。

在一个实施例中,半导体衬底是n+掺杂的衬底,外延漂移区是n-掺杂的区,鳍片包括n 掺杂的半导体材料,并且再生长栅极区是p掺杂的区。符号“n+”、“n”和“n-”表示半导体衬底、鳍片和外延漂移区之间的相对掺杂浓度。在该实施例中,n掺杂的鳍片具有比n-掺杂的外延漂移区更高的n型掺杂剂浓度,并且半导体衬底比n掺杂的鳍片掺杂得更重。实际掺杂剂浓度可以根据所选择的半导体材料和半导体器件的电压等级而大范围地变化。在一些 实施例中,n+掺杂的半导体衬底可以是具有在约5×10

图2A至图2D是示出了根据本公开实施例的制造半导体器件200的简化截面图,半导体 器件200包括具有多个再生长栅极的多个半导体鳍片。参照图2A,提供了n+掺杂的半导体 衬底201,在n+掺杂的半导体衬底201上外延生长n-掺杂的半导体层202,并且在n-掺杂的 半导体层202上外延生长n-掺杂的半导体层203f。在一个实施例中,n掺杂的半导体层202 形成半导体器件的漂移区,并且掺杂有n型掺杂剂,例如氮。在n掺杂的半导体层203f上形 成图案化硬掩膜层211。图案化硬掩膜层可以包括二氧化硅或氮化硅。在一个实施例中,可 通过PECVD(等离子体增强化学气相沉积)来形成图案化硬掩膜层。在另一实施例中,可以 利用基于氟的化学试剂使用RIE(反应离子刻蚀)来形成图案化硬掩膜层。在一个实施例中, 图案化硬掩膜层可以包括与N掺杂的半导体层203f的表面接触的耐火金属、金属合金、或金 属氮化物(例如,TiN)。在一个实施例中,n+掺杂的半导体衬底201可以是n+掺杂的III族氮化物化合物衬底。虽然本发明的实施例是关于在底层“上”形成一个或多个半导体层来描述的,但是应当理解,包括缓冲层、黏附层等的额外的外延层可以存在于本文示出的层之间。另外,虽然在本文以单独层的形式来描述外延层,但这不是本发明的实施例所需要的,并且包括再生长外延材料的各种外延层可以包括多个子层。因此,提供了复杂的外延结构,外延结构包括直接地沉积在底层上的多个外延层和/或多个再生长材料层,或者包括在附图中 示出的相邻层之间的一个或多个附加层。

图2B是示出了在已执行蚀刻工艺以获得由凹陷区209分隔的多个半导体鳍片203之后 的半导体器件结构的截面图。应注意的是,在蚀刻工艺之后,鳍片的底部可以具有与图2B 中所示的形状不同的形状。本发明实施例在本文中是参考作为发明的理想化实施例和中间结 构的截面图来描述的。为了清楚起见,附图中的层和区的厚度将不是按比例绘制的。由例如 制造技术和/或公差所造成的图示中的形状变化是可以预料的。因此,本发明的实施例不应被 解释为限于本文所示的区的特定形状,而应包括由制造所造成的形状上的偏差。在下面的附 图中,鳍片的底部分被示出为与漂移区的表面呈90度角,即,鳍片被示出为具有矩形截面形 状。应理解的是,鳍片的底部分可以具有圆形或弯曲特征。因此,图中示出的区在本质上是 示意性的,并且这些区的形状并不旨在示出器件区的实际形状,并且并不旨在限制本发明的 范围。

图2C是示出了已在凹陷区209中外延再生长栅极区204之后的器件结构的截面图。在 一个实施例中,再生长栅极区204可以包括p型III族氮化物层,该p型III族氮化物层在凹 陷区中外延且均匀地生长,直至厚度与鳍片203的上表面大致平坦。在一个实施例中,p型 III型氮化物层可以掺杂具有约1×10

图2D是示出了在鳍片203的上表面上形成源极金属层205并且在再生长栅极区204上 形成栅极金属层206之后的半导体器件结构的截面图。在一个实施例中,漏极金属层207也 可以形成在半导体衬底201的底表面上。

图3是示出了再生长栅极沿半导体鳍片的侧壁变化的简化截面图。参考图3,半导体器 件300包括:衬底301、衬底301上的漂移区302、漂移区302上的多个鳍片303、漂移区302 上的并且围绕鳍片的再生长栅极区304。由于布局设计和/或光刻和/或蚀刻工艺变化,鳍片可 以具有不同的高度,和/或再生长栅极具有不同的高度(厚度)。在图3所示的示例中,再生 长栅极区304包括:具有与鳍片303的上表面大致齐平的上表面的第一再生长栅极304a、具 有比鳍片303的上表面低的上表面的第二再生长栅极304b、具有比鳍片303的上表面低的上 表面的第三再生长栅极304c,具有与鳍片303的上表面大致齐平的上表面的第四再生长栅极304d,以及具有比鳍片303的上表面低的上表面的第五再生长栅极304e。在接触形成之前可 能需要对再生长栅极区的非均匀厚度(或垂直于衬底301的表面测量的高度)进行额外的处 理。在不进行额外的处理来获得再生长栅极区的厚度均匀性,不均匀的厚度将导致以下一种 或多种问题:栅极金属层对于不同的栅极(304a、304b、304c)具有不同的厚度,这导致金 属栅极电阻率变化;由不相等的沟道长度所导致的在短的再生长栅极区域(例如热点(hot spot))上的高集中度的电流可能超过最大允许温度值并降低器件可靠性;自对准接触的不 均匀形貌以及更高的漏电流。

图4A至图4G示出了根据本公开实施例的在相应的200nm、400nm、500nm、550nm、600nm、650nm和800nm再生长晶片上的再生长分布的实验结果。图4A是示出了1.8/2.0 (沟槽宽度/鳍片节距)鳍片阵列中的200nm再生长衬底上的相邻半导体鳍片之间的凹陷中 的半导体层的垂直再生长剖面的SEM(扫描电子显微镜)图像。200nm再生长工艺的横向部 分下方存在有空隙410。这些空隙410位于保护层中,该保护层仅用于保护用于聚焦离子束(focused ion beam,FIB)测量和表征工艺的结构。在于正常工艺中不存在空隙410和保护层, 并且仅作为用于FIB过程的制备措施的结果时出现空隙410和保护层。

图4B是示出了1.8/2.0(沟槽宽度/鳍片节距)鳍片阵列中的400nm再生长衬底上的相邻 半导体鳍片之间的沟槽中的半导体层的垂直再生长剖面的SEM图像。对于该400nm再生长, 在相邻半导体鳍片之间存在谷412。应注意的是,在硬掩膜上方存在层401。层401是仅为保 护FIB工艺的结构而需要的保护层。在再生长工艺中不存在层401,层401仅需要作为FIB 工艺的制备措施的结果产生的。

图4C是示出了1.8/2.0鳍片阵列中的500nm再生长衬底上的相邻半导体鳍片之间的沟槽 中的半导体层的垂直再生长剖面的SEM图像。在相邻半导体鳍片之间存在凹坑(divot)414。

图4D是示出了1.8/2.0鳍片阵列中的550nm再生长衬底上的相邻半导体鳍片之间的沟槽 中的半导体层的垂直再生长剖面的SEM图像。在相邻的半导体鳍片之间的凹坑418是仍然可 见的。通过将凹坑418与图4C所示的凹坑414进行比较,凹坑418更不深。还可以看出, 图4C和图4D中所示的凹坑414、凹坑418的深度在横向方向和竖直方向上比图4B所示的谷412小。在550nm再生长衬底上的鳍片之间的再生长层几乎实现了平坦表面。层401是用于FIB处理的保护层。根据本公开实施例,不需要伪影(artifact)层401。

图4E是示出了1.8/2.0鳍片阵列中的600nm再生长衬底上的相邻半导体鳍片之间的凹陷 中的半导体层的垂直再生长剖面的SEM图像。再生长半导体层的上表面是大致平坦的并且与 硬掩膜的底表面齐平。

图4F是示出了1.8/2.0鳍片阵列中的650nm再生长衬底上的相邻半导体鳍片之间的沟槽 中的半导体层的垂直再生长剖面的SEM图像。再生长半导体层的上表面是大致平坦的并且在 硬掩膜的底表面上方。因此,本发明人相信,对于本示例中的初始蚀刻沟槽深度,在550nm 和650nm之间的再生长厚度可以为半导体层提供可接受的平坦表面。当然,本领域的普通技 术人员将认识到许多变型、修改和替代。在一个实施例中,有源器件区中的再生长厚度取决 于蚀刻深度和硬掩膜与沟槽之间的宽度比。在另一实施例中,有源器件区中的半导体层的再 生长的平坦度取决于沟槽深度以及鳍片宽度与沟槽宽度之间的比。在一个实施例中,有源器 件区具有约0.8μm(微米)的沟槽深度、约1.8μm的沟槽宽度和约0.2μm的硬掩膜宽度(即, 鳍片宽度是约0.2μm),使得有源器件区中的沟槽与硬掩膜之间的宽度比是0.9(1.8/0.2), 以获得再生长厚度在550nm和650nm之间的再生长半导体层的平坦表面。

通过对半导体层执行额外的外延再生长以产生更厚的再生长层,再生长半导体层将在硬 掩膜层的上表面上方突出,如图4G所示。本发明人相信,在550nm和650nm之间的再生 长厚度可以为半导体层提供可接受的平坦表面。

图5是解释了在本公开中所使用术语的鳍片图案布局的平面图。将描述和/或定义几个术 语以便于更好地理解本公开。参考图5,鳍片的阵列(即鳍片阵列)500包括多个细长鳍片 503,细长鳍片503通过图案化凹陷区511彼此分隔。两个相邻的细长鳍片之间的距离被称为 节距P。每个细长鳍片具有宽度W和长度L,其中在Y方向上的单个鳍片的情况下,长度L 也被称为鳍片阵列长度AL。在一个实施例中,细长鳍片具有0.2μm的宽度和1000μm的长度。在一个实施例中,两个相邻的细长鳍片之间的节距约为2μm,且图案化凹陷区的深度约为0.7μm至0.8μm。长鳍片被称为具有大于100μm(例如700μm、1000μm)长度的鳍片。 细长鳍片被称为具有大于10倍鳍片宽度的长度的杆状鳍片。参照图5,杆状鳍片在X方向上 彼此平行地布置并且沿Y方向延伸。图案化凹陷区的深度和鳍片的高度在Z方向上延伸出鳍 片阵列的表面(即,X-Y平面)。参照图3,衬底表面的法线与z轴对准。

图6是示出了根据本公开实施例的具有多个半导体鳍片的鳍片阵列600的鳍片图案布局 的平面图,其中所述半导体鳍片鳍片具有短长度。短鳍片被称为具有小于100μm(例如50μm、 25μm)的长度的杆状鳍片。换句话说,通过将长鳍片分解成多个小鳍片段来形成短鳍片。例 如,长度为1000μm的长鳍片可以分成40多个短鳍片,每个短鳍片的长度为25μm。参照图 6,鳍片阵列600包括以多个行(第1行、第2行、第3行)和多个列(第1列、第2列…第 n列)排列的多个短鳍片。每行中的短鳍片以间隔P彼此分隔。每行以间隔S(即,每行之间 的间隙)彼此分隔。现在阵列的总长度通过AL=N×L+(N-1)×S与单独的鳍片长度L、 行数目N和间隔S相关。在一个实施例中,间隔S具有等于间隔P的尺寸。在另一实施例中, 间隔S可以具有大于单个间隔P的尺寸(例如,1.2×P、1.5×P,或2×P)。可以理解的是, 行数目和列数目可以是任何整数。在一个实施例中,不同行中的列数目可以是不同的,例如, 以实现阵列的“舍入(rounding)”,以用于改善的结终止的边缘设计。在图6所示的示例中, 示出了在每行中使用六个短鳍片,共三行和六列,但是应当理解的是,为了描述示例性实施 例,可任意选择短鳍片的数量目以及行量目和列量目,并且不应当是限制性的。

在一个示例性实施例中,鳍片长度L约为25μm,鳍片宽度W约为0.2μm,沿着z方向测量的鳍片厚度或鳍片高度约为0.8μm,节距P在1.5μm至2.5μm之间的范围内。在一个 实施例中,鳍片宽度W和两个相邻鳍片之间的节距P之间的比在约0.08至0.13之间的范围 内,优选地在0.1至0.12之间的范围内。在一个实施例中,鳍片长度L和两个相邻鳍片之间 的节距P之间的比在5至25之间的范围内,优选地在10至20之间,更优选地在12至16 之间。在一个实施例中,鳍片长度L为约25μm,并且鳍片宽度W在0.15μm至0.7μm之间 的范围内。

图7A示出了根据本公开的一个实施例的具有2μm节距的0.3μm×1000μm长鳍片阵列 中的600nm再生长衬底(晶片)上的厚度变化的垂直生长剖面。图7A包括示出了晶片中心上的生长剖面的顶部分以及示出了晶片边缘上的生长剖面的底部分。图7A的左侧部分示出了衬底中心(顶部分)上的管芯的左侧部分的生长剖面和衬底边缘(底部分)上的管芯的左侧部分的生长剖面。图7A的中心部分示出了在衬底中心(顶部分)上的管芯的中心部分的生长剖面以及在衬底边缘(底部分)上的管芯的中心部分的生长剖面。图7A的右侧部分示出了在衬底中心(顶部分)上的管芯的右侧部分的生长剖面以及在衬底边缘(底部分)上的管芯的右侧部分的生长剖面。如图7A所示,鳍片之间的再生层具有横跨管芯的大致均匀的厚度,即,当从管芯的左侧到中心再到管芯的右侧扫描时,厚度变化很微小。

图7B示出了根据本公开的一个实施例的具有2μm节距的0.3μm×1000μm长鳍片阵列 中的800nm再生长衬底(晶片)上的生长厚度变化。图7B的左侧部分示出了衬底中心(顶部分)上的管芯的左侧部分的生长剖面以及衬底边缘(底部分)上的管芯的左侧部分的生长剖面。图7B的中心部分示出了在衬底中心(顶部分)上的管芯的中心部分的生长剖面以及在衬底边缘(底部分)上的管芯的中心部分的生长剖面。图7B的右侧部分示出了在衬底中心(顶部)上的管芯的右侧部分的生长剖面以及在衬底边缘(底部分)上的管芯的右侧部分的生长剖面。参照图7B,管芯的厚度是不均匀的,即,厚度根据管芯的扫描位置变化。例如,管芯的中心区处的厚度看起来大于管芯的左边缘和右边缘处的厚度。这将在图11A至图11D中确认。

图8A示出了根据本公开实施例的基于FIB数据的具有2μm节距的0.3μm×1000μm长鳍片阵列中的600nm再生长衬底(晶片)上的生长厚度变化。x轴表示管芯位置(即,管芯 在衬底上的测量位置)。中心/左表示从衬底中心上的管芯的左侧部分进行的测量。中心/中心表示从衬底中心上的管芯的中心部分进行的测量。中心/右表示在衬底中心上的管芯的右侧部 分的测量。边缘/左表示从衬底边缘上的管芯的左侧部分进行的测量。边缘/中心表示从衬底边 缘上的管芯的中心部分进行的测量。边缘/右表示从衬底边缘上的管芯右侧进行的测量。y轴 表示在鳍片的上表面上的硬掩膜层的衬底(底表面)上方的半导体层再生长厚度的高度,单 位为nm。参照图8A,横跨管芯位置的厚度变化在的50nm至180nm之间的范围内。在相同 的位置取自具有管芯的不同衬底的厚度变化很小,例如小于30nm。

图8B示出了根据本公开实施例的基于FIB数据的具有2μm节距的0.3μm×1000μm长鳍片阵列中的800nm再生长衬底(晶片)上的生长厚度变化。x轴表示管芯位置(即,管芯 在衬底上的测量位置)。中心/左表示从衬底中心上的管芯的左侧部分进行的测量。中心/中心表示从衬底中心上的管芯的中心部分进行的测量。中心/右表示在衬底中心上的管芯的右侧部 分的测量。边缘/左表示从衬底边缘上的管芯的左侧部分进行的测量。边缘/中心表示从衬底边 缘上的管芯的中心部分进行的测量。边缘/右表示从衬底边缘上的管芯右侧进行的测量。y轴 表示在鳍片的上表面上的硬掩膜层的衬底(底表面)上方的半导体层的再生长厚度的高度, 单位为nm。参照图8B,厚度变化在120nm至540nm之间的范围内。在相同的位置取自具 有管芯的不同衬底与的厚度变化更大。例如,取自从衬底边缘处的管芯的左侧部分的管芯的 厚度变化可以在120nm至460nm之间变化,具有280nm的平均厚度值。800nm再生长衬 底导致与600nm再生长衬底相比更大的厚度变化。因此,本发明人已开发并在本文描述了一 种在凹陷区中外延再生长半导体层的方法,该凹陷区以在450nm至650nm的范围内分隔鳍 片,以获得均匀厚度的外延再生长半导体层。下面将详细描述该方法。

图9A至图9D是根据本公开实施例的诺马斯基对比(Nomarski-contrast)显微照片图像, 该图像示出了分别对于25μm、50μm、100μm和1000μm长鳍片的800nm再生长晶片的不同鳍片长度的效果。参照图9A至图9D,斑纹随着鳍片长度的增加而增加。图9A示出了在 25μm长度的鳍片中厚度变化被认为是微小的,而在1000μm长度的鳍片中厚度变化被认为 是显著的(在图9D中)。

图10A和图10B是示出了根据本公开实施例的800nm再生长晶片的针对相应的25μm鳍片和1000μm鳍片的不同鳍片长度的效果的高分辨率诺马斯基对比显微照片图像。在这些图中,图案化硬掩膜层显示为竖直黑线。对于1000μm的鳍片,斑纹外观要更加明显。

图11A至图11D是根据本公开实施例的分别示出在800nm再生长衬底(晶片)上的25μm、50μm、100μm和1000μm鳍片长度的变化(σ(sigma)和范围)的诺马斯基对比显微 照片图像(下方图像)和轮廓仪迹线(上方曲线图)。鳍片长度被定义为沿着图5和图6中 所示的阵列长度方向(y方向)延伸的细长杆。横轴代表从管芯的0μm到1200μm的扫描距 离。垂直轴代表高度(外延再生长半导体层的厚度)。图11A包括顶部分和底部分,该顶部 分示出了25μm长度鳍片的范围为

图12是根据本公开实施例的在500nm再生长晶片上具有2μm节距的0.3μm(宽度)×25μm(长度)鳍片阵列的斜视图SEM图像。参照图12,25μm高鳍片阵列的外延再生长半 导体层的表面是光滑的。也就是说,外延再生长半导体层的厚度变化很小。

本发明人已经确定具有短鳍片(即,长度小于100μm)的鳍片阵列具有半导体材料的良 好的均匀再生长性,即,外延再生长栅极层的表面横跨凹陷区(从鳍片之间的沟槽到沟槽) 上是均匀的,如图1所示。作为示例,根据实施例,利用图6中所示的鳍片阵列的布局结构, 其中每个长鳍片被划分(分割)成多个短鳍片。在一个实施例中,参考图1和图6,鳍片阵 列的物理布局结构至少包括第一行鳍片(例如,图6中的第2行)和第二行鳍片(图6中的第3行),鳍片沿着阵列宽度的方向(即,沿着行的方向)彼此平行地布置。布置在鳍片阵 列的第一行中的鳍片彼此间隔第一节距,并且布置在鳍片阵列的第二行中的鳍片彼此间隔第二节距。在一个实施例中,第一节距和第二节距具有相同的宽度。在一个实施例中,第一行鳍片和第二行鳍片彼此间隔与第一节距或第二节距大致相同的间隔。在一个实施例中,鳍片 的宽度小于1.0μm,并且鳍片之间的间隔小于2.5μm。在一个实施例中,鳍片的宽度为0.3μm 或更小,并且鳍片之间的间隔小于2.0μm。在一个实施例中,鳍片的长度小于50μm。在一个实施例中,鳍片的长度为25μm或更小。

图13是示出了根据本公开实施例的包括鳍片阵列的集成电路(半导体器件)1300的鳍 片图案布局的平面图,所述鳍片阵列具有多个短半导体鳍片1303。参考图13,集成电路(半 导体器件)1300包括鳍片阵列1311,鳍片阵列1311具有第一行鳍片1312和第二行鳍片1313。 第一行鳍片1312彼此平行地布置并且彼此间隔第一节距P1。第二行鳍片彼此平行地布置并 且彼此间隔第二节距P2。第一行和第二行彼此间隔一定间隔S。在一个实施例中,间隔S大 致等于第一节距P1或第二节距P2。在一个实施例中,第一节距P1和第二节距P2具有相同 的尺寸(即,相邻鳍片列之间的距离相同)。在一个实施例中,鳍片阵列宽度由列数目(第 1列到第n列)确定,所述列大致垂直于第一行和第二行。在一个实施例中,鳍片中的每一 者的宽度在0.15μm至0.3μm的范围内,优选地为0.2μm,并且鳍片中的每一者的长度在10 μm至100μm的范围内,优选地为50μm,更优选地为25μm。在一个实施例中,集成电路 (半导体器件)1300还可以包括外延再生半导体层(图1的再生长栅极区104),该外延再 生半导体层围绕鳍片且具有与鳍片的上表面大致齐平或呈平面的均匀表面。在一个实施例中, 集成电路1300还可以包括栅极金属层1306(示出为带点表面图案),该栅极金属层覆盖外 延再生长半导体层(未示出)并且围绕鳍片(通过开口1309与鳍片分离),以形成类网状栅 极结构,从而减少栅极金属接触的电阻。针对高频应用,在本发明的一些实施例中利用金属栅极层的类网状栅极结构来降低栅极金属接触电阻。在一个实施例中,鳍片设置在漂移层(图 1的漂移层102)上,漂移层又设置在衬底(图1的半导体衬底101)上。在一个实施例中,衬底是n+掺杂的GaN衬底,漂移层是n-掺杂的GaN层,鳍片包括n掺杂的GaN层,并且外 延再生长半导体层是p掺杂的GaN栅极层。在一个实施例中,栅极金属层包括TiN。在一个 实施例中,源极金属接触(图1的源极金属层105)设置在鳍片的上表面上。栅极金属层1306 的开口1309形成围绕鳍片的源极金属接触的多个壕沟。在一个实施例中,集成电路1300是 由围绕多个导电沟道的公共控制栅极组成的晶体管器件。图1示出了集成电路1300的一部分 的截面图。

图14是示出了根据本公开的另一实施例的具有鳍片阵列的集成电路(半导体器件)1400 的可替代的物理布局的平面图,所述鳍片阵列包括多个短半导体鳍片。参考图14,集成电路 1400包括鳍片阵列1401,鳍片阵列1401具有多个半导体鳍片1403,半导体鳍片1403在第 一方向上隔开第一距离1411并且在第二方向上隔开第二距离1412,第一方向朝第二方向倾 斜一定角度。在一个实施例中,第一距离1411等于第二距离1412。在一个实施例中,第一 距离1411不等于第二距离1412。在一个实施例中,第一方向与第二方向之间的角度小于90 度,优选地所述角度在10度至80度的范围内,更优选地所述角度在30度至60度之间。在 一个实施例中,半导体鳍片在平行于第一方向和第二方向的方向上是对准的,并且第一方向 和第二方向偏移45度的角度。

图15是示出了根据本公开的又一实施例的具有鳍片阵列的集成电路1500的鳍片图案布 局的平面图,所述鳍片阵列包括多个短半导体鳍片。参考图15,集成电路1500包括鳍片阵 列1501,鳍片阵列1501具有多个半导体鳍片1503/1513,半导体鳍片1503/1513在第一方向 上隔开第一距离1511,并且在第二方向上隔开第二距离1521和第三距离1522。第一方向可 以与第二方向正交。在一个实施例中,第二距离1521等于第一距离1511,第三距离1522等 于第一距离1511的一半。在一个实施例中,鳍片阵列边缘处的鳍片长度是鳍片阵列中心部分 (未示出)处的鳍片长度的两倍。在一个实施例中,鳍片阵列中的鳍片在第一方向和第二方 向上交替地布置。在示例性实施例中,鳍片阵列包括在鳍片阵列的相对边缘处的第一鳍片1503 以及交替地布置在第一鳍片1503之间的第二鳍片1513。第一鳍片1503长度是设置在其间的 第二鳍片1513长度的两倍。

图16是示出了根据本公开实施例的制造具有鳍片阵列的半导体器件的方法1600的简化 流程图。方法1600包括:提供半导体结构,所述半导体结构具有第一导电类型的半导体衬底、 在半导体衬底上的漂移层、以及在漂移层上的具有多个半导体鳍片的鳍片阵列(1601)。鳍 片由凹陷区包围。所述鳍片阵列至少包括第一行鳍片和第二行鳍片,所述第一行鳍片和所述 第二行鳍片在第一方向上隔开第一距离并且在第二方向上隔开第二距离。方法1800还包括: 在凹陷区中外延再生长第二导电类型的栅极层(1603)。第二导电类型与第一导电类型相反。 外延再生长栅极层可以具有与鳍片的上表面大致平坦或齐平的上表面。方法1600还包括:在 鳍片的上表面上形成多个源极接触、在外延再生长栅极层上形成一个或多个栅极接触、以及 在半导体衬底的底表面上形成漏极接触(1605)。

在一个实施例中,提供半导体结构可以包括:提供半导体衬底、在半导体衬底上外延生 长漂移层、在漂移层上外延生长具有第一导电类型的半导体层、在半导体层上形成金属层、 在金属层上形成图案化硬掩膜层、以及利用作为掩膜的图案化硬掩膜层来蚀刻金属层和半导 体层,以形成鳍片阵列和形成围绕鳍片阵列的凹陷区。在一个实施例中,半导体衬底是III 族氮化物化合物衬底。在一个实施例中,省略金属层。

在一个实施例中,图案化硬掩膜层包括彼此平行布置并被配置成形成多个半导体鳍片的 细长形状的阵列。在一个实施例中,每个细长形状的宽度在约0.2μm至约0.7μm的范围内, 长度在约25μm至约500μm的范围内,并且两个相邻的细长形状之间的节距在约1.9μm至 约10μm的范围内。本发明的范围并不限于附图中鳍片的布置。在一个实施例中,细长形状 以第一行和第二行布置,所述第一行和所述第二行在第一方向上隔开第一距离并且在第二方 向上隔开第二距离。在一个实施例中,第一方向与第二方向正交。在一个实施例中,第一方 向相对于第二方向以30度至50度范围内的角度偏移,优选地所述角度在35度至45度之间。 在一个实施例中,细长形状具有相同的尺寸,并且第一距离等于第二距离,如图14所示。在 一个实施例中,细长形状具有不均匀的尺寸,并且第一距离不等于第二距离,如图15所示。 本发明人已经观察到,通过使用具有根据图13至图15中所示的物理布局布置的短鳍片的鳍 片阵列,可以获得均匀厚度的外延再生长栅极层,如图11A所示。

在一个实施例中,衬底是包括n-GaN外延层的III-V族化合物衬底,并且栅极层包括p-GaN 再生外延层。在一个实施例中,在850℃至1050℃之间的生长温度下,优选地在950℃生长 温度下,以及在200mbar(毫巴)至大气压力之间的生长压力下,优选地在600mbar至大气 压力之间的生长压力下执行p-GaN再生长。

本文公开的实施例不受此处描述的特定实施例的范围限制。除了这里描述的实施例之外, 本发明的实施例的各种修改对于本领域普通技术人员将从前述描述和附图中变得明了。此外, 虽然本发明的一些实施例已经在特定环境中针对特定目的的特定实现的上下文中描述,但是 本领域普通技术人员将认识到其有用性不限于此,并且本发明的实施例可以有利地在任何数 量的环境中针对任何数量的目的来实施。

- GAN垂直型器件中的再生长均匀性

- 一种基于再生长技术降低GaN HEMT器件欧姆接触电阻的方法及GaN HEMT器件