数字模拟转换器装置与校正方法

文献发布时间:2023-06-19 09:51:02

技术领域

本案是有关于一种数字模拟转换器装置,且特别是有关于在校正时使用非二进制算法的电流导向式数字模拟转换器。

背景技术

数字模拟转换器常见于各种电子装置中。在相关技术中,数字模拟转换器常在校正时使用二进制的编码方式进行操作。然而,当数字模拟转换器的内部电路在校正时出现错误时,二进制的编码方式无法有效改善上述错误。

发明内容

为了解决上述问题,本案的一些实施方式提供一种数字模拟转换器(digital-to-analog converter,DAC)装置,其包含电流导向式DAC电路系统与校正电路系统。电流导向式DAC电路系统根据一输入信号的多个最低有效位产生一第一信号,并根据该输入信号的多个最高有效位产生一第二信号。校正电路系统响应于该第一信号与该第二信号的一比较结果执行非二进制搜寻算法以产生校正信号,以根据校正信号校正电流导向式DAC电路系统。

本案的一些实施方式提供一种校正方法,其包含下列操作:通过电流导向式DAC电路系统根据输入信号的多个最低有效位产生第一信号,并根据该输入信号的多个最高有效位产生第二信号;以及响应于该第一信号与该第二信号执行非二进制搜寻算法以产生一校正信号,并根据该校正信号校正该电流导向式DAC电路系统。

综上所述,本案实施例提供的DAC装置与校正方法可利用非二进制搜寻算法校正电流导向式DAC,以提升DAC装置的整体可靠度并节省校正时需耗费的运作时间。

附图说明

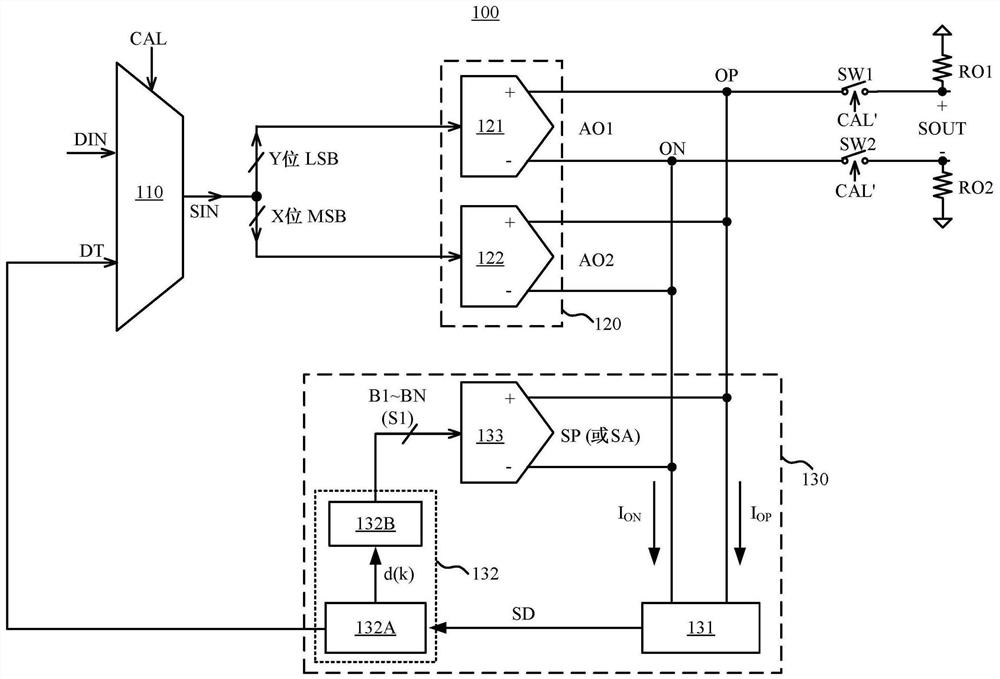

图1为根据本案一些实施例所绘示之的数字模拟转换器(digital-to-analogconverter,DAC)装置的示意图;

图2为根据本案一些实施例所绘示图1中多个DAC电路的电流源电路的设置示意图;

图3为根据本案一些实施例所绘示的一种非二进制搜寻算法的操作示意图;以及

图4为根据本案一些实施例所绘示的一种校正方法的流程图。

具体实施方式

本文所使用的所有词汇具有其通常的意涵。上述的词汇在普遍常用的字典中的定义,在本说明书的内容中包含任一于此讨论的词汇的使用例子仅为示例,不应限制到本公开内容的范围与意涵。同样地,本公开内容亦不仅以于此说明书所示出的各种实施例为限。

在本文中,使用第一、第二与第三等等的词汇,是用于描述各种组件、组件、区域、层与/或区块是可以被理解的。这些词汇只限于用来辨别单一组件、组件、区域、层与/或区块。因此,在下文中的一第一组件、组件、区域、层与/或区块也可被称为第二组件、组件、区域、层与/或区块,而不脱离本案的本意。本文中所使用之“与/或”包含一或多个相关联的项目中的任一者以及所有组合。

关于本文中所使用之“耦接”或“连接”,均可指二或多个组件相互直接作实体或电性接触,或是相互间接作实体或电性接触,亦可指二或多个组件相互操作或动作。

于本文中,用语“电路系统(circuitry)”泛指包含一或多个电路(circuit)所形成的单一系统。用语“电路”泛指由一或多个晶体管与/或一或多个主被动组件按一定方式连接以处理信号的对象。

为易于理解,各附图中的类似组件将被指定为相同标号。

图1为根据一些实施例所绘示的数字模拟转换器(digital-to-analogconverter,DAC)装置100的示意图。

DAC装置100包含多任务器电路系统110、DAC电路系统120以及校正电路系统130。多任务器电路系统110根据模式控制信号CAL输出数据信号DIN或测试信号DT,以作为输入信号SIN。例如,当模式控制信号CAL具有逻辑值0,DAC装置100操作于一般模式,且多任务器电路系统110输出数据信号DIN为输入信号SIN。或者,当模式控制信号CAL具有逻辑值1,DAC装置100操作于校正模式,且多任务器电路系统110输出测试信号DT为输入信号SIN。

DAC电路系统120耦接至多任务器电路系统110,以接收输入信号SIN。DAC电路系统120包含多个DAC电路121与122。DAC电路121根据输入信号SIN中的Y个最低有效位(leastsignificant bit,LSB)产生信号AO1。DAC电路122根据输入信号SIN的X个最高有效位(mostsignificant bit,MSB)产生信号AO2。

在一些实施例中,输入信号SIN的X个最高有效位及/或测试信号DT的X个最高有效位可由对应的热码(thermometer code)所取代,所述对应的热码具有(2

于一些实施例中,DAC电路系统120为一电流导向式(current-steering)DAC电路系统。电流导向式DAC电路系统可由多个电流源电路实施,其可依据输入信号SIN启动,以输出相应的电流信号来作为信号AO1或AO2。

于一些实施例中,DAC装置100还包含电阻RO1~RO2与多个开关SW1~SW2。电阻RO1~RO2分别耦接至多个DAC电路121与122的多个输出端OP与ON,以将多个信号AO1与AO2转换成电压形式的模拟输出SOUT。

开关SW1与SW2分别耦接至DAC电路系统120的多个输出端以及电阻RO1~RO2。当操作于校正模式时,开关SW1~SW2响应于模式控制信号CAL’而不导通,其中模式控制信号CAL’为模式控制信号CAL的互补信号。如此,于校正模式下,信号AO1与AO2可正确地传送至校正电路系统130。或者,当操作于一般模式时,开关SW1~SW2响应于模式控制信号CAL’导通。如此,于一般模式时,信号AO1~AO2可传送至电阻RO1~RO2。

于一些实施例中,校正电路系统130耦接至DAC电路系统120,并在校正模式下基于信号AO1与AO2校正DAC电路122。于一些实施例中,校正电路系统130包含检测电路131、数字控制器电路132以及DAC电路133。

检测电路131耦接至DAC电路121~122的多个输出端OP与ON,以接收信号AO1与AO2。于一些实施例中,检测电路131比较信号AO1与信号AO2,以产生检测信号SD。检测信号SD用于指示信号AO1与信号AO2之比较结果。于一些实施例中,检测电路131可由电流比较器或量化器等等电路实现,但本案并不以此为限。

数字控制器电路132耦接至多任务器电路系统110与检测电路131。于一些实施例中,数字控制器电路132设置有一内存(未绘示),其储存默认的测试信号DT,以在校正模式下提供测试信号DT至多任务器电路系统110。于一些实施例中,数字控制器电路132还响应于检测信号SD来执行一校正运算,以产生校正信号S1。

例如,数字控制器电路132可根据检测信号SD执行一非二进制(non-binary)的搜寻算法,以决定校正信号S1的多个位B1~BN。于一些实施例中,数字控制器电路132包含校正电路132A与编译码器电路132B。校正电路132A执行非二进制搜寻算法,以产生位d(k),其中k为1,2,…,M。编译码器电路132B用以根据位d(k)执行编码(或译码)操作,以产生多个位B1~BN。在一些实施例中,数字控制器电路132亦可由加法器及缓存器所实现,以执行非二进制(non-binary)的搜寻算法。

DAC电路133耦接至DAC电路122与数字控制器电路132。在校正模式下,DAC电路133根据校正信号S1输出调整信号SA。在校正模式执行完后,校正信号S1的多个位B1~BN被决定,以供DAC装置100在一般模式下使用。

于一些实施例中,在一般模式下,DAC电路133根据决定好的校正信号S1输出补偿信号SP,以校正DAC电路122。例如,若DAC电路122为多个单位电流源所实施的电流导向式DAC,补偿信号SP可直接输入至DAC电路122,以修正其对应单位电流源的偏压。如此,可等效校正DAC电路122所输出的信号AO2。

或者,如图1所示,于一些实施例中,DAC电路133直接耦接至DAC电路122的输出。于此设置方式下,DAC电路133可根据校正信号S1导通其内部的对应电流源电路,以产生对应的电流信号(即补偿信号SP)至DAC电路122的多个输出端OP与ON。如此一来,补偿信号SP可与信号AO2直接相加,以等效修正DAC电路122的偏移。

于一些实施例中,控制DAC电路133输出的校正信号S1可由一内存储存,在一般模式的情况下,当有多个MSB(例如为电流源电路122A)被开启时,可加总所述多个MSB所对应的校正信号S1,来控制DAC电路133。

图2为根据本案一些实施例的设置方式所绘示图1中多个DAC电路121、122以及133中的电流源电路的设置示意图。

于一些实施例中,DAC电路121、122以及133皆可由电流导向式DAC电路实现。于此例中,Y等于3,即多个电流源电路121A分别由LSB的多个位L1~L3控制;X等于2,对应到M1~M3(如热码),即多个电流源电路122A分别由MSB的多个位M1~M3控制;N=4,即多个电流源电路133A分别由校正信号S1中的多个位B1~BN控制。

举例而言,若LSB以二进制编码(binary code)编码且MSB以热码编码,则多个电流源电路121A的多个电流(后称电流ILSB)依序相差2倍。例如,如图2所示,多个电流源电路121A(如位L1~L3所对应的电流源电路121A)的电流ILSB依序相差2倍。如图2所示,DAC电路133包含多个电流源电路133A,其电流依序相差2倍(例如为1/2I、1/4I、1/8I等等)。于一些实施例中,DAC电路133的分辨率高于DAC电路122的分辨率。

理想上,多个电流ILSB之的总和应等于单一电流源电路122A的电流(后称电流IMSB)。亦即,ΣILSB=IMSB(后称式1)。然而,由于处理差异与/或电路偏移等影响,电流IMSB将会出现偏移,使得式1无法成立。在一些实施例中,DAC电路121还包含额外的一电流源电路121B,其电流为I,并由位L4所控制,在此情况下,理想上,ΣILSB=IMSB。在一些实施例中,DAC电路133还包含额外的一电流源电路133B,其电流为I/16且设定以经由校正信号S1的一额外位B5控制。

因此,在校正模式下,数字控制器电路132可输出具有特定位值的测试信号DT。于初次测试时,测试信号DT的低权重位(例如为LSB的位L1~L3及位L4)皆为1,而测试信号DT的高权重位(例如为MSB对应的热码M1~M3)中一对应者为0。于此条件下,所有电流源电路121A会导通而输出全部电流ILSB至一输出端(例如为输出端ON);一对应的电流源电路122A会导通而输出单一电流IMSB至另一输出端(例如为输出端OP)。通过此设置方式,检测电路131可比较电流ILSB的总和及所述对应电流源电路122A输出的电流IMSB,以确认两者是否符合式1。若不符合式1,检测电路131可输出相应的检测信号SD。

在一些实施中,测试信号DT中除了该对应者外的高权重位(除了该对应者的热码)一半为0,一半为1,使得剩余的电流源电路122A则平均分配在两个输出端上。在一些实施例中,剩余的电流源电路122A平均分配时产生的误差,可利用输出端交换及相应的算法校正,因所述误差非为本案的重点,故在本案中均默认剩余的电流源电路122A平均分配无误差。

在一些实施例中,数字控制器电路132可响应于检测信号SD来执行非二进制搜寻算法以决定位d(1)。接着,至少一电流源电路133A依据位d(1)输出调整信号SA,以调整信号AO2。检测电路131可比较信号AO1与信号AO2经调整信号SA调整后的信号,以产生下一步阶的检测信号SD。通过相同操作,数字控制器电路132可决定第2个位d(2)。依此类推,检测信号SD逐次被更新,且校正信号S1的多个位B1~BN可被决定。至少一电流源电路133A根据多个位B1~BN导通,以输出对应电流为补偿信号SP。

在一些实施例中,在决定位d(k)的过程中,信号AO1相当于后述的电流I

于一些实施例中,补偿信号SP可与信号AO2直接加总,以等效地校正DAC电路122(如图1所示)。换言之,式1可修正为ΣILSB=IMSB+ISP(后称式2),其中ISP为补偿信号SP对应于两输出端OP与ON之间的电流差,用以补偿IMSB,使IMSB+ISP与ΣILSB相等。如此,通过逐次执行一或多次操作,数字控制器电路132可决定该单一电流源电路133A须修正的偏移量,并记录其对应的校正信号S1至其内存(未绘示)内。

当记录到一个电流源电路122A所对应的补偿信号SP后,数字控制器电路132可将测试信号DT的MSB对应的热码的次一对应者更新为1,并再次执行上述操作。依此类推,数字控制器电路132可通过查找表等方式纪录所有电流源电路122A所对应的校正信号S1。如此,在一般模式下,当有电流源电路122A被启动时,数字控制器电路132可输出对应的校正信号S1,以控制DAC电路133输出补偿信号SP。

随着信号形式的不同,检测电路131亦可采用不同电路设置来判断上述式2是否成立。举例而言,当上述信号皆为电流信号时,检测电路131可由电流比较器以及切换电路实现。在一些实施例中,切换电路可用来对调信号AO1~AO2所对应的电流信号的传递路径,以利电流比较器获取足够信息来判断式2是否成立。

以下说明校正电路132A的操作。于一些实施例中,DAC电路133的位数为N,转换步阶(step)数为M,其中N小于等于M,而偏移量为OFFSET,即OFFSET=ΣILSB-IMSB。于此条件下,根据非二进制搜寻算法产生之调整信号SA(k)来补偿OFFSET,满足下式3:

其中,调整信号SA(k)为对应DAC电路133在输出端OP所输出电流的信号位准(如果对应到图2,其单位为1/16I),电流I

于一些实施例中,非二进制搜寻算法可设计以具有冗余(redundancy)范围q(k),其可用以容忍检测电路131在第k个转换步阶的决策错误。于一些实施例中,冗余范围q(k)符合下式4:

于一些实施例中,over range为相较于执行二进制制算法所超出的信号位准范围。

根据式3与式4,可进一步推得数值p(k)符合下式5:

于一些实施例中,校正电路132A可根据上述式3~5依序产生多个位d(k)。于一些实施例中,校正电路132A可由数字信号处理电路、一或多个逻辑电路与/或执行一有限状态机的处理电路等等方式实现,但本案并不以此为限。

图3为根据本案一些实施例绘制的一种非二进制搜寻算法的操作示意图。

在此例中,over range设定为0,总信号位准为16,N为4,M为5,且前3次转换步阶对应的冗余范围q(1)至q(3)分别设定为2、1、1。假设偏移量OFFSET对应于输出端OP的信号位准SOFFSET约为9,其中,偏移量OFFSET对应的信号位准SOFFSET使得IMSB+OFFSET=ΣILSB。在第1次步阶,调整信号SA(k)为8(根据式3,即2

接着,在第2次步阶,校正电路132A根据式3与式5改变调整信号SA,以调整信号SA(k)至5。信号位准S

于一些实施例中,位d(1)~d(5)可被编码为一多位准数字码,以控制DAC电路133产生所需的调整信号SA,但本案并不以此为限。

在一些实施例中,调整信号SA于输出端OP所对应的数字码Dout满足下式6:

D

其中

在本例中,N为4,M为5,上式6可展开为下式7:

其中D

于一些相关技术中,电流导向式DAC内的校正是透过二进制搜寻算法执行。在此些技术中,当电流导向式DAC内部的比较电路出现错误,将导致校正过程失败,并降低电流导向式DAC的转换准确率。此外,在部分应用中,为了降低出错,上述相关技术需执行多回比较,以提高校正准确度。如此,校正过程需耗费较多处理时间。

相较于上述技术,如先前所述,本案实施例的校正电路132A可容忍检测电路131出现的部分错误,故DAC装置100的整体准确率可被提升。另外,透过设定上述的冗余范围q(k),校正电路132A可容忍比较错误而不用进行多次比较,故可降低所需要的处理时间。

于一些实施例中,编译码器电路132B可转换多个位d(1)~d(5)为校正信号S1的多个位B1~BN。举例而言,编译码器电路132B可将非二进制的"01111"(即位d(1)~d(5))转换为二进制的"1001"(即位B1~BN)。

上述位数值与相关电路设定方式用于示例,其他各种位数值与电路设定方式皆为本案所涵盖的范围。

图4为根据一些实施例所绘示的一种校正方法400的流程图。于一些实施例中,校正方法400可由图1中的DAC装置100执行。

于操作S410,数字模拟转换器电路系统120根据输入信号SIN的最低有效位产生信号AO1,并根据输入信号SIN的最高有效位产生信号AO2。

于操作S420,响应于信号AO1与信号AO2的一比较结果执行非二进制搜寻算法以产生校正信号S1,以根据校正信号S1校正数字模拟转换器电路系统120。

上述各操作的说明可参照前述图1至图3的各实施例,故不重复赘述。上述校正方法400的多个步骤仅为示例,并非限于上述示例的顺序执行。在不违背本案的各实施例的操作方式与范围下,在校正方法400下的各种操作当可适当地增加、替换、省略或以不同顺序执行。

综上所述,本案实施例提供的DAC装置与校正方法可利用非二进制搜寻算法校正电流导向式DAC,以DAC装置的整体可靠度并节省校正需耗费的运作时间。

上述实施方式用于示例,在不脱离本案的精神和范围内,当可作各种更动与润饰,因此本案的保护范围当视后附的申请专利范围所界定者为准。

【符号说明】

100:数字模拟转换器装置

120:数字模拟转换器电路系统

DT:测试信号

SIN:输入信号

AO1、AO2:信号

MSB:最高有效位

RO1、RO2:电阻

132:数字控制器电路

SD:检测信号

S1:校正信号

B1~BN、B5:位

d(k):位

132B:编译码器电路

SA、SA(k):调整信号

133A:电流源电路

I:单位电流

S410、S420:操作

q(1)~q(3):冗余范围

L1~L4:位

S

110:多任务器电路系统

130:校正电路系统

DIN:数据信号

CAL、CAL’:模式控制信号

121、122:数字模拟转换器电路

133:数字模拟转换器电路

LSB:最低有效位

SOUT:模拟输出

OP、ON:输出端

131:检测电路

SP:补偿信号

SW1、SW2:开关

132A:校正电路

121A、122A:电流源电路

REF:参考信号

ILSB、IMSB:电流

400:校正方法

p(1)~p(5):数值

M1~M3:位

I

- 数字模拟转换器的校正电路及校正方法

- 数字模拟转换器装置与校正方法