基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法

文献发布时间:2023-06-19 09:58:59

技术领域

本发明涉及半导体衬底技术领域,尤其涉及一种基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法。

背景技术

随着大数据,云计算,物联网,5G通信和人工智能等领域的蓬勃发展,预计于2021年全球年数据流量增长达到复合年均增长率在25%以上,超过百万亿亿字节。这种爆炸式增长的流量需求使现有的数据通信领域面临着严峻的挑战。在这个大背景下,利用硅基光子集成电路在数据中心内部实现高速低功耗光互联将成为新一代通信领域的突破口。由于硅材料是间接带隙半导体材料,发光效率低,如何实现高效的硅基光源已成为了硅基光子集成电路的最主要瓶颈。现有最成熟的方法是采用异质外延和异质集成的方法将成熟的III-V族化合物光电器件集成到硅衬底上,从而实现高效的硅基光源。相对于异质集成,异质外延以更高的产能和更低的生产成本被认为是更加高效率的集成方法。

异质外延的技术难点在于III-V材料与硅材料的晶体属性不匹配。由于III-V族化合物材料与硅衬底存在晶格失配,在III-V外延生长到硅材料上时会产生高密度的穿透型位错,这些穿透型位错会形成大量的载流子的非辐射复合中心,并蔓延至硅基光源的有源层从而大幅度地减少器件发光效率和使用寿命。穿透型位错只有在贯穿整个晶体结构或是两个拥有相反柏氏矢量方向的穿透位错相遇时才会结束蔓延。现阶段对于实现低穿透型位错密度III-V族化合物材料基于硅衬底的分子束外延生长(Molecular Beam Epitaxy,MBE)主要依赖于超晶格位错过滤层。此方法需要高厚度的III-V缓冲层来容纳足够多的超晶格位错过滤层从而有效地降低穿透型位错密至<10

鉴于此,如何实现低厚度低穿透型位错密度的III-V族缓冲层将直接决定了高产能低成本的硅基光子集成电路成功是否成功的关键。

发明内容

本发明的目的是提供一种基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法,所述方法利用MBE设备在硅衬底上制备一层硅外延层,并结合砷化镓缓冲层来降低穿透位错,该方法能够有效降低异质外延时由于III-V族化合物和硅衬底晶格失配而导致的高密度穿透型位错,从而避免在后续生长中因使用过多层数超晶格位错过滤层而导致的微裂缝问题,提高了器件性能。

为解决上述技术问题,本发明提供一种基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法,所述方法包括以下步骤:

S1、将硅衬底送入MBE腔中,并利用MBE腔内高温去除硅衬底的表面氧化层;

S2、在去除表面氧化层的硅衬底上生长一层第一外延层并进行MBE腔内的第一次退火;

S3、通过步骤S2的第一次退火后进行砷化铟纳米点生长;

S4、通过步骤S3的砷化铟纳米点生长后再生长一层第二外延层,然后进行MBE腔内的第二次退火以在第二外延层中形成纳米空洞;

S5、通过步骤S4的第二次退火后进行砷化镓材料生长以形成一层砷化镓缓冲层,从而获得基于纳米空洞的低穿透位错密度硅基砷化镓衬底。

优选地,所述步骤S1具体实现方式为:将硅衬底送入温度为950℃-1200℃之间的MBE腔内并保持10-40min,进而去除硅衬底的表面氧化层。

优选地,所述步骤S2具体实现方式为:利用MBE腔与硅电子束蒸发技术在去除表面氧化层的硅衬底上生长一层厚度为50-100nm的第一外延层,然后维持MBE腔内温度处于900-1200℃之间并保持10-20min,完成MBE腔内的第一次退火。

优选地,所述第一外延层为硅外延层。

优选地,所述步骤S3具体实现方式为:将MBE腔内温度降至300-500℃之间并保持,然后进行砷化铟纳米点生长以得到砷化铟纳米点。

优选地,所述砷化铟纳米点的生长速率为0.1-0.3原子层每秒。

优选地,所述步骤S4具体实现方式为:将MBE腔内温度保持300-500℃之间并生长一层厚度为10-20nm的第二外延层,然后将MBE腔内温度升至700-750℃之间进行MBE腔内的第二次退火以在第二外延层里产生高密度的纳米空洞。

优选地,所述第二外延层的生长所采用材料为硅。

优选地,所述步骤S5具体实现方式为:将MBE腔内温度降至550-610℃之间,然后再进行砷化镓材料生长以生长一层厚度为200-500nm的砷化镓缓冲层,从而获得基于纳米空洞的低穿透位错密度硅基砷化镓衬底。

优选地,所述砷化镓缓冲层的生长速率为0.1-1.0原子层每秒。

与现有技术比较,本发明首先利用MBE设备在硅衬底上制备一层第一外延层后退火,然后在第一外延层上生长高质量砷化铟纳米点,并在砷化铟纳米点周边形成第二外延层屏障后再次退火以在第二外延层里产生高密度纳米空洞,最后结合砷化镓缓冲层来降低硅衬底的穿透位错密度,该方法能够有效避免后续生长过程中因使用过多层数超晶格位错过滤层而导致的微裂缝问题,从而提高硅基砷化镓衬底上器件性能。

附图说明

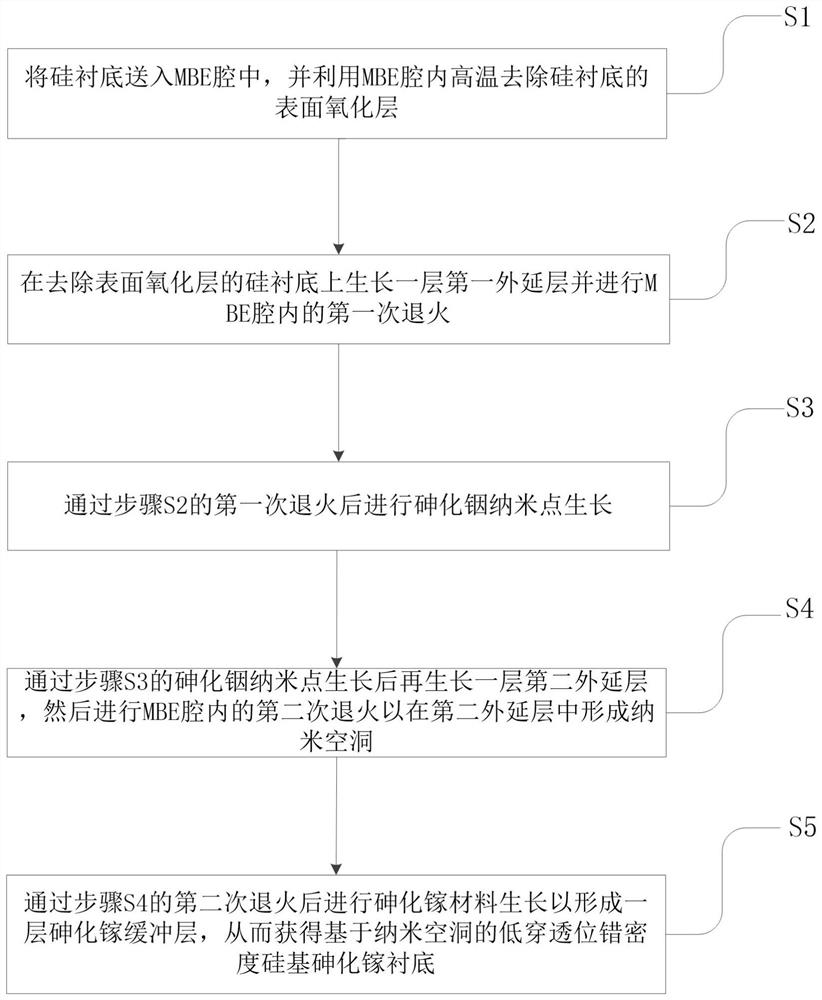

图1是本发明基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法的流程图,

图2是本发明中低穿透位错密度砷化镓硅衬底的结构图。

具体实施方式

为了使本技术领域的人员更好地理解本发明的技术方案,下面结合附图对本发明作进一步的详细说明。

图1示出了本发明提出的基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法流程图。

图2示出了本发明提出的中低穿透位错密度砷化镓硅衬底的结构图。如图2所示,包括,硅衬底1,第一外延层2,第二外延层3,砷化镓缓冲层4。

如图1~图2所示,一种基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法,所述方法包括以下步骤:

S1、将硅衬底1送入MBE(Molecular Beam Epitaxy,分子束外延)腔中,并利用MBE腔内高温去除硅衬底1的表面氧化层;

S2、在去除表面氧化层的硅衬底1上生长一层第一外延层2并进行MBE腔内的第一次退火;

S3、通过步骤S2的第一次退火后进行砷化铟纳米点生长以得到砷化铟纳米点;

S4、通过步骤S3的砷化铟纳米点生长后再生长一层第二外延层3,然后进行MBE腔内的第二次退火以在第二外延层3中形成纳米空洞;

S5、通过步骤S4的第二次退火后进行砷化镓材料生长以形成一层砷化镓缓冲层4,从而获得基于纳米空洞的低穿透位错密度硅基砷化镓衬底。

本实施例中,首先利用MBE设备在硅衬底1上制备一层第一外延层2,并在第一外延层2上生长砷化铟纳米点,然后在砷化铟纳米点周边形成一层第二外延层3屏障以在第二外延层3里产生高密度的纳米空洞,最后通过第二外延层3与砷化镓缓冲层4结合来降低硅衬底的穿透位错密度,能够有效避免后续砷化镓生长过程中因使用过多层数超晶格位错过滤层而导致的微裂缝问题,从而提高了硅基砷化镓衬底上器件的性能。

其中,所述步骤S1具体实现方式为:将硅衬底1送入温度为950℃-1200℃之间的MBE腔内并保持10-40min,进而去除硅衬底1的表面氧化层。

其中,所述步骤S2具体实现方式为:利用MBE腔与硅电子束蒸发技术在去除表面氧化层的硅衬底1上生长一层厚度为50-100nm的第一外延层2,然后维持MBE腔内温度处于900-1200℃之间并保持10-20min,完成MBE腔内的第一次退火。本实施例中,所述第一外延层2为硅外延层。

其中,所述步骤S3具体实现方式为:将MBE腔内温度降至300-500℃之间并保持,然后进行砷化铟纳米点生长以得到砷化铟纳米点。

其中,所述砷化铟纳米点的生长速率为0.1-0.3原子层每秒。

其中,所述步骤S4具体实现方式为:将MBE腔内温度保持300-500℃之间并生长一层厚度为10-20nm的第二外延层3,然后将MBE腔内温度升至700-750℃之间进行MBE腔内的第二次退火以在第二外延层3里产生高密度的纳米空洞。本实施例中,所述第二外延层3采用的材料为硅。由于第二外延层3里产生了高密度的纳米空洞,故第二外延层3表面所形成的穿透位错能够蔓延到高密度纳米空洞内并被终结。

其中,所述步骤S5具体实现方式为:将MBE腔内温度降至550-610℃之间,然后再进行砷化镓材料生长以生长一层厚度为200-500nm的砷化镓缓冲层4,从而获得基于纳米空洞的低穿透位错密度硅基砷化镓衬底。本实施例中,所述砷化镓缓冲层4的厚度还可以根据抛光的控制精度进行相应调整。

其中,所述砷化镓缓冲层4的生长速率为0.1-1.0原子层每秒。

以上对本发明所提供的一种基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法进行了详细介绍。本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对本发明进行若干改进和修饰,这些改进和修饰也落入本发明权利要求的保护范围内。

- 基于纳米空洞的低穿透位错密度硅基砷化镓层生长方法

- 利用低温防分解籽晶层在砷化镓衬底上生长氮化镓的方法