MOSFET门极串扰钳位电路、控制方法及控制器

文献发布时间:2023-06-19 10:40:10

技术领域

本发明涉及电控技术领域,尤其涉及一种MOSFET门极串扰钳位电路、控制方法及控制器。

背景技术

以半桥电路为例,在上桥IGBT(绝缘栅双极型晶体管,Insulated Gate BipolarTransistor)/MOSFET(金属氧化物半导体场效应晶体管,Metal-Oxide-SemiconductorField-Effect Transistor)开通的过程中,过高的dv/dt(电压变化率)会在下桥的IGBT/MOSFET米勒电容上产生一个位移电流,该位移电流通过驱动电阻流到地,造成门极电压抬升,如果抬升的电压大于IGBT/MOSFET的开通阈值,则会导致下桥IGBT/MOSFET开通数十或数百纳秒,造成额外的开关损耗,可能导致IGBT/MOSFET过热甚至损坏。

此外,由于IGBT/MOSFET封装工艺的问题,IGBT/MOSFET模块和单管IGBT/MOSFET器件在实际芯片的发射极和外部接线端子的发射极之间存在杂散电感,在IGBT/MOSFET开关过程中,一旦杂散电感上的电流发生变化,将会产生一个感应的电压,这个电压可能会叠加在IGBT/MOSFET的驱动电压上,导致IGBT/MOSFET的误开通。

为了减小上述的两种风险因素所造成的串扰电压的大小,常用的方案是在门极回路增加一个低阻抗的泄流通路。通常采用PNP三极管进行钳位控制,实测发现使用PNP三极管进行钳位时,在开通和关断时刻,均会在三极管BE之间形成反压,反压峰值较大,可能超过所选三极管规格书中给出的最大值,因此PNP三极管钳位方案存在风险。在开通过程的二极管反向恢复阶段,对于源极杂散电感较大的IGBT/MOSFET来说,PNP三极管导通可能导致杂散电感产生的正向串扰电压更大。另一方面,由于射极杂散电感的存在,实测的门极G和源极E(射极E)之间的电压并不是真实IGBT芯片的门极和射极的电压,所以采用门极电阻上的压降控制PNP开通的方式可能导致真实门极串扰较大的时候,PNP三极管无法打开。对于SiC MOSFET来说,其开关速度更快,串扰电压更加恶劣,此外由于SiC MOSFET的工艺问题,其负压耐受能力较弱,因此针对SiC串扰电压的抑制,不只要考虑正向的串扰电压,同时也要考虑负向串扰电压的抑制。

发明内容

本发明的主要目的在于提供一种MOSFET门极串扰钳位电路、控制方法及控制器,旨在解决抑制SiC MOSFET串扰电压的技术问题。

为实现上述目的,本发明提供了一种MOSFET门极串扰钳位电路,所述MOSFET门极串扰钳位电路包括:MOSFET驱动单元、抗扰单元及驱动芯片;其中,

所述MOSFET驱动单元的门极与所述驱动芯片的第一驱动端连接,所述抗扰单元的第一端与所述MOSFET驱动单元的门极连接,所述抗扰单元的第二端与所述驱动芯片的负压端或接地端连接;

所述抗扰单元,用于接收在MOSFET开关过程中引起的串扰电压;

所述驱动芯片,用于控制所述抗扰单元降低所述串扰电压。

优选地,所述抗扰单元包括并联相接于所述门极与所述驱动芯片的负压端之间的泄流单元和钳位单元,所述驱动芯片控制所述泄流单元的通断,所述钳位单元接收并抑制所述MOSFET驱动单元的感性串扰电压和容性串扰电压。

优选地,所述泄流单元包括第一二极管及MOS管,所述第一二极管的阳极和所述MOSFET驱动单元的门极连接,所述第一二极管的阴极和所述MOS管的漏极连接,所述MOS管的源极与所述驱动芯片的负压端连接,所述MOS管的门极与驱动芯片的第二驱动端连接。

优选地,所述钳位单元包括第一电阻和第二二极管,所述第一电阻的一端与所述MOSFET驱动单元的门极连接,所述第一电阻的另一端与所述第二二极管的阴极连接,所述第二二极管的阳极与所述驱动芯片的负压端连接。

优选地,所述抗扰单元包括并联相接于所述门极与所述驱动芯片的接地端之间的泄流单元和钳位单元,所述驱动芯片控制所述泄流单元的通断,所述钳位单元接收并抑制所述MOSFET驱动单元的感性串扰电压和容性串扰电压。

优选地,所述泄流单元包括第一二极管及MOS管,所述第一二极管的阳极和所述MOSFET驱动单元的门极连接,所述第一二极管的阴极和所述MOS管的漏极连接,所述MOS管的源极与所述驱动芯片的接地端连接,所述MOS管的门极与驱动芯片的第二驱动端连接。

优选地,所述钳位单元包括第一电阻和第二二极管,所述第一电阻的一端与所述MOSFET驱动单元的门极连接,所述第一电阻的另一端与所述第二二极管的阴极连接,所述第二二极管的阳极与所述驱动芯片的接地端连接。

此外,为实现上述目的,本发明还提出一种MOSFET门极串扰钳位电路控制方法,所述MOSFET门极串扰钳位电路控制方法基于如上所述的MOSFET门极串扰钳位电路,所述方法包括:

所述泄流单元接收所述MOSFET驱动单元的门极传输的感性串扰电压和容性串扰电压;

所述驱动芯片控制所述泄流单元降低所述容性串扰电压。

优选地,所述方法,还包括:所述钳位单元接收并抑制所述MOSFET驱动单元的感性串扰电压和容性串扰电压;

所述驱动芯片控制所述钳位单元抑制所述感性串扰电压和容性串扰电压。

此外,为实现上述目的,本发明还提出一种控制器,所述控制器包括如上文所述的MOSFET门极串扰钳位电路。

本发明提出一种MOSFET门极串扰钳位电路,所述电路包括:MOSFET驱动单元、抗扰单元及驱动芯片;其中,所述MOSFET驱动单元的门极与所述驱动芯片的第一驱动端连接,所述抗扰单元的第一端与所述MOSFET驱动单元的门极连接,所述抗扰单元的第二端与所述驱动芯片的负压端或接地端连接;所述抗扰单元,用于接收在MOSFET开关过程中引起的串扰电压;所述驱动芯片,用于控制所述抗扰单元降低所述串扰电压。所述MOSFET门极串扰钳位电路对MOSFET驱动单元的门极通过阻尼作用进行了隔离,同时对串扰电压进行了泄流。既能够抑制米勒电容造成的正向串扰电压的大小,又可以抑制射极杂散电感造成的正向串扰电压的大小。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

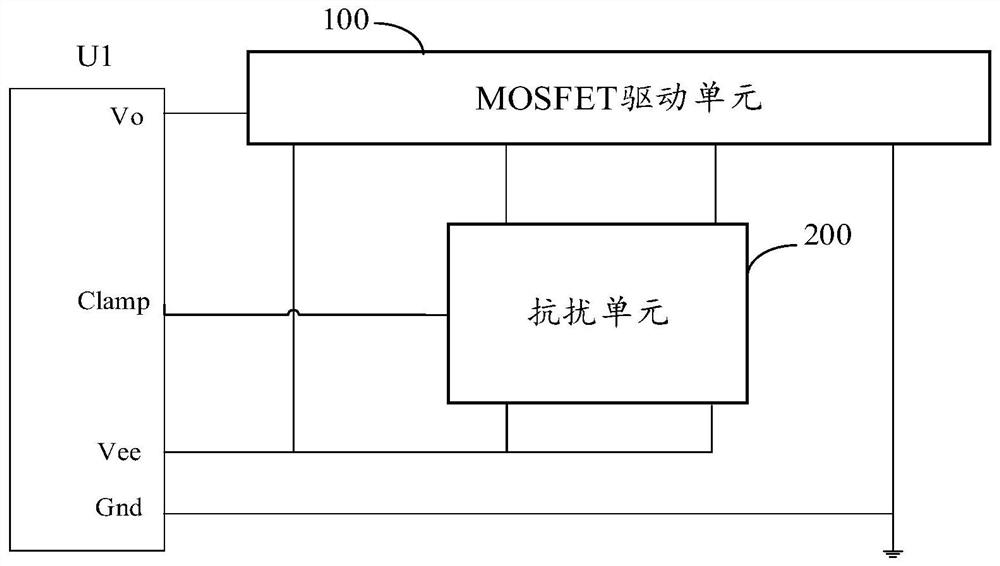

图1为本发明MOSFET门极串扰钳位电路一实施例的结构示意图;

图2为MOSFET开通过程第一电压变化图;

图3为本发明MOSFET门极串扰钳位电路一实施例的电路示意图;

图4为本发明MOSFET门极串扰钳位电路一实施例的另一电路示意图;

图5为MOSFET开通过程第二电压变化图;

图6为本发明MOSFET门极串扰钳位电路控制方法第一实施例的流程示意图。

附图标号说明:

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

本发明实施例提供了一种MOSFET门极串扰钳位电路,参考图1,图1为本发明MOSFET门极串扰钳位电路一实施例的结构示意图。

需要说明的是,本发明的MOSFET门极串扰钳位电路适用于上桥MOSFET或者下桥MOSFET,本实施例中以所述MOSFET门极串扰钳位电路设置在下桥为例进行说明。具体实施中,不限制所述MOSFET门极串扰钳位电路用在上桥或者下桥。

本发明MOSFET门极串扰钳位电路一实施例中,所述MOSFET门极串扰钳位电路包括:MOSFET驱动单元100、抗扰单元200及驱动芯片U1。

所述MOSFET驱动单元100的门极与所述驱动芯片U1的第一驱动端连接,所述抗扰单元200的第一端与所述MOSFET驱动单元100的门极连接,所述抗扰单元200的第二端与所述驱动芯片U1的负压端Vee或接地端Gnd连接,所述MOSFET驱动单元100的漏极与上桥MOSFET的源极(图中未示出上桥MOSFET,但并不影响本实施例的解释说明)连接,本发明实施例中的MOSFET驱动单元100相对于上桥MOSFET为下桥MOSFET。

易于理解的是,影响串扰电压大小的因素主要包括门极电阻,寄生电容,杂散电感的大小,但是门极内部电阻,寄生电容,源极杂散电感都是无法改变的。因此本发明实施例中设置了抗扰单元200。

参考图2,图2为MOSFET开通过程第一电压变化图,是现有技术中上桥MOSFET开通过程中的电流变化图,V

t1阶段:当上桥V

t2阶段:上桥MOSFET电流达到最大负载电流,下桥续流二极管电流I

所述抗扰单元200,用于接收在MOSFET开关过程中引起的串扰电压;所述驱动芯片U1,用于控制所述抗扰单元200降低所述串扰电压。

进一步地,参考图3,图3为本发明MOSFET门极串扰钳位电路一实施例的电路示意图,所述抗扰单元200包括并联相接于所述门极与所述驱动芯片U1的负压端Vee之间的泄流单元202和钳位单元201,所述驱动芯片U1控制所述泄流单元202的通断,所述钳位单元201接收并抑制所述MOSFET驱动单元100的感性串扰电压和容性串扰电压。

易于理解的是,在上桥MOSFET开通过程中,在t1-2阶段主要是源极杂散电感导致的上正下负的感性串扰电压,泄流单元202导通,MOSFET驱动单元门极等效电阻减小,RC时间常数减小,感性串扰电压迅速达到最小负值。降低后的串扰电压小于所述MOSFET驱动单元的门极开通阈值。

所述源极杂感电感导致上正下负的感性串扰电压。此时所述泄流单元202导通,接收所述驱动芯片U1从负压端Vee输入的驱动电压。

本实施例中,所述泄流单元202的一端连接到钳位电压端Clamp,钳位电压端Clamp可以接收外部clamp信号,当MOS处于关断的状态,clamp信号就会触发钳位MOS开通,具体地:以上桥MOSFET开通为例,此时下桥MOSFET是关断状态,clamp信号会控制钳位MOS导通,所以在t1阶段,钳位MOS是打开的,会让门极电压负向增大,有助于抑制正向串扰,而如果采用PNP三极管钳位,在t1阶段是无法导通的,只能抑制容性串扰。

需要说明的是,t3阶段,源极感应电压反向,泄流单元202关断,所述钳位单元201导通,所述钳位单元201中包含电阻,通过电阻的阻尼作用,导致反向充电回路RC时间常数增大,充电速度变慢,感性串扰电压仍为负值,且较小,因此总的串扰电压降低。

易于理解的是,在上桥MOSFET开通过程中t2阶段,米勒电流造成的容性串扰电压正向增大,所述泄流单元202为提供了一个低阻抗的泄流通路,通过所述泄流通路将容性串扰电压泄流。开通过程中,源极感应电压反向时,所述泄流单元202关断,停止泄流。

本发明通过上述电路,所述MOSFET门极串扰钳位电路对MOSFET驱动单元的门极通过阻尼作用进行了隔离,同时对串扰电压进行了泄流。既能够抑制米勒电容造成的正向串扰电压的大小,又可以抑制源极杂散电感造成的正向串扰电压的大小。

基于本发明MOSFET门极串扰钳位电路一实施例,提出本发明MOSFET门极串扰钳位电路第二实施例,参考图3、图4,图3为本发明MOSFET门极串扰钳位电路一实施例的电路示意图,图4为本发明MOSFET门极串扰钳位电路一实施例的另一电路示意图。

需要说明的是,所述驱动芯片U1包括电源输出端Vo、钳位电压端Clamp、负压端Vee、接地Gnd,本实施例中对所述驱动芯片U1的类别不做限制,所述驱动芯片U1能执行的功能包括但不限于输出电压、输出钳位信号、输出负压供电及接地。

具体实施中,负压端Vee输出驱动负电压是负压关断方案,当采用零伏关断方案时,可以将负压端Vee和接地Gnd接到一起。

所述MOSFET驱动单元100包括三极管Q2和第一门极电阻Rg及MOSFET子单元101;其中,所述三极管Q2的门极与电源电压端Vo连接,所述三极管Q2的集电极与所述驱动芯片U1的负压端Vee(参考图3)或者接地端Gnd(参考图4)连接,所述三极管Q2发射极与所述第一门极电阻Rg的一端连接,所述第一门极电阻Rg的另一端与所述泄流单元202的一端连接。

本实施例中,为方便解释说明,基于图3进行说明。所述MOSFET子单元101的驱动端(参考图3中,第二门极电阻Rint的第一端)与所述钳位单元201的一端连接,所述MOSFET子单元101的一端接地。所述MOSFET子单元101包括:第二门极电阻Rint、第一至第二电容C1~C2、源极杂感电感L、二极管与三极管。第二门极电阻Rint的第一端与所述第一门极电阻Rg的第二端连接,所述第二门极电阻Rint的第二端与所述三极管的门极连接,所述第一电容C1的第一端与所述三极管的门极连接,所述第一电容C1的第二端与所述三极管的集电极连接,所述三极管的集电极还和另一半桥的MOSFET单元连接,所述第二电容C2的第一端与所述三极管的门极连接,所述第二电容C2的第二端与所述三极管的发射极连接,所述三极管的发射极与所述源极杂感电感L的第一端连接,所述源极杂感电感L的第二端接地,所述二极管的阳极与所述三极管的集电极连接,所述二极管的阴极与所述三极管的集电极连接。具体实施中MOSFET子单元101也可能由其他器件构成,本实施例对此不加以限制。

所述钳位单元201包括第一电阻R1及第二二极管D2。所述第一电阻R1的第一端和所述第二门极电阻Rint的第一端连接,所述第一电阻R1的第二端和所述第二二极管D2的阴极连接,所述第二二极管D2的阳极和所述负压端Vee连接。所述第二二极管D2,用于在所述MOSFET驱动单元100的门极开通时导通,接收所述驱动芯片U1输入的驱动负电压。所述第一电阻R1,用于对所述驱动负电压进行阻尼,以获取阻尼驱动电压,并将所述阻尼驱动电压输出至所述MOSFET驱动单元100的第二门极电阻Rint。

易于理解的是,在开通时,第二二极管D2导通,同时第一电阻R1起到一定的阻尼作用,导致反向充电回路RC时间常数增大,充电速度变慢,感性串扰电压仍为负值,且较小,因此总的串扰电压降低。

所述泄流单元202包括第一二极管D1及MOS管Q1,所述第一二极管D1的阳极和所述第二门极电阻Rint的第一端连接,所述第一二极管D1的阳极和所述第一门极电阻Rg的第二端连接,所述第一二极管D1的阴极和所述MOS管Q1的漏极连接,所述MOS管Q1的源极和所述负压端Vee连接,所述MOS管Q1的门极和钳位电压端Clamp连接。

所述第一二极管D1及所述MOS管Q1,用于在所述MOSFET驱动单元100的门极开通时导通,接收所述MOSFET驱动单元100的门极输出的容性串扰电压,并对所述容性串扰电压进行泄流。

需要说明的是,开通过程中,米勒电流造成的容性串扰电压正向增大,第一二极管D1正向导通,通过MOS管Q1提供一个低阻抗的泄流通路,因此正向容性串扰电压减小。

易于理解的是,所述驱动芯片U1的钳位电压端Clamp输出钳位电压信号控制所述MOS管Q1的开通与关断。MOSFET驱动单元100的门极的开通过程中,所述驱动芯片U1输出钳位电压信号控制所述MOS管Q1开通。

需要说明的是,开通过程中,源极感应电压反向时,第一二极管D1关断,停止泄流。

本发明通过上述电路,所述MOSFET门极串扰钳位电路对MOSFET驱动单元的门极通过阻尼作用进行了隔离,同时对串扰电压进行了泄流。既能够抑制米勒电容造成的正向串扰电压的大小,又可以抑制源极杂散电感造成的正向串扰电压的大小。

基于本发明MOSFET门极串扰钳位电路第二实施例,提出本发明MOSFET门极串扰钳位电路第三实施例,参考图2,图2为本发明MOSFET门极串扰钳位电路一实施例的电路示意图。参考图4,图4为MOSFET开通过程第二电压变化图,是现有技术中上桥MOSFET开通过程中的电流变化图,基于第一实施例,不再对标号一一赘述。

需要说明的是,t7阶段:上桥V

所述钳位单元201,还用于在上桥MOSFET关断时截止,并将所述MOSFET驱动单元100的门极电压钳位在预设驱动负压。

需要说明的是,关断过程,在t7阶段,米勒电流的变化会导致门极串扰电压负向增长,可能会超过下桥MOSFET的门极耐压,通过所述钳位单元201将门极直接钳位到驱动负压,防止串扰负压超过负压极限,调节负压的钳位效果。

第二二极管D2,还用于在上桥MOSFET关断时截止,并将所述MOSFET驱动单元100的门极电压钳位在预设驱动负压。

需要说明的是,关断过程中,米勒电流的变化会导致门极串扰电压负向增长,可能会超过MOSFET的门极耐压,通过第二二极管D2将门极电压直接钳位到驱动负压,防止串扰负压超过负压极限,其中第二电阻R2用于调节负压的钳位效果。

本发明实施例通过上述电路既可以有效的抑制开通期间的正向串扰电压的大小,又可以抑制关断期间负向串扰电压的大小。开通期间的串扰电压包括米勒电容造成的正向串扰电压和源极杂散电感引起的正向串扰电压的大小。

此外,为实现上述目的,本发明实施例还提出一种MOSFET门极串扰钳位电路控制方法。参考图5,图5为本发明MOSFET门极串扰钳位电路控制方法第一实施例的流程示意图;参考图1,所述MOSFET门极串扰钳位电路控制方法基于如上文所述的MOSFET门极串扰钳位电路,所述方法包括:

步骤S10:所述泄流单元接收所述MOSFET驱动单元的门极传输的感性串扰电压和容性串扰电压;

易于理解的是,影响串扰电压大小的因素主要包括门极电阻(参考图2中第一门极电阻Rg、第二门极电阻Rint),寄生电容(参考图2中第一至第二电容C1~C2),杂散电感(参考图2中源极杂感电感L)的大小,但是门极内部电阻,寄生电容,射极杂散电感都是无法改变的。在对门极串扰进行抑制前,首先对门极处于何种状态进行判断,以确定采用何种方式进行抑制。

步骤S20:所述驱动芯片控制所述泄流单元降低所述容性串扰电压。

易于理解的是,在上桥MOSFET开通过程中,所述源极杂感电感L导致上正下负的感性串扰电压。此时所述钳位单元201导通,接收所述驱动芯片U1从负压端Vee输入的驱动电压。

易于理解的是,下桥MOSFET的漏极和上桥MOSFET的源极连接,在上桥MOSFET开通时,源极的电压发生改变,可以根据源极电压的改变判断上桥MOSFET是否开通。

易于理解的是,在上桥MOSFET开通过程中,在t1-2阶段主要是源极杂散电感导致的上正下负的感性串扰电压,泄流单元202导通,MOSFET驱动单元门极等效电阻减小,RC时间常数减小,感性串扰电压迅速达到最小负值。

所述源极杂感电感导致上正下负的感性串扰电压。此时所述泄流单元202导通,接收所述驱动芯片U1从负压端Vee输入的驱动电压。

进一步地,步骤S10具体包括:所述钳位单元接收并抑制所述MOSFET驱动单元的感性串扰电压和容性串扰电压。

所述步骤S20具体包括:所述驱动芯片控制所述钳位单元抑制所述感性串扰电压和容性串扰电压。

本实施例中,所述泄流单元的一端连接到钳位电压端Clamp,钳位电压端Clamp可以接收外部clamp信号,当MOS处于关断的状态,clamp信号就会触发钳位MOS开通,具体地:以上桥MOSFET开通为例,此时下桥MOSFET是关断状态,clamp信号会控制钳位MOS导通,所以在t1阶段,钳位MOS是打开的,会让门极电压负向增大,有助于抑制正向串扰,而如果采用PNP三极管钳位,在t1阶段是无法导通的,只能抑制容性串扰。

所述钳位单元201包括第一电阻R1及第二二极管D2。所述第一电阻R1的第一端和所述第二门极电阻Rint的第一端连接,所述第一电阻R1的第二端和所述第二二极管D2的阴极连接,所述第二二极管D2的阳极和所述负压端Vee连接。所述第二二极管D2,用于在所述MOSFET驱动单元100的门极开通时导通,接收所述驱动芯片U1输入的驱动负电压。所述第一电阻R1,用于对所述驱动负电压进行阻尼,以获取阻尼驱动电压,并将所述阻尼驱动电压输出至所述MOSFET驱动单元100的第二门极电阻Rint。

易于理解的是,在开通时,第二二极管D2导通,同时第一电阻R1起到一定的阻尼作用,导致反向充电回路RC时间常数增大,充电速度变慢,感性串扰电压仍为负值,且较小,因此总的串扰电压降低。

所述泄流单元202包括第一二极管D1及MOS管Q1,所述第一二极管D1的阳极和所述第二门极电阻Rint的第一端连接,所述第一二极管D1的阳极和所述第一门极电阻Rg的第二端连接,所述第一二极管D1的阴极和所述MOS管Q1的漏极连接,所述MOS管Q1的源极和所述负压端Vee连接,所述MOS管Q1的门极和钳位电压端Clamp连接。

需要说明的是,t3阶段,源极感应电压反向,泄流单元202关断,所述钳位单元201导通,所述钳位单元201中包含电阻,通过电阻的阻尼作用,导致反向充电回路RC时间常数增大,充电速度变慢,感性串扰电压仍为负值,且较小,因此总的串扰电压降低。

易于理解的是,在上桥MOSFET开通过程中t2阶段,米勒电流造成的容性串扰电压正向增大,所述泄流单元202为提供了一个低阻抗的泄流通路,通过所述泄流通路将容性串扰电压泄流。开通过程中,源极感应电压反向时,所述泄流单元202关断,停止泄流。

本发明通过上述方法,所述MOSFET门极串扰钳位电路对MOSFET驱动单元的门极通过阻尼作用进行了隔离,同时对串扰电压进行了泄流。既能够抑制米勒电容造成的正向串扰电压的大小,又可以抑制源极杂散电感造成的正向串扰电压的大小。

进一步地,关断过程,在t7阶段,米勒电流的变化会导致门极串扰电压负向增长,可能会超过下桥MOSFET的门极耐压,通过所述钳位单元201将门极直接钳位到驱动负压,防止串扰负压超过负压极限,调节负压的钳位效果。

第二二极管D2,还用于在上桥MOSFET关断时截止,并将所述MOSFET驱动单元100的门极电压钳位在预设驱动负压。

需要说明的是,关断过程中,米勒电流的变化会导致门极串扰电压负向增长,可能会超过MOSFET的门极耐压,通过第二二极管D2将门极电压直接钳位到驱动负压,防止串扰负压超过负压极限,其中第二电阻R2用于调节负压的钳位效果。

本发明实施例通过上述方法既可以有效的抑制开通期间的正向串扰电压的大小,又可以抑制关断期间负向串扰电压的大小。开通期间的串扰电压包括米勒电容造成的正向串扰电压和源极杂散电感引起的正向串扰电压的大小。

此外,本发明实施例还提出一种控制器,所述控制器包括如上文所述的MOSFET门极串扰钳位电路。

由于本控制器采用了上述所有实施例的全部技术方案,因此至少具有上述实施例的技术方案所带来的所有有益效果,在此不再一一赘述。

应当理解的是,以上仅为举例说明,对本发明的技术方案并不构成任何限定,在具体应用中,本领域的技术人员可以根据需要进行设置,本发明对此不做限制。

需要说明的是,以上所描述的工作流程仅仅是示意性的,并不对本发明的保护范围构成限定,在实际应用中,本领域的技术人员可以根据实际的需要选择其中的部分或者全部来实现本实施例方案的目的,此处不做限制。

另外,未在本实施例中详尽描述的技术细节,可参见本发明任意实施例所提供的MOSFET门极串扰钳位电路,此处不再赘述。

此外,需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者系统不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者系统所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括该要素的过程、方法、物品或者系统中还存在另外的相同要素。

上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如只读存储器(Read Only Memory,ROM)/RAM、磁碟、光盘)中,包括若干指令用以使得一台终端00设备(可以是手机,计算机,服务器,或者网络00设备等)执行本发明各个实施例所述的方法。

以上仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- MOSFET门极串扰钳位电路、控制方法及控制器

- MOSFET门极串扰钳位电路及控制器