一种基于恢复机制的消盲PFD电路

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及FPGA设计领域,主要涉及一种基于恢复机制的消盲PFD电路,属于基本电子电路的技术领域。

背景技术

锁相环是一种基于负反馈原理的闭环控制系统,其发展主要经历了三代。第一代是模拟锁相环,结构全部由模拟电路实现。第二代是模数混合锁相环,即,数字锁相环,其鉴相器由数字电路实现,其余结构由模拟电路实现。第三代是全数字锁相环,结构全部由数字电路实现。目前在锁相环领域,全数字锁相环由于具有成本低、面积小、速度快等优势,成为了近年来的常用结构。

双D触发器型鉴频鉴相器(PFD,Phase Frequency Detector)是一种常用于锁相环的线性鉴相器。然而传统的双D触发器型PFD存在非理想效应,其中一种为死区问题。传统的双D触发器型PFD的死区问题可通过增加复位延迟的方法解决。但是,双D触发器型PFD除了死区问题,还存在盲区问题。盲区问题是PFD的另一种非理想效应,当PFD比较的两个时钟信号的相位差接近±2π时,PFD检测出的相位差容易发生极性翻转的情况,会影响锁相环的锁定速度。

锁相环的实现方式包含ASIC和FPGA电路,其中,ASIC可实现模数混合锁相环和全数字锁相环,但FPGA只能实现全数字锁相环。授权公告号为CN101388666B的发明专利公开的鉴频鉴相器通过减小线性鉴相范围消除了鉴相盲区,但该鉴频鉴相器结构适用于模数混合锁相环,无法在FPGA实现。公开号为CN102291127A的发明专利和授权公告号为CN107302356B的发明专利公开的鉴频鉴相器通过调节复位延时来减小盲区,但都是基于晶体管级进行结构设计的,无法在FPGA实现。公开号为CN110365329A的发明专利公开的鉴频鉴相器通过增加记忆电路消除了鉴相盲区,但其结构也是基于晶体管级设计的,无法在FPGA实现。公开号为CN109639268A的发明专利公开的鉴频鉴相器在相位差在π到2π时抑制复位信号产生,从而消除盲区,其结构基于晶体管级设计,仍无法在FPGA实现。

目前,所有适用于全数字锁相环的PFD报道都是基于晶体管级进行设计,尚未有关于基于FPGA的改进双D触发器型PFD结构来解决盲区问题的报道。

发明内容

本发明的发明目的是针对上述背景技术的不足,提供一种基于恢复机制的消盲PFD电路,实现基于RTL级设计PFD电路恢复机制的发明目的,解决如何在FPGA上实现适用于全数字锁相环的消盲PFD的技术问题。

本发明为实现上述目的采用如下技术方案:

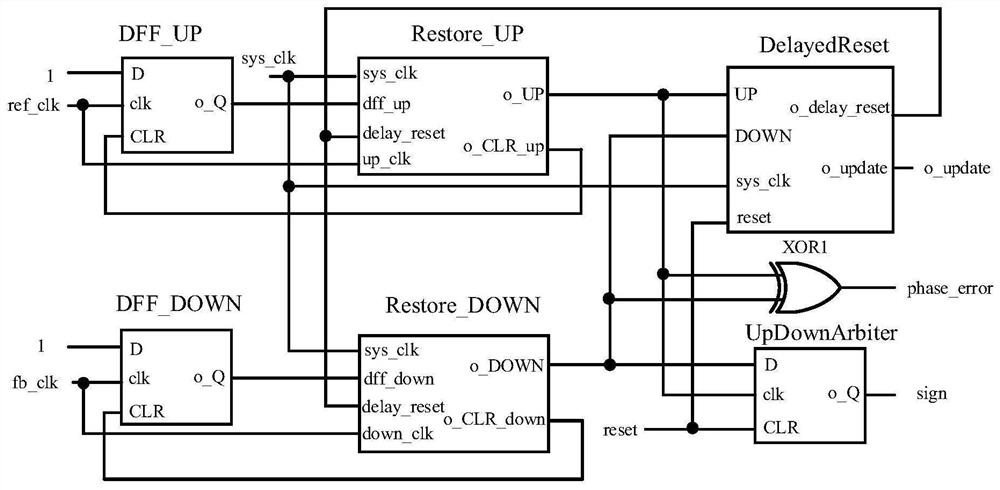

一种基于恢复机制的消盲PFD电路,电路包括DFF_UP模块、DFF_DOWN模块、UpDownArbiter模块、DelayedReset模块、Restore_UP模块、Restore_DOWN模块和二输入异或门。

DFF_UP模块包括一个异步复位的D触发器;DFF_UP模块的D输入端用于输入逻辑1信号,DFF_UP模块的clk输入端用于输入外界参考时钟信号ref_clk,DFF_UP模块的CLR输入端与所述Restore_UP模块的o_CLR_up输出端相连,DFF_UP模块的o_Q输出端与Restore_UP模块的dff_up输入端相连。

DFF_DOWN模块的结构和DFF_UP模块相同,包括一个异步复位的D触发器;DFF_DOWN模块的D输入端用于输入逻辑1信号,DFF_DOWN模块的clk输入端用于输入外界反馈时钟信号fb_clk,DFF_DOWN模块的CLR输入端与所述Restore_DOWN模块的o_CLR_down输出端相连,DFF_DOWN模块的o_Q输出端与所述Restore_DOWN模块的dff_down输入端相连。

UpDownArbiter模块包括一个D触发器;UpDownArbiter模块的D输入端与Restore_DOWN模块的o_DOWN输出端相连,UpDownArbiter模块的clk输入端与Restore_UP模块的o_UP输出端相连,UpDownArbiter模块的CLR输入端用于输入外界复位信号reset,UpDownArbiter模块的o_Q输出端用于输出符号位信号sign。

DelayedReset模块包括两个D触发器和若干逻辑门;DelayedReset模块的UP输入端与所述Restore_UP模块的o_UP输出端相连,DelayedReset模块的DOWN输入端与Restore_DOWN模块的o_DOWN输出端相连,DelayedReset模块的sys_clk输入端用于输入外界系统时钟信号,DelayedReset模块的reset输入端用于输入外界复位信号reset,DelayedReset模块的o_delay_reset输出端与Restore_UP模块的delay_reset输入端、Restore_DOWN模块的delay_reset输入端相连,DelayedReset模块的o_update输出端用于将鉴相更新信号o_update输出。

Restore_UP模块包括若干逻辑门和D触发器;Restore_UP模块的sys_clk输入端用于输入外界系统时钟信号sys_clk,Restore_UP模块的dff_up输入端与所述DFF_UP模块的o_Q输出端相连,Restore_UP模块的delay_reset输入端与DelayedReset模块的o_delay_reset输出端相连,Restore_UP模块的up_clk输入端用于输入外界参考时钟信号ref_clk,Restore_UP模块的o_UP输出端与DelayedReset模块的UP输入端相连,Restore_UP模块的o_CLR_up输出端与DFF_UP模块的CLR输入端相连。

Restore_DOWN模块的结构与Restore_UP模块相同,包括若干逻辑门和D触发器;Restore_DOWN模块的sys_clk输入端用于输入外界系统时钟信号sys_clk,Restore_DOWN模块的dff_down输入端与DFF_DOWN模块的o_Q输出端相连,Restore_DOWN模块的delay_reset输入端与DelayedReset模块的o_delay_reset输出端相连,Restore_DOWN模块的down_clk输入端用于输入外界参考时钟信号,Restore_DOWN模块的o_DOWN输出端与DelayedReset模块的DOWN输入端相连,Restore_DOWN模块的o_CLR_down输出端与DFF_DOWN模块的CLR输入端相连。

二输入异或门的第一输入端与Restore_UP模块的o_UP输出端相连,第二输入端与Restore_DOWN模块的o_DOWN输出端相连,输出端用于输出相位差信号phase_error。

本发明采用上述技术方案,具有以下有益效果:

(1)本发明提出了一种基于恢复机制的消盲PFD电路,该电路在传统的双D触发器型PFD结构基础上,通过门极电路产生的外界参考时钟信号上升沿使能信号、外界参考时钟信号上升沿检测模块恢复信号增加了恢复机制,抑制外界参考时钟信号的上升沿检测模块复位清零信号变为高电平,恢复被外界参考时钟信号上升沿检测模块的复位清零信号拉低的外界参考时钟信号上升沿恢复信号,有效解决PFD的盲区问题。

(2)该PFD电路结构基于RTL级进行设计,可在FPGA实现,用于全数字锁相环中。

附图说明

图1为本发明消盲PFD电路的整体结构图。

图2为本发明DelayedReset模块的结构图。

图3(a)为本发明o_CLR_UP信号产生电路的结构图,图3(b)为本发明o_UP信号产生电路的结构图,图3(c)为本发明pos_up_en信号产生电路的结构图,图3(d)为本发明restore_up信号产生电路的结构图,图3(e)为本发明Restore_UP模块的整体电路结构图。

图4为本发明pos_up_en信号工作时的PFD时序图。

图5为本发明restore_up信号工作时的PFD时序图。

图中标号说明:XOR1为异或门,AND1~AND7为第一至第七与门,OR1~OR7为第一至第七或门,NOT1~NOT5为第一至第五反相器,DFF1~DFF8为第一至第八D触发器,MUX1为二选一数据选择器。

具体实施方式

下面结合附图对本发明作更进一步的说明。

如图1所示,本发明公开的一种基于恢复机制的消盲PFD电路,主要由DFF_UP模块、DFF_DOWN模块、UpDownArbiter模块、DelayedReset模块、Restore_UP模块和Restore_DOWN模块这六个模块组成。DFF_UP模块,即UP 触发器模块,用于检测外界参考时钟信号ref_clk的上升沿; DFF_DOWN模块,即DOWN触发器模块,用于检测外界反馈时钟信号fb_clk的上升沿;Restore_UP模块用于恢复DFF_UP模块检测的ref_clk上升沿信号;Restore_DOWN模块用于恢复DFF_DOWN模块检测的fb_clk上升沿信号;DelayedReset模块用于复位Restore_UP模块和Restore_DOWN模块;UpDownArbiter模块用于比较恢复后的ref_clk上升沿信号和fb_clk上升沿信号得到表示鉴相结果的符号位信号sign。

如图1所示,DFF_UP模块包括一个异步复位的D触发器:DFF_UP模块的D输入端用于输入逻辑信号1,DFF_UP模块的clk输入端用于输入外界参考时钟信号ref_clk,DFF_UP模块的CLR输入端与Restore_UP模块的o_CLR_up输出端相连,DFF_UP模块的o_Q输出端与Restore_UP模块的dff_up输入端相连。

如图1所示,DFF_DOWN模块与DFF_UP模块的结构相同,包括一个异步复位的D触发器:DFF_DOWN模块的D输入端用于输入逻辑信号1,DFF_DOWN模块的clk输入端用于输入外界反馈时钟信号fb_clk,DFF_DOWN模块的CLR输入端与Restore_DOWN模块的o_CLR_down输出端相连,DFF_DOWN模块的o_Q输出端与Restore_DOWN模块的dff_down输入端相连。

UpDownArbiter模块为包括一个D触发器的仲裁模块:UpDownArbiter模块的D输入端与Restore_DOWN模块的o_DOWN输出端相连, UpDownArbiter模块的clk输入端与Restore_UP模块的o_UP输出端相连,UpDownArbiter模块的CLR输入端用于输入外界复位信号reset,UpDownArbiter模块的o_Q输出端用于输出符号位信号sign。此时,输入端信号已解决了盲区问题,不会导致符号位信号sign错误翻转。当o_DOWN信号的上升沿超前于o_UP信号的上升沿时,符号位sign为1,表示反馈信号fb_clk相位超前于参考信号ref_clk相位。当o_DOWN信号的上升沿落后于o_UP信号的上升沿时,符号位sign为0,表示反馈信号fb_clk的相位落后于参考信号ref_clk的相位。

DelayedReset模块的结构如图2所示,包括两个D触发器和若干逻辑门。DelayedReset模块的UP输入端与Restore_UP模块的o_UP输出端相连,DelayedReset模块的DOWN输入端与Restore_DOWN模块的o_DOWN输出端相连,DelayedReset模块的sys_clk输入端用于输入外界系统时钟信号sys_clk,DelayedReset模块的reset输入端用于输入外界复位信号reset,DelayedReset模块的o_delay_reset输出端与Restore_UP模块的delay_reset输入端、Restore_DOWN模块的delay_reset输入端相连,DelayedReset模块的o_update输出端用于输出鉴相更新信号。第一与门AND1对输入的恢复后的外界参考时钟信号上升沿信号o_UP、恢复后的外界反馈时钟信号上升沿o_DOWN进行与运算,输出与运算结果至第一或门OR1的一个输入端;第一或门OR1的另一个输入端接收外界复位信号reset,输出或运算结果至第一D触发器DFF1的数据输入端;第一D触发器DFF1的Q输出端输出延时复位信号o_delay_reset;第二与门AND2对输入的恢复后的外界参考时钟信号上升沿信号o_UP、恢复后的外界反馈时钟信号上升沿o_DOWN进行与运算,输出与运算结果至第二D触发器DFF2的数据输入端,第一D触发器DFF1和第二D触发器DFF2的时钟信号端口接系统时钟信号sys_clk,第二D触发器DFF2的Q输出端输出PFD鉴相更新信号o_update;DelayedReset模块生成的延时复位信号o_delay_reset以及PFD鉴相更新信号o_update都与FPGA系统时钟sys_clk同步。当全局复位信号reset为高电平时,全局复位,此时延迟复位信号o_delay_reset信号为高电平,该信号输入到Restore_UP 和Restore_DOWN模块。当一次鉴相周期结束,鉴相更新信号o_update也需要变为高电平,鉴相更新信号o_update为全数字锁相环中其它模块采样相位差信号phase_error提供指示作用,如图1所示,相位差信号phase_error通过异或门XOR1对恢复后的外界参考时钟信号上升沿信号、恢复后的外界反馈时钟信号上升沿信号进行异或运算得到,异或门XOR1的两个输入端分别与Restore_UP模块的o_UP输出端、Restore_DOWN模块的o_DOWN输出端相连。

Restore_UP模块和Restore_DOWN模块通过恢复机制解决PFD中存在的盲区问题,两模块的结构相同,功能对称,只介绍Restore_UP模块。Restore_UP模块的整体结构如图3(e)所示。

Restore_UP模块的sys_clk输入端用于输入外界系统时钟信号sys_clk,Restore_UP模块的dff_up输入端与DFF_UP模块的o_Q输出端相连,Restore_UP模块的delay_reset输入端与DelayedReset模块的o_delay_reset输出端相连,Restore_UP模块的up_clk输入端用于输入外界参考时钟信号ref_clk,Restore_UP模块的o_UP输出端与DelayedReset模块的UP输入端相连,Restore_UP模块通过o_UP输出端输出恢复后的外界参考时钟信号上升沿信号至DelayedReset模块的UP输入端,Restore_UP模块的o_CLR_up输出端与DFF_UP模块的CLR输入端相连,Restore_UP模块通过o_CLR_up输出端输出UP触发器的复位清零信号。Restore_UP模块主要通过UP触发器上升沿使能信号pos_up_en和UP触发器恢复信号restore_up这两个内部逻辑信号来解决盲区问题。

Restore_UP模块通过图3(a)所示的门极电路生成UP触发器的复位清零信号o_CLR_up,具体包括第一反相器NOT1、第三与门AND3,第一反相器NOT1的输入端接UP触发器上升沿使能信号pos_up_en,输出反相后的pos_up_en值第三与门AND3的一个输入端,AND3的另一个输入端接DelayedReset模块输出的延时复位信号o_delay_reset,第三与门AND3输出UP触发器的复位清零信号o_CLR_up。

Restore_UP模块通过图3(b)所示的门极电路生成恢复后的外界参考时钟信号上升沿信号o_UP,具体包括:第二或门OR2、第二反相器NOT2、第四与门AND4,第二或门OR2对输入的UP触发器恢复信号restore_up和外界参考时钟信号上升沿信号进行或运算,第二反相器NOT2的输入端接DelayedReset模块输出的延时复位信号o_delay_reset,第四与门AND4对第二或门OR2输出的或运算结果以及第二反相器NOT2输出的反相o_delay_reset进行与运算得到恢复后的外界参考时钟信号上升沿信号o_UP。

UP触发器上升沿使能信号pos_up_en用于抑制UP触发器复位信号o_CLR_up变为高电平,该信号的工作条件为up_clk信号相位超前于down_clk信号相位且鉴出的相位差接近-2π。图3(c)中的o _UP_d2信号由o _UP信号延迟2个系统时钟周期得到,用于判断本次鉴相过程中UP触发器是否先拉高。pos_up信号为up_clk信号的上升沿检测信号,pos_up_d信号用于拓展pos_up_en信号的宽度,使其大于一个系统时钟周期。当up_clk信号的下一次上升沿出现在延迟复位信号delay_reset拉高的上一个系统时钟周期内,且落后于down_clk信号的本次上升沿,此时pos_up_en信号拉高,抑制了Restore_UP模块输出的复位信号o_CLR_up变为高电平,此时delay_reset信号拉高周期内,UP触发器不会被复位,仍保持dff_up信号输出为高电平,Restore_UP输出的信号o_UP信号为高电平,符号位信号sign不发生翻转,解决了盲区问题。

UP触发器上升沿使能信号pos_up_en通过图3(c)所示的门极电路产生,具体包括:第三D触发器DFF3、第四D触发器DFF4、第五D触发器DFF5、第六D触发器DFF6、第五与门AND5、第六与门AND6、第三或门OR3;其中,第三D触发器DFF3的数据输入端接外界参考时钟信号ref_clk,时钟信号端接外界系统时钟信号sys_clk,输出与sys_clk同步的up_clk端口输入信号;第三反相器的输入端接第三D触发器的Q输出端,输出反相的up_clk端口输入信号;第六与门AND6对输入的外界参考时钟信号ref_clk以及反相的up_clk端口输入信号进行与运算,输出up_clk端口输入信号的上升沿检测信号pos_up;第六D触发器DFF6的数据输入端接第六与门AND6的输出端,时钟信号端接外界系统时钟信号sys_clk,对pos_up进行延迟处理,输出up_clk端口输入信号上升沿检测信号的延迟信号pos_up_d;第三或门对第六DFF6输出的pos_up_d以及第六与门AND6输出的pos_up进行或运算;第四D触发器DFF4的数据输入端接恢复后的外界参考时钟信号上升沿信号o_UP,时钟信号端接外界系统时钟信号sys_clk,输出延时1个系统时钟周期的恢复后的外界参考时钟信号上升沿信号o_UP_d1;第五D触发器DFF5的数据输入端接第四DFF4的Q输出端,时钟信号端接外界系统时钟信号sys_clk,输出延时2个系统时钟周期的恢复后的外界参考时钟信号上升沿信号o_UP_d2;第五与门AND5的两个输入端分别接第五D触发器DFF5的输出端以及第三或门OR3的输出端,输出UP触发器上升沿使能信号pos_up_en。

UP触发器恢复信号restore_up用于恢复被复位信号拉低的输出信号o_UP。如图3(d)所示,当pos_up信号为高电平,且delay_reset信号或delay_reset_d信号拉高,此时说明在up_clk信号相位超前于down_clk相位的情况下,延迟复位信号delay_reset拉高的系统时钟周期内有参考时钟信号up_clk的上升沿,UP触发器会丢失上升沿。因此restore_up信号在下一个系统时钟周期结束后拉高,此时UP触发器的输出信号dff_up虽然为0,但由于restore_up信号变为高电平,Restore_UP模块输出的信号o_UP得到恢复。下一次PFD鉴相周期,o_UP信号和o_DOWN信号送入UpDownArbiter模块比较输出的符号位信号sign也不会出现极性翻转的情况。

UP触发器恢复信号restore_up通过图3(d)所示的门极电路产生,具体包括:第四或门OR4、第五或门OR5、第六或门OR6、第七或门OR7、第四反相器NOT4、第七与门AND7、第七D触发器DFF7、二选一数据选择器MUX1;其中,第四或门OR4的两个输入端分别接delay_reset端口以及delay_reset_d端口,delay_reset_d端口输入的信号经图3(e)所示第八D触发器DFF8对DelayedReset模块输出的延时复位信号o_delay_reset延迟处理得到的;第四反相器NOT4的输入端接pos_up信号;第六或门OR6的输入端接delay_reset端口及第四反相器NOT4的输出端;第五反相器NOT5的输入端接第六或门OR6的输出端;第七与门AND7的两个输入端分别接第四或门OR4的输出端以及pos_up信号;第五或门OR5的两个输入端分别接第七AND7的输出端以及第五反相器NOT5的输出端;第七或门OR7的两个输入端分别接第七与门AND7的输出端以及第六或门OR6的输出端;二选一数据选择器MUX1的一个数据输入端接第七或门OR7的输出端,另一个数据输入端接第七D触发器DFF7的Q输出端,控制端接第七或门OR7的输出端;第七D触发器DFF7的数据输入端接二选一数据MUX1的输出端,时钟信号端接外界系统时钟信号sys_clk,输出UP触发器恢复信号restore_up。

pos_up_en信号工作时的PFD信号时序图如图4所示。根据图4介绍pos_up_en信号的工作原理。

图4中的t1时刻为fb_clk信号本次鉴相过程中的上升沿。ref_clk波形图t2时刻圆圈标注的为下一次鉴相过程中的上升沿,此时记为当前系统时钟周期。延迟复位信号delay_reset在t3时刻下一个系统时钟周期内拉高,当ref_clk信号和fb_clk信号在当前系统时钟周期内拉高且ref_clk信号的t2时刻上升沿滞后于fb_clk信号的t1时刻上升沿,pos_up_en信号变为高电平,抑制了下一个系统时钟周期o_CLR_UP信号变为高电平,从而抑制了UP触发器的复位清零,符号位sign信号不会发生翻转,PFD的盲区问题得到了解决。

restore_up信号工作时的PFD信号时序图如图5所示。根据图5介绍restore_up信号的工作原理。

图5中的t1时刻为fb_clk信号本次鉴相过程中的上升沿。t2时刻delay_reset信号为高电平,此时记为当前系统时钟周期。ref_clk波形图t3时刻圆圈标注的为下一次鉴相过程中的上升沿,在复位信号delay_reset为高电平的系统周期内,虽然UP触发器的输出dff_up信号复位后变为低电平,且复位信号影响到ref_clk的t3时刻下一次上升沿检测,但Restore_UP模块在下一个系统时钟周期内检测到了ref_clk的上升沿,在复位周期后的第二个系统时钟周期t4时刻拉高信号restore_up,恢复了Restore_UP模块输出的o_UP信号。在这段时间内,符号位信号sign一直为低电平,表示ref_clk信号相位一直超前fb_clk信号相位,未出现极性翻转的情况,丢失的上升沿信息得到了恢复,盲区问题得到了解决。

以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 一种基于恢复机制的消盲PFD电路

- 一种基于基站模型的导盲方法、导盲杖及导盲系统