芯片测试系统和测试方法

文献发布时间:2023-06-19 11:57:35

技术领域

本申请涉及测试技术领域,具体而言,涉及一种芯片测试系统和测试方法。

背景技术

随着集成电路的发展,芯片中FLASH(闪存)的结构越来越复杂,功能也越来越多样化。不仅芯片的一些重要参数需要存放在FLASH里,而且某些FLASH需要先进行内嵌自测试后才能正常使用。

目前,量产芯片的FLASH内嵌自测试在晶元级测试(wafer level test)中的芯片针测(Chip Probe,CP)阶段,或是在封装后测试(package level test)中的最后测试(Final Test,FT)阶段来进行。测试机台昂贵,测试成本高。

发明内容

本申请实施例的目的在于提供一种芯片测试系统和测试方法,不仅可以用于量产的芯片测试,也可以用于测试片的芯片测试。

本申请实施例第一方面提供了一种芯片测试系统,包括:上位机,用于基于配置信息生成测试指令;协议转换器,一端连接所述上位机,用于将所述上位机下发的测试指令转换为预设格式的测试命令;待测芯片,连接所述协议转换器的另一端,用于接收所述协议转换器发送的所述预设格式的测试命令,并执行所述预设格式的测试命令,获得对所述待测芯片的测试信息;其中,所述上位机生成对所述测试信息的读取指令,并由所述协议转换器将所述读取指令转换为所述预设格式的所述测试命令后发送给所述待测芯片,所述待测芯片执行所述读取指令,并将读取到的所述测试信息返回给所述上位机。

于一实施例中,所述上位机包括:指令生成器,用于根据配置信息生成测试指令。

于一实施例中,所述上位机还包括:接口模块,连接所述指令生成器,用于将所述测试指令发送给协议转换器,并通过所述协议转换器接收所述待测芯片返回的所述测试信息。

于一实施例中,所述上位机还包括:预期计算器,连接所述指令生成器,用于计算每条所述测试指令的期望值。

于一实施例中,所述上位机还包括:处理器,分别连接所述预期计算器和所述接口模块,用于将所述测试信息与所述期望值进行比对,并基于比对结果,生成所述待测芯片的测试结果信息。

于一实施例中,所述待测芯片包括:命令接收器,连接所述协议转换器,用于接收对所述待测芯片的所述测试命令。

于一实施例中,所述待测芯片包括:命令执行器,连接所述命令接收器,用于执行所述测试命令,并获得所述待测芯片的所述测试信息。

于一实施例中,所述待测芯片包括:模式检测器,连接所述命令执行器,用于检测所述待测芯片当前是否处于测试模式,并在所述待测芯片当前处于测试模式时,驱动所述命令执行器执行所述测试命令。

于一实施例中,所述待测芯片包括:存储器,连接所述命令执行器,用于存储所述待测芯片的测试信息。

本申请实施例第二方面提供了一种芯片测试方法,包括:接收测试请求,所述测试请求中携带有用于测试的配置信息;根据所述配置信息,生成测试指令;发送所述测试指令至待测芯片,并计算所述测试指令的期望值;接收所述待测芯片返回的测试信息;判断所述测试信息与所述期望值是否相同;若所述测试信息与所述期望值相同,发送下一条测试指令至所述待测芯片,否则,输出所述测试信息与所述期望值的比对结果信息。

本申请提供的芯片测试系统和测试方法,用户可以通过上位机配置测试参数,上位机根据用户的配置信息生成测试指令,并发送测试指令给协议转换器,协议转换器将测试指令转换为待测芯片可以识别的预设格式的测试命令,并将测试命令发送给待测芯片,然后待测芯片执行测试命令后得到测试信息,上位机还可以读取待测芯片的测试信息,进而完成对待测芯片的测试过程,不仅可以用于量产的芯片测试,也可以用于测试片的芯片测试,克服了现有技术中芯片测试的局限性。

附图说明

为了更清楚地说明本申请实施例的技术方案,下面将对本申请实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本申请的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

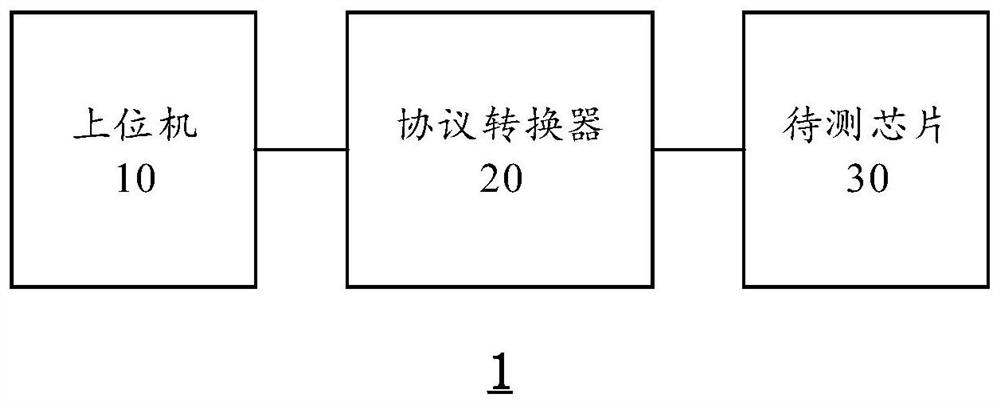

图1为本申请一实施例的芯片测试系统的结构示意图;

图2为本申请一实施例的芯片测试系统的结构示意图;

图3为本申请一实施例的芯片测试方法的流程示意图;

图4为本申请一实施例的芯片测试方法的流程示意图;

图5为本申请一实施例的芯片测试方法的流程示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行描述。在本申请的描述中,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

如图1所示,本实施例提供一种芯片测试系统1,包括:上位机10、协议转换器20和待测芯片30,其中:

上位机10,用于基于配置信息生成测试指令。上位机10可以是手机、平板电脑、笔记本电脑、台式计算机或者多个计算机组成的大型计算系统等设备。

协议转换器20,一端连接上位机10,用于将上位机10下发的测试指令转换为预设格式的测试命令。协议转换器20可以是芯片测试机台,比如可以是JTAG(Joint TestAction Group,联合测试工作组)设备。预设格式可以是待测芯片30能够识别的格式,比如待测芯片30可以识别的测试命令为JATG命令,则JTAG设备将上位机10传送过来的测试指令转换成JATG命令发送待测芯片30。

待测芯片30,连接协议转换器20的另一端,用于接收协议转换器20发送的预设格式的测试命令,并执行预设格式的测试命令,获得对待测芯片30的测试信息。待测芯片30可以是芯片生产过程中测试用的测试片,也可以是已经量产的芯片。

其中,上位机10生成对测试信息的读取指令,并由协议转换器20将读取指令转换为预设格式的测试命令后发送给待测芯片30,待测芯片30执行读取指令,并将读取到的测试信息返回给上位机10。如此实现对待测芯片30的自动测试过程。

上述芯片测试系统1,用户可以通过上位机10配置测试参数,上位机10根据用户的配置信息生成测试指令,并发送测试指令给协议转换器20,协议转换器20将测试指令转换为待测芯片30可以识别的预设格式的测试命令,并将测试命令发送给待测芯片30,然后待测芯片30执行测试命令后得到测试信息,上位机10还可以读取待测芯片30的测试信息,进而完成对待测芯片30的测试过程,不仅可以用于量产的芯片测试,也可以用于测试片的芯片测试,克服了现有技术中芯片测试的局限性。

如图2所示,本实施例提供一种芯片测试系统1,上位机10包括:指令生成器11,用于根据配置信息生成测试指令。指令生成器11也可以根据用户的配置信息限定测试指令的发送顺序。

于一实施例中,测试指令和指令的含义可以参见下表1:

表1测试指令及其含义

其中,TMRSET指令可以使FLASH进入测试模式,测试FLASH IP各种电特性(比如擦参考单元的电流、写微调编码时的参考电流和位单元电流等等),执行FLASH仅在测试模式下支持的一些指令。

用户可以根据自己的测试需求灵活组合表1中的指令,配置不同的参数,比如配置不同的擦写地址、写入数据等,以达到测试目的。

于一实施例中,上位机10还包括:接口模块12,连接指令生成器11,用于将测试指令发送给协议转换器20,并通过协议转换器20接收待测芯片30返回的测试信息。接口模块12可以嵌入接口逻辑,将测试指令通过接口模块12下发到协议转换器20,比如通过USB(Universal Serial Bus,通用串行总线)接口下发到JTAG设备。

于一实施例中,上位机10还包括:预期计算器13,连接指令生成器11,用于计算每条测试指令的期望值。在实际场景中,一个既定的待测芯片30,其对应的一些功能预先设置了期望值,比如电特性必须满足电特性的期望值,才算芯片合格。期望值可以由用户配置,也可以基于用户配置信息通过调用特定函数来自动计算得出。

于一实施例中,上位机10还包括:处理器14,分别连接预期计算器13和接口模块12,用于将测试信息与期望值进行比对,并基于比对结果,生成待测芯片30的测试结果信息,并可以发出提示信息,告知用户测试结论。

于一实施例中,待测芯片30中可以内嵌有用于测试的命令接收器31,该命令接收器31与协议转换器20连接,用于接收对待测芯片30的测试命令。

于一实施例中,待测芯片30中可以内嵌有用于测试的命令执行器32,命令执行器32连接命令接收器31,用于执行测试命令,并获得待测芯片30的测试信息。

于一实施例中,待测芯片30包括:模式检测器33,连接命令执行器32,用于检测待测芯片30当前是否处于测试模式,并在待测芯片30当前处于测试模式时,驱动命令执行器32执行测试命令。测试模式可以是内嵌自测试模式。

在实际场景中,芯片进入内嵌自测试模式可以有两种方式:

一、通过配置芯片外部的输入输出引脚,使芯片进入内嵌自测试模式。此时模式检测器33通过检测输入输出引脚的电平状态来判断芯片是否处于内嵌自测试模式。

二、通过I2C总线指令,驱动芯片进入内嵌自测试模式。

于一实施例中,待测芯片30包括:存储器34,连接命令执行器32,用于存储待测芯片30的测试信息,即保存测试命令相关的执行结果。存储器34可以由寄存器实现。

如图3所示,本实施例提供一种芯片测试方法,可用于上述图1或图2所示的芯片测试系统1中,该方法包括:

首先使芯片进入内嵌自测试模式,上位机10通过USB接口将测试指令按照一定顺序(比如用户配置的测试顺序)发送给JTAG设备,接着JTAG设备把测试指令转换成JTAG命令传送给待测芯片30。如果待测芯片30处于内嵌自测试模式,接收到JTAG命令后,待测芯片30会按照JTAG命令的要求执行相应的测试操作,并将测试操作的结果信息保存到寄存器中。上位机10发送读取结果指令,从待测芯片30获取测试操作的结果信息,并将其与预期结果进行比较。如果两者一致,上位机10会继续发送后续的测试指令,否则停止发送测试指令,并打印fail(错误),提示用户该芯片的FLASH有缺陷。

上述芯片测试方法,用户可以通过上位机10配置测试参数,上位机10根据用户的配置信息生成测试指令,并发送测试指令给协议转换器20,协议转换器20将测试指令转换为待测芯片30可以识别的预设格式的测试命令,并将测试命令发送给待测芯片30,然后待测芯片30执行测试命令后得到测试信息,上位机10还可以读取待测芯片30的测试信息,进而完成对待测芯片30的测试过程,不仅可以用于量产的芯片测试,也可以用于测试片的芯片测试。FLASH自测试不但可以筛选出FLASH功能正常的芯片,同时也可以将芯片的一些重要参数写入FLASH特定区域,以供芯片上电过程中加载。克服了现有技术中芯片测试的局限性。

如图4所示,本实施例提供一种芯片测试方法,可由上述图1或图2所示的上位机10来执行,该方法包括:

步骤401:接收测试请求,测试请求中携带有用于测试的配置信息。

步骤402:根据配置信息,生成测试指令。

步骤403:发送测试指令至待测芯片30,并计算测试指令的期望值。可以通过协议转换器20将测试指令下发至待测芯片30。

步骤404:接收待测芯片30返回的测试信息。可以通过协议转换器20将测试信息返回至上位机10。

步骤405:判断测试信息与期望值是否相同。若是,进入步骤406,否则进入步骤407。

步骤406:发送下一条测试指令至待测芯片30。

步骤407:输出测试信息与期望值的比对结果信息。

上述芯片测试方法的有益效果请结合上述实施例对图1至图3的详细描述。

如图5所示,本实施例提供一种芯片测试方法,可由上述图2所示的上位机10来执行,以共有N(N为大于零的有限自然数)条测试指令为例,该方法包括:

步骤501:指令产生器产生满足测试需求的测试指令序列,共N条指令。

步骤502:接口模块12发送第一条测试指令,N=N-1。

步骤503:预期计算器13计算出步骤502中接口模块12发送的第一条测试指令对应的预期返回值A(即期望值)。

步骤504:接口模块12接收待测芯片30针对第一条测试指令返回的测试信息数据B。

步骤505:处理器14比较A==B?,若是进入步骤506,否则,说明第一条测试指令的测试结果出错,可以发出提示信息。

步骤506:判断N==0?,若是,说明所有的N条测试指令全部完成测试,可以结束本次测试任务。否则,返回步骤502,进行下一条测试指令的发送过程。

上述芯片测试方法的有益效果请结合上述实施例对图1至图3的详细描述。

虽然结合附图描述了本发明的实施例,但是本领域技术人员可以在不脱离本发明的精神和范围的情况下作出各种修改和变型,这样的修改和变型均落入由所附权利要求所限定的范围之内。

- 芯片测试组件、芯片测试系统和芯片测试方法

- 芯片测试系统、测试方法、芯片的测试响应方法和芯片