一种抑制冲击电流的冗余电路及工作方法

文献发布时间:2023-06-19 09:27:35

技术领域

本发明涉及直流电源技术领域,尤其是涉及一种抑制冲击电流的冗余电路及工作方法。

背景技术

服务器、网络交换机、冗余存储磁盘阵列(RAID)、以及其它形式的通信基础设施等高可用性系统,需要在整个使用生命周期内具有接近零的停机率。为实现高可靠性,系统的供电电源一般采用冗余电源,是由两个完全一样的电源组成,由冗余电路控制电源进行负载均衡,当一个电源出现故障时,另一个电源马上可以接管其工作,在更换电源后,又是两个电源协同工作。但如果系统存在容性负载时,在上电一瞬间是相当于短路的,瞬间电流理论上是无限大,这种冲击电流往往远远高于正常供电的电流值,如果供电源没有保护措施,可能会对供电源造成损害,即使有保护措施,也可能会触发供电源的保护机制从而使供电源无法启动,为了消除容性负载带来的电流冲击,目前普遍采用的技术是抑制冲击电流,但这种解决方式是在冗余电路基础上又增加了一套抑制冲击电流电路,不仅增加了电源体积,又增加了器件种类数量,降低了电源可靠性。

发明内容

为解决上述问题,本发明的目的是提供一种结构简单、制造成本低、可靠性高的抑制冲击电流的冗余电路,同时公开上述抑制冲击电流的冗余电路的工作方法。

为实现上述发明目的,本发明采用如下技术方案:

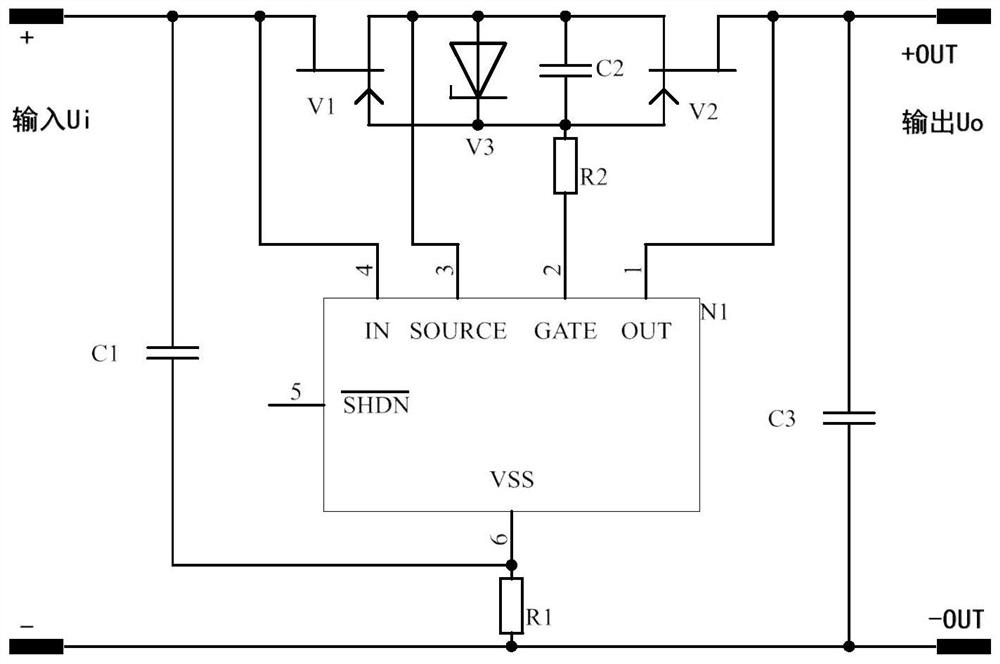

一种抑制冲击电流的冗余电路,其包括集成电路N1、第一MOS管V1、第二MOS管V2和稳压管V3,输入电源Ui的正极与集成电路N1的IN端连接,通过第一电容C1与集成电路N1的VSS端连接,且经第一电阻R1与输入电源Ui的负极连接,输入电源Ui的正极还与第一MOS管V1的漏极连接;第一MOS管V1的源极与集成电路N1的SOURCE端连接,第一MOS管V1的源极、栅极分别与第二MOS管V2的源极、栅极连接,且二者之间接有并联的稳压管V3、第二电容C2,第一MOS管V1、第二MOS管V2的栅极经第二电阻R2与集成电路N1的GATE端连接,第二MOS管V2的漏极与集成电路N1的OUT端、输出电压Uo的正极连接;输入电源Ui的负极与输出电压Uo的负极相连接,且与第二MOS管V2的漏极之间接有第三电容C3。

进一步地,上述的第一MOS管V1、第二MOS管V2均为N沟道MOS管。

进一步地,上述的集成电路N1的型号为LTC4359HDCB#TRPBF。

进一步地,上述的稳压管V3采用BW系列。

进一步地,上述的输入电源Ui为直流9V~80V。

一种抑制冲击电流的冗余电路的工作方法,其应用于上述的抑制冲击电流的冗余电路,包括以下步骤:

输入电压Ui通过第一电阻R1给集成电路N1供电,通过集成电路N1的IN端和OUT端分别采集输入电压和输出电压,当输入电压大于输出电压时,集成电路N1的GATE端将发出信号通过第二电阻R2到第一MOS管V1、第二MOS管V2的栅极,经过第二电阻R2给第二电容C2充电以及给稳压管V3供电,使第二MOS管V2的栅极和漏极电压缓慢上升,稳压管V3使第二MOS管V2的栅极和漏极电压值不会超过稳压管V3的稳压值,从而保护第二MOS管V2的栅极和漏极不会因为异常高电压损坏;

在第二电阻R2给第二电容C2充电过程中,第二MOS管V2将工作在线性区,从而使输出电压Uo的电压缓慢上升来给系统中容性负载供电,经过第二R2和第二电容C2组成的延时电路,延时一段时间后将完全打开第一MOS管V1和第二MOS管V2;

延迟时间通过以下公式进行计算:

T=R2×C2×ln((U-Uc)/U)

其中,R2为第二电阻R2的阻值,C2为第二电容C2的容值,Uc为充电电压,U为输入电压。

由于采用如上所述的技术方案,本发明具有如下优越性:

该抑制冲击电流的冗余电路,其电路设计简单,使用元器件少,制造成本低,体积小,功能兼容性强,实用性强,可靠性高,设置在电源输出端能够使电源兼具备冗余功能,还具备抑制输出浪涌冲击电流的功能,在上电瞬间,能抑制浪涌冲击电流,兼容系统中各种类型的负载,大大节省了空间和设计成本,适用范围广,适用于各种电源的冗余要求以及容性或感性负载要求,在电源应用领域具有广泛的应用前景。

附图说明

图1是本发明抑制冲击电流的冗余电路的原理图。

具体实施方式

下面结合附图和实施例对本发明的技术方案作进一步详细说明。

如图1所示,该抑制冲击电流的冗余电路,其包括集成电路N1、第一MOS管V1、第二MOS管V2和稳压管V3,输入电源Ui的正极与集成电路N1的IN端连接,通过第一电容C1与集成电路N1的VSS端连接,且经第一电阻R1与输入电源Ui的负极连接,输入电源Ui的正极还与第一MOS管V1的漏极连接;第一MOS管V1的源极与集成电路N1的SOURCE端连接,第一MOS管V1的源极、栅极分别与第二MOS管V2的源极、栅极连接,且二者之间接有并联的稳压管V3、第二电容C2,第一MOS管V1、第二MOS管V2的栅极经第二电阻R2与集成电路N1的GATE端连接,第二MOS管V2的漏极与集成电路N1的OUT端、输出电压Uo的正极连接;输入电源Ui的负极与输出电压Uo的负极相连接,且与第二MOS管V2的漏极之间接有第三电容C3。

上述的第一MOS管V1、第二MOS管V2均为N沟道增强型MOS管,型号均为IXFT88N30P。

上述的集成电路N1的型号为LTC4359HDCB#TRPBF。

上述的稳压管V3采用BW系列。

上述的输入电源Ui为直流9V~80V。

本发明抑制冲击电流的冗余电路,其工作过程为:输入电压Ui接入,通过第一电阻R1给集成电路N1供电,通过集成电路N1的IN端(引脚4)和OUT端(引脚1)分别采集输入电压和输出电压,当输入电压大于输出电压时,集成电路N1的GATE端(引脚2)将发出信号通过第二电阻R2到第一MOS管V1、第二MOS管V2的栅极(G),经过第二电阻R2给第二电容C2充电以及给稳压管V3供电,使第二MOS管V2的栅极(G)和漏极(S)电压缓慢上升,稳压管V3使第二MOS管V2的栅极(G)和漏极(S)电压值不会超过稳压管V3的稳压值,从而保护第二MOS管V2的栅极(G)和漏极(S)不会因为异常高电压损坏。

在第二电阻R2给第二电容C2充电过程中,第二MOS管V2将工作在线性区,从而使输出电压Uo的电压缓慢上升来给系统中容性负载供电,经过第二R2和第二电容C2组成的延时电路,延时一段时间后将完全打开第一MOS管V1和第二MOS管V2。

延迟时间通过以下公式进行计算:

T=R2×C2×ln((U-Uc)/U)

其中,R2为第二电阻R2的阻值,C2为第二电容C2的容值,Uc为充电电压,U为输入电压。

如果浪涌冲击电流的持续时间较长,要避开浪涌冲击电流过程的时间,就需要将第二MOS管V2延时导通的时间增长,根据公式:T=R2×C2×ln((U-Uc)/U),需要增大第二电阻R2和第二电容C2来满足时间的要求。

本发明抑制冲击电流的冗余电路,其在仅仅增加了第二MOS管V2、第二电阻R2和第二电容C2的情况下,利用MOS管线性工作区域,采用控制输出电压的缓慢增大来间接控制冲击电流的大小,而非直接去抑制冲击电流,从而实现了冗余电路抑制冲击电流的能力,使冗余电路同时具备了冗余和抑制冲击电流的双重功能。

本发明抑制冲击电流的冗余电路,其无需电源为针对感性或容性负载而增加功率,电源输出功率不需要考虑启动冲击电流带来的影响,满足正常工作状态下的电流即可,从而减小不必要的功率浪费。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种抑制冲击电流的冗余电路及工作方法

- 一种抑制冲击电流的电路及供电电路