电子装置

文献发布时间:2023-06-19 09:29:07

技术领域

本申请主要关于一种电子装置,尤指一种具有芯片以及与芯片接合的导电垫的电子装置。

背景技术

电子装置中的芯片可能接合于基板上(例如面板的基板或是软性电路的基板),经由设置于基板上的导电垫将芯片信号传送至面板或软性电路的基板中。因此,如何提高芯片与导电垫之间的接合度已成为现今需探讨的项目。

发明内容

本申请提供了一种电子装置,包括一基板、一第一导电垫及一芯片。第一导电垫设置于基板上。芯片包括一第二导电垫,电性连接于第一导电垫,且第一导电垫设置于基板与第二导电垫之间。第一导电垫具有第一凹槽。

附图说明

为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

图1为根据一些实施例中本申请的电子装置的俯视图。

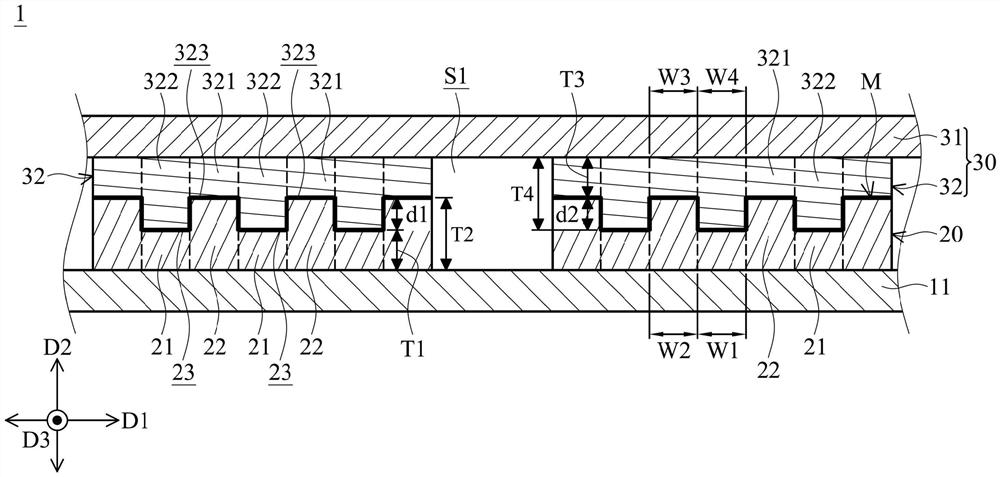

图2为本申请的第一实施例的电子装置的示意图。

图3为根据本申请的第一导电垫的多种不同实施例的俯视图。

图4A以及图4B为本申请电子装置的制作方法的一实施例的制程示意图。

图5为本申请的第二实施例的电子装置的示意图。

图6A以及图6B为本申请电子装置的制作方法的另一实施例的制程示意图。

图7为本申请的第三实施例的电子装置的示意图。

图8A以及图8B为本申请电子装置的制作方法的另一实施例的制程示意图。

图中元件标号说明:

电子装置 1

基板 11

信号线 13

第一导电垫 20

第一部分 21

第二部分 22

第一凹槽 23

芯片 30

基底 31

第二导电垫 32

第三部分 321

第四部分 322

第二凹槽 323

深度 d1、d2

方向 D1、D3

法线方向 D2

粘着层 G1、G2

导电粒子 G20

厚度 T1、T2、T3、T4

宽度 W1、W2、W3、W4

焊料合金 M

间隔空间 S1

操作区 Z1

非操作区 Z2

热压制程 P1

具体实施方式

以下的说明提供许多不同的实施例来实施本申请的不同特征。以下特定例子所描述的元件和排列方式,仅用来精简的表达本申请,其仅作为例子,而并非用以限制本申请。例如,第一元件在第二元件上的描述包括了第一和第二元件之间直接接触,或是以另一元件设置于第一和第二元件之间,以致于第一和第二元件并不是直接接触。第一元件与第二元件电性连接的描述包括第一和第二元件之间直接电性连接接触,或是更通过另一元件将第一和第二元件电性连接。

通过参考以下的详细描述并同时结合附图可以理解本申请,须注意的是,为了使读者能容易了解及附图的简洁,本申请中的多张附图只绘出电子装置的一部分,且附图中的特定元件并非依照实际比例绘图。此外,图中各元件的数量及尺寸仅作为示意,并非用来限制本申请的范围。

本申请通篇说明书与所附的权利要求中会使用某些词汇来指称特定元件。本领域技术人员应理解,电子设备制造商可能会以不同的名称来指称相同的元件。本文并不意在区分那些功能相同但名称不同的元件。在下文说明书与权利要求书中,“含有”与“包括”等词为开放式词语,因此其应被解释为“含有但不限定为…”之意。

此外,本说明书于不同的例子中沿用了相同的元件标号及/或文字。前述的沿用仅为了简化以及明确,并不表示于不同的实施例以及设定之间必定有关联。

虽然术语第一、第二、第三…可用以描述多种组成元件,但组成元件并不以此术语为限。此术语仅用于区别说明书内单一组成元件与其他组成元件。权利要求中可不使用相同术语,而依照权利要求中元件宣告的顺序以第一、第二、第三…取代。因此,在下文说明书中,第一组成元件在权利要求中可能为第二组成元件。

于此使用的空间上相关的词汇,例如上方或下方等,仅用以简易描述附图上的一元件或一特征相对于另一元件或特征的关系。除了附图上描述的方位外,包括于不同的方位使用或是操作的装置。此外,附图中的形状、尺寸以及厚度可能为了清楚说明的目的而未依照比例绘制或是被简化,仅提供说明之用。

在此,“约”、“大约”、“大致”等用语表示在一给定值或范围的20%之内、10%之内或5%之内。在此给定的数量为大约的数量,意即在没有特定说明的情况下,仍可隐含“约”、“大约”、“大致”等的含义。

图1为根据一些实施例中本申请的电子装置1的俯视图。电子装置1可包括电视、电脑、平板电脑、智慧型手机、车用面板、触控显示器、公用显示器、天线、检测装置等各式的电子装置,但不限于此。电子装置例如包括液晶、发光二极管(LED)、有机发光二极管(OLED)、微发光二极管显(micro-LED或mini-LED)、量子点发光二极管(Quantum Dot light-emitting diode,QD-LED;QLED)、萤光(fluorescence)材料、彩色滤光(Color filter,CF)材料、磷光(phosphor)材料、其他合适材料或上述的组合,在此不做限制。在某些实施例中,电子装置可以为有源式发光二极管(Active matrix,AM-LED)或无源式发光二极管(Passive matrix,PM-LED)。

电子装置1可包括一基板11、一(或多个)第一导电垫20以及一芯片30。第一导电垫20设置于基板11上。基板11可例如为阵列基板或电路板,但不限于此。电子装置1的基板11例如包括软性电路板(例如薄膜覆晶封装chip on film(COF))或硬性电路板,但不限于此。基板11的材料可包括玻璃、石英、金属、陶瓷、有机聚合物、塑料、其他合适材料或其组合,但不限于此。若基板11的材质为有机聚合物,例如包括聚酰亚胺(polyimide,PI)、聚对苯二甲酸乙二酯(polyethylene terephthalate,PET)、聚碳酸酯(polycarbonate,PC)、其他合适材料或其组合,但不限于此。在一些实施例中,基板11例如为阵列基板时,基板11例如可分为操作区Z1与非操作区Z2,非操作区Z2例如邻近或环绕于操作区Z1,但不限于此。在一些实施例中,非操作区Z2位于操作区Z1的至少一侧。操作区Z1例如包括显示区、检测区、发光区或其他合适的操作区,但不限于此,而非操作区Z2例如为线路区,但不限于此。在一些实施例中,多个第一导电垫20可设置于基板11上且对应非操作区Z2,且多个信号线13及多个像素(未绘示)可设置于基板11上,这些信号线13分别电性连接于第一导电垫20,而第一导电垫20通过信号线13电性连接至像素(例如像素的晶体管)。在一些实施例中,信号线13例如包括扫描线、数据线或读取线,但不限于此。须注意的是,附图中的第一导电垫20以及信号线13的数目仅为示意,并不予以限制,且附图的元件的尺寸仅为示意,为了使第一导电垫20、芯片30以及信号线13更为清楚,故将这些元件放大。

在一些实施例中,芯片30例如设置或接合于基板11上。详细来说,芯片30包括第二导电垫(图1未绘示,可参考图2的第二导电垫32),至少部分的第二导电垫32例如与电路基板10的第一导电垫20于基板11的法线方向D2上重叠,故芯片30可通过第二导电垫32与第一导电垫20电性连接。在一些实施例中,芯片30可包括驱动芯片,例如包括扫描芯片、数据芯片或其他合适的芯片,但不限于此。在一些实施例中,电子装置1包括至少一个芯片30,但不限于此。

图2为本申请的第一实施例的电子装置1的示意图。芯片30包括一基底31以及一(或多个)第二导电垫32,基底31上可设有其他电路(未绘示),但为了让附图更简易或清楚,基底31绘制成平坦的结构。第二导电垫32例如设置于基底31上且与其他电路电性连接,芯片30可通过第二导电垫32与第一导电垫20电性连接。在一些实施例中,第二导电垫32可直接接触或间接接触第一导电垫20。在一些实施例中,第一导电垫20设置于基板11与第二导电垫32之间,且第二导电垫32例如对应设置于第一导电垫20上,且第一导电垫20与第二导电垫32于基板11的法线方向D2上可大致重叠。在一些实施例中,多个第一导电垫20例如沿方向D1上排列或设置,且多个第二导电垫32例如沿方向D1上排列或设置。

在一些实施例中,第一导电垫20的材料可相同或不同于第二导电垫32的材料。第一导电垫20及第二导电垫32的材料可包括金属材料、透明导电材料或上述组合。第一导电垫20及/或第二导电垫32的材料可包括铜(Cu)、铝(Al)、钛(Ti)、金(Au)、锡(Sn)、银(Ag)、钼(Mo)、硅(Si)、铟锡氧化物(ITO)氧化锡(TO)、氧化铟锌(IZO)、氧化铟镓锌(IGZO)、氧化铟锡锌(ITZO)、氧化锑锡(ATO)、氧化锑锌(AZO)、其他适合的材料或其组合,但不限于此。在一些实施例中,第一导电垫20及/或第二导电垫32可例如包括单层导电层或多层导电层。在一些实施例中,第一导电垫20及/或第二导电垫32例如包括至少两层导电层,此至少两层导电层例如可直接接触而电性连接。举例来说,上述的至少两层导电层之间可设有至少一绝缘层(未绘示),且此至少两层导电层通过绝缘层的开口接触而电性连接,但不限于此。在一些实施例中,第一导电垫20例如为钼-铝-钼合金层上再设有一透明导电层,钼-铝-钼合金层与透明导电层之间例如具有至少一绝缘层,且此至少绝缘层具有开口露出部分钼-铝-钼合金层的上表面,透明导电层可通过此开口与钼-铝-钼合金层接触而电性连接,但不限于此。

在一些实施例中(图2),第一导电垫20例如具有至少一第一部分21以及至少一第二部分22。举例来说,于图2的剖视图中,第一部分21以及第二部分22可例如沿方向D1交错排列,但不限于此。

在一些实施例中,第二部分22的厚度T2大于第一部分21的厚度T1,其中第一部分21的厚度T1定义为于基板11的法线方向D2上第一部分21的最小厚度,而第二部分22的厚度T2定义为于基板11的法线方向D2上第二部分22的最大厚度。在一些实施例中,第一导电垫20为多层导电层,且多层导电层例如包括至少两层导电层时,第一部分21的最下层的导电层的底表面至最上层的导电层的上表面之间于基板11的法线方向D2上的最小厚度定义为第一部分21的厚度T1。另外,最下层的导电层的底表面至最上层的导电层的上表面之间于基板11的法线方向D2上的最大厚度定义为第二部分22的厚度T2。换句话说,第一导电垫20例如具有至少一第一凹槽23,第一凹槽23朝向第二导电垫32,两相邻的第二部分22及一第一部分21之间形成此第一凹槽23。第一凹槽23例如与第一部分21于基板11的法线方向D2上重叠,且第一凹槽23的深度d1可例如为第二部分22的厚度T2扣除第一部分21的厚度T1。第一凹槽23的深度d1定义为第一凹槽23于基板11的法线方向D2上的最大深度。须注意的是,当第一导电垫20为多层导电层时,且多层导电层之间设有至少一绝缘层时,第一凹槽23例如定义为第一导电垫20的最上层的导电层(即最邻近第二导电垫32的导电层)的凹槽。须注意的是,当第一导电垫20为多层导电层,且不同的导电层之间直接接触(即不同的导电层之间未设有其它绝缘层),此时第一凹槽23例如定义为此第一导电垫20的多层导电层的凹槽。须注意的是,当第一导电垫20为单层导电层时,此时第一凹槽23例如定义为此第一导电垫20的凹槽。在一些实施例中,第二部分22的厚度T2与第一部分21的厚度T1的比例介于1至4之间(1 在一些实施例中,第一凹槽23的深度d1小于第二部分22的厚度T2,第一凹槽23的深度d1与第二部分22的厚度T2的比例介于0.1至1之间(0.1 需注意的是,上述或后续所提的层别(部分或元件)的厚度或深度可例如通过扫描式电子显微镜(scanning electron microscope,SEM)来测量,例如可拍摄该层别(元件)的剖视切面下的SEM影像,且通过测量该层别(或部分或元件)于SEM影像中如上所定义的最大厚度、最小厚度、最大深度来获得,或者可通过其他合适的测量方法来测量。 在一些实施例中,第二导电垫32例如具有至少一第三部分321以及至少一第四部分322。于图2中,第三部分321以及第四部分322可例如沿方向D1交错排列,但并不以此为限。 在一些实施例中,第四部分322的厚度T4大于第三部分321的厚度T3。第三部分321的厚度T3定义为于基板11的法线方向D2上第三部分321的最小厚度,而第四部分322的厚度T4定义为于基板11的法线方向D2上第四部分322的最大厚度。在一些实施例中,第二导电垫32为多层导电层,例如包括至少两层导电层,第三部分321的最下层的导电层的底表面(例如邻近于基底31的表面)至最上层的导电层的上表面(例如邻近于第一导电垫20的表面)之间于基板11的法线方向D2上的最小厚度定义为第三部分321的厚度T3。另外,最下层的导电层的底表面至最上层的导电层的上表面的之间于基板11的法线方向D2上的最大厚度定义为第四部分322的厚度T4。换句话说,第二导电垫32例如具有至少一第二凹槽323,第二凹槽323朝向第一导电垫20,两相邻的第四部分322及第三部分321之间形成此第二凹槽323。在一些实施例中,第二凹槽323例如与第三部分321于基板11的法线方向D2上重叠,第二凹槽323的深度d2可例如为第四部分322的厚度T4扣除第三部分321的厚度T3。第二凹槽323的深度d2定义为于基板11的法线方向D2上的第二凹槽323的最大深度。须注意的是,当第二导电垫32为多层导电层时,不同的导电层之间可设有至少一绝缘层时,第二凹槽323例如定义为第二导电垫32的最上层导电层(即最邻近第一导电垫20的导电层的凹槽)。须注意的是,当第二导电垫32为多层导电层时,且不同的导电层之间直接接触时,即不同的导电层之间未设有其它绝缘层时,此时第二凹槽323例如定义为此第二导电垫32的多层导电层的凹槽。须注意的是,当第二导电垫32为单层结构时,此时第二凹槽323例如定义为此第二导电垫32的凹槽。 在一些实施例中,第四部分322的厚度T4与第三部分321的厚度T3的比例介于1至4之间(1 在一些实施例中,第二凹槽323的深度d2小于第四部分322的厚度T4。在一些实施例中,第二凹槽323的深度d2与第四部分322的厚度T4的比例介于0.1至1之间(0.1 在一些实施例中,如图2所示,于基板11的法线方向D2上,第四部分322例如与第一部分21重叠,且第三部分321例如与第二部分22重叠。换句话说,部分第四部分322例如位于第一凹槽23内,部分第二部分22例如位于第二凹槽323内。在一些实施例中,第四部分322的宽度W4小于第一部分21的宽度W1。在一些实施例中,第二部分22的宽度W2例如小于第三部分321的宽度W3。换句话说,在一些实施例中,第四部分322的宽度W4可小于第一凹槽23的宽度,第二部分22的宽度W2可小于第二凹槽323的宽度。在一些实施例中,第一凹槽23的宽度和第四部分322的宽度W4的差异介于0微米至14微米(μm)之间(0微米<ΔW≦14微米)。在一些实施例中,第一凹槽23的宽度和第四部分322的宽度W4的差异介于0微米至7微米(μm)之间(0微米<ΔW≦7微米)。在一些实施例中,第二凹槽323的宽度和第二部分22的宽度W2的差异介于0微米至14微米(μm)之间(0微米<ΔW≦14微米)。在一些实施例中,第二凹槽323的宽度和第二部分22的宽度W2的差异介于0微米至7微米(μm)之间(0微米<ΔW≦7微米)。上述的宽度W1、宽度W2、宽度W3及宽度W4比较须在相同的方向上做比较,例如需在垂直于基板11的法线方向D2上的任一方向(包括方向D1或方向D3)。方向D3例如于基板11的法线方向D2及方向D1垂直,但不限于此。上述第一部分21的宽度W1、第二部分22的宽度W2、第三部分321的宽度W3以及第四部分322的宽度W4例如为上述部分于在垂直于基板11的法线方向D2上的任一方向上的最大宽度。上述宽度可例如通过光学显微镜(optical microscopy,OM)来拍摄出画面,并测量该层于画面中的最大宽度来获得,或者可通过其他合适的测量方法来测量。 在一些实施例中,第一导电垫20的第一凹槽23及第二导电垫32的第二凹槽323例如错位设置。换句话说,于基板11的法线方向D2上,第一凹槽23与第二凹槽323无重叠。在一些实施例中,第四部分322投影至基板11的投影面积例如小于第一凹槽23投影至基板11的投影面积。在一些实施例中,第二部分22投影至基板11的投影面积例如小于第二凹槽323投影至基板11的投影面积。在一些实施例中,第二导电垫32的第四部分322投影至基板11上的投影面积的形状可例如大致相同或对应于第一凹槽23投影至基板11上的投影面积的形状设计。另外,第一导电垫20的第二部分22投影至基板11上的投影面积的形状可例如大致相同或对应于第二凹槽323投影至基板11上的投影面积的形状设计。在一些实施例中,第一导电垫20的结构例如互补于第二导电垫32的结构,即第一导电垫20的凹槽处对应第二导电垫32的凸起处,第一导电垫20的凸起处对应第二导电垫32的凹槽处。借由上述第一导电垫20以及第二导电垫32的结构设计,可提高芯片30与电路基板10之间的接合效果,或增加芯片30与电路基板10之间的导电性。 图3为根据本申请的第一导电垫20的多种不同实施例的俯视图。于基板11的法线方向D2上,第一凹槽23的形状(如图4中的黑色部分)可包括线条、网格、曲线、圆型、多边型、其他适合形状、或其组合,但并不以此为限。在一些实施例中,第一凹槽23可为连续的形状或非连续的形状。上述的第一凹槽23为非连续的形状即例如第一导电垫20具有多个第一凹槽23。在一些实施例中,第二凹槽323可以为连续的形状或非连续的形状。上述的第二凹槽323为非连续的形状即例如第二导电垫32具有多个第二凹槽323。在一些实施例中,第一凹槽23投影至基板11上的投影面积A1与第一导电垫20投影至基板11上的投影面积A2的比例为0.05至0.95之间(0.05≦A1/A2≦0.95)。在一些实施例中,投影面积A1与投影面积A2的比例为0.2至0.8之间(0.2≦A1/A2≦0.8)。在一些实施例中,投影面积A1与投影面积A2的比例为0.4至0.6之间(0.4≦A1/A2≦0.6)。在一些实施例中,第二凹槽323投影至基板11上的投影面积A3与第二导电垫32投影至基板11上的投影面积A4的比例为0.05至0.95之间(0.05≦A3/A4≦0.95)。在一些实施例中,投影面积A3与投影面积A4的比例为0.2至0.8之间(0.2≦A3/A4≦0.8)。在一些实施例中,投影面积A3与投影面积A4的比例为0.4至0.6之间(0.4≦A3/A4≦0.6)。在一些实施例中,不同的第一凹槽23投影至基板11上的投影面积或形状可以相同或不同。在一些实施例中,不同的第二凹槽323投影至基板11上的投影面积或形状可以相同或不同。 上述的第一导电垫20的第一凹槽23或第二导电垫32的第二凹槽323例如通过激光、轮刀、光刻制程(例如包括曝光、显影或蚀刻等制程)或其它合适的方式来制作,但不限于此。 图4A及图4B为本申请电子装置1的制作方法的一实施例的制程示意图。如图4A所示,将芯片30的第二导电垫32与电路基板10的第一导电垫20对位。上述对位例如将第二导电垫32与第一导电垫20于基板11的法线方向D2重叠设置。后续如图4B所示,将部分的第四部分322设置于第一凹槽23内,且部分的第二部分22例如设置于第二凹槽323内。在一些实施例,至少部分第一部分21例如接触于第四部分322。在一些实施例,至少部分第二部分22例如接触于第三部分321,之后例如通过热压制程P1提供适当的压力及/或适当温度,使第二导电垫32与第一导电垫20进行接合(例如溶融结合)。在一些实施例中,接合后的第一导电垫20与第二导电垫32之间产生焊料合金M,焊料合金M例如为金属间化合物(intermetallic compound,IMC),但不以此为限。此焊料合金M的材料例如包括至少部分第一导电垫20中的材料与至少部分第二导电垫32中的材料,但不限于此。 图5为本申请的第二实施例的电子装置1的示意图。第二实施例与图2的第一实施例具有相似的结构。于第二实施例中,电子装置1更包括一粘着层G1邻近第一导电垫20及第二导电垫32设置,且粘着层G1设置于第一导电垫20及第二导电垫32之间。在一些实施例中,粘着层G1包括为一绝缘胶,粘着层G1的材料包括热固性高分子材料或热塑性高分子材料,例如,环氧树脂或丙烯酸树脂、丙烯酸多醇树酯(acrylic polyol resin)、其他合适的材料或上述的组合,但不限于此。在一些实施例中,接合后的两相邻的第一导电垫20以及两相邻的第二导电垫32之间例如形成一间隔空间S1。在一些实施例中,粘着层G1例如设置于间隔空间S1中,但不限于此。在一些实施例中,空气层例如设置于间隔空间S1中。在一些实施例中,粘着层G1例如设置于第一凹槽23及/或第二凹槽323内。 在一些实施例中(图5),第四部分322的宽度W4例如小于第一部分21的宽度W1。借由将粘着层G1设置于第一导电垫20及第二导电垫32之间,或将粘着层G1设置于间隔空间S1中,甚至部分粘着层G1设置于第一凹槽23及/或第二凹槽323内,可提高芯片30与电路基板10之间的接合效果,或增加芯片30与电路基板10之间的导电性。 图6A以及图6B为本申请电子装置1的制作方法的另一实施例的制程示意图。如图6A所示,于接合前,可例如将粘着层G1设置于电路基板10的第一导电垫20上,后续将芯片30的第二导电垫32与第一导电垫20对位,上述对位例如将第二导电垫32与第一导电垫20于基板11的法线方向D2重叠设置,此时粘着层G1例如设置于第二导电垫32与第一导电垫20之间。详细来说,在一实施例中,第四部分322可对应于第一凹槽23,第二部分22可对应于第二凹槽323设置。如图6B所示,将部分的第四部分322例如设置于第一凹槽23内,部分的第二部分22例如设置于第二凹槽323内。在一些实施例,例如通过热压制程P1提供适当的压力以及/或适当温度,使第二导电垫32与第一导电垫20进行接合。于上述图6A及图6B的实施例中,粘着层G1可包括具有绝缘特性的胶材,当粘着层G1设置于间隔空间S1时,不会使两相邻的第一导电垫20经由粘着层电性连接,且不会使得两相邻的第二导电垫32经由粘着层电性连接。在一些实施例中,粘着层G1可具有缓冲或支撑特性的材料,粘着层G1可使基底31与基板11之间维持适当的距离,减少基底31与基板11之间不适当的压合。 图7为本申请的第三实施例的电子装置1的示意图。第三实施例与图5的第二实施例具有相似的结构。在一些实施例中,粘着层G2可包括异方性导电胶或其它导电胶。在一些实施例中,粘着层G2设置于间隔空间S1中。在一些实施例中,粘着层G2可例如设置于第一凹槽23及/或第二凹槽323内。于图7实施例中,粘着层G2包括多个导电粒子G20,导电粒子G20可例如设置于第一导电垫20及第二导电垫32之间,第一导电垫20可经由导电粒子G20电性连接于第二导电垫32。在一些实施例中,导电粒子G20的材料包括金、镍、银、铜、锡、其他合适金属材料、或其合金,或其他合适导电材料、或上述任意组合,但本申请并不仅限于此。在一些实施例中,导电粒子G20的最大宽度可例如小于第一部分21的宽度W1(或第一凹槽23的宽度),或导电粒子G20的最大宽度可例如小于第三部分321的宽度W3(或第二凹槽323的宽度)。在一些实施例中,导电粒子G20的最大宽度可例如小于第一凹槽23的深度d1,或导电粒子G20的最大宽度可例如小于第二凹槽323的深度d2。因此,借由粘着层G2可提高芯片30与电路基板10之间的接合效果,或增加芯片30与电路基板10之间的导电性。 图8A及图8B为本申请电子装置1的制作方法的一实施例的制程示意图。如图8A所示,于接合前,可例如将粘着层G2设置于电路基板10的第一导电垫20上,后续将芯片30的第二导电垫32与第一导电垫20对位,对位例如将第二导电垫32与第一导电垫20于基板11的法线方向D2重叠设置,此时粘着层G2例如设置于第二导电垫32与第一导电垫20之间。详细来说,在一实施例中,第四部分322对应于第一凹槽23,第二部分22对应于第二凹槽323。如图8B所示,将第四部分322例如设置于第一凹槽23内,且第二部分22例如设置于第二凹槽323内。在一些实施例,通过热压制程P1提供适当的压力以及/或适当温度,使第二导电垫32与第一导电垫20进行接合。 上述已公开的特征能以任何适当方式与一或多个已公开的实施例相互组合、修饰、置换或转用,并不限定于特定的实施例。 本申请的一些实施例提供优于现有技术的优点,但应理解,其他实施例可提供不同的优点。于本申请中不需要讨论所有的优点,并且并非所有实施例都需要特定的优点。多种优点可呈现在一些实施例中。 综上所述,本申请的电子装置的芯片可借由第一导电垫固定于基板。此外,借由第一导电垫以及第二导电垫的结构设计,使得芯片更能稳固定设置于基板上,并可增加芯片与第一导电垫之间的导电率。 虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的修改和完善,因此本发明的保护范围当以权利要求书所界定的为准。

- 电子装置的运行状态估计设备、电子装置的运行状态估计方法、电子装置的特征向量登记设备、电子装置的特征向量登记方法、服务器装置和电子装置的运行状态估计系统

- 电子装置、安装有电子装置的电子设备、安装有电子装置的物品、电子装置的制造方法