磁性存储单元及其制作方法

文献发布时间:2023-06-19 09:33:52

技术领域

本发明涉及半导体元件技术领域,特别是涉及一种自旋转移力矩式磁阻随机存取存储器(spin-transfer torque magnetoresistive random access memory,STT-MRAM)结构及其制作方法。

背景技术

如本领域中已知,自旋转移力矩式磁阻随机存取存储器(STT-MRAM)等磁性存储器装置是最近在存储器技术领域中十分受到关注的非挥发性存储器,其具有优于传统磁阻随机存取存储器的若干优点,例如,包括更高的耐用性、更低的功耗和更快的操作速度。

在两个铁磁层(ferromagnetic layer)间具有薄绝缘层的磁隧穿结(magnetotunnel junction,MTJ)中,隧穿阻值(tunnel resistance TMR)会根据两个铁磁层的相对磁化方向而变化。磁阻随机存取存储器具有利用隧穿磁阻(tunnel magnetoresistance,TMR)效应的磁隧穿结结构的半导体元件,能以矩阵排列成存储器单元。

在传统设计中,MTJ位单元阵列的源极线(source line,SL)被布置为与位线(bitline,BL)平行。然而,在传统设计中,由于通孔和金属间隔规则,源极线(SL)和位线(BL)之间没有直接和平行的重叠。因此,受限于金属和通孔间隔规则,传统设计的最小位单元尺寸不能再减小或最小化。

因为存储器包括至少数十万个存储单元,所以只要稍微减小每个存储单元中的面积就可以导致存储器密度的显著提升。由此可知,目前该技术领域仍需要一种MRAM存储单元结构,具有更小的MRAM存储单元面积,来改善MRAM存储器阵列密度。

发明内容

本发明提供了一种改良的自旋转移力矩式磁阻随机存取存储器(STT-MRAM)结构及其制作方法,能解决上述先前技术的不足。

本发明一方面披露一种磁性存储单元,包含一基底,具有一存储区。在所述基底上的所述存储区内设有一选择晶体管。在所述基底上设有一第一介电层,其中,所述第一介电层覆盖所述存储区和所述选择晶体管。在所述第一介电层中设置有一接垫,其中,所述接垫位于一第一水平面且电连接至所述选择晶体管的一漏极区。所述第二介电层覆盖所述第一介电层和所述接垫。在所述第二介电层中设置有一柱状存储器堆叠,其中,所述柱状存储器堆叠包含电耦合至所述接垫的一底电极、电耦合至设置于所述第二介电层上的位线的一上电极,以及介于所述底电极和所述上电极之间的一磁隧穿结。在所述第一介电层中设置有一源极线,其中,所述源极线位于一第二水平面且电连接至所述选择晶体管的一源极区,其中,所述第二水平面低于所述第一水平面。

依据本发明实施例,所述接垫位于第一金属层中。依据本发明实施例,所述源极线可以位于一第零金属层中且接近所述接垫,但不限于此。依据本发明实施例,所述第零金属层为一钨金属层,且所述第一金属层为一镶嵌铜层。

依据本发明实施例,所述第二介电层可以包含氮掺杂碳化硅层、硅氧层,以及超低介电常数材料层。所述磁性存储单元另包含一介层插塞,设于所述硅氧层和所述氮掺杂碳化硅层中,且所述介层插塞电连接所述底电极和所述接垫,例如,所述介层插塞可以是钨金属介层插塞。

依据本发明实施例,另包含一字符线,设于所述基底上且电连接至所述选择晶体管的一栅极,其中,所述字符线沿着一第一方向延伸。所述源极线沿着所述第一方向延伸,且所述位线沿着一第二方向延伸,且所述第二方向垂直于所述第一方向。

另一方面,本发明披露的磁性存储单元包含一基底,具有一存储区。在所述基底上的所述存储区内设有一选择晶体管。在所述基底上设有一第一介电层,其中,所述第一介电层覆盖所述存储区和所述选择晶体管。在所述第一介电层中设置有一接垫,其中,所述接垫位于一第一水平面且电连接至所述选择晶体管的一漏极区。所述第二介电层覆盖所述第一介电层和所述接垫。在所述第二介电层中设置有一柱状存储器堆叠,其中,所述柱状存储器堆叠包含电耦合至所述接垫的一底电极、电耦合至设置于所述第二介电层上的位线的一上电极,以及介于所述底电极和所述上电极之间的一磁隧穿结。所述磁性存储单元的源极线设于所述第二介电层中,其中,所述源极线位于第二水平面且电连接至所述选择晶体管的源极区,其中,所述第二水平面高于所述第一水平面。依据本发明实施例,所述接垫位于第一金属层中。依据本发明实施例,所述源极线可以位于第二金属层中,但不限于此。

依据本发明实施例,所述第二介电层可以包含氮掺杂碳化硅层、硅氧层,以及超低介电常数材料层。所述磁性存储单元另包含一介层插塞,设于所述硅氧层和所述氮掺杂碳化硅层中,且所述介层插塞电连接所述底电极和所述接垫,例如,所述介层插塞可以是钨金属介层插塞。

本发明另一方面披露一种形成磁性存储单元的方法,包含:提供一基底,具有一存储区。在所述基底上的所述存储区内形成一选择晶体管。在所述基底上形成一第一介电层,其中,所述第一介电层覆盖所述存储区和所述选择晶体管。在所述第一介电层中形成一接垫,其中,所述接垫位于一第一水平面且电连接至所述选择晶体管的一漏极区。形成一第二介电层,覆盖所述第一介电层和所述接垫。在所述第二介电层中形成一柱状存储器堆叠,其中,所述柱状存储器堆叠包含一电耦合至所述接垫的底电极,以及一电耦合至设置于所述第二介电层上的一位线的一上电极。形成一源极线,其中,所述源极线位于一第二水平面且电连接至所述选择晶体管的一源极区。

附图说明

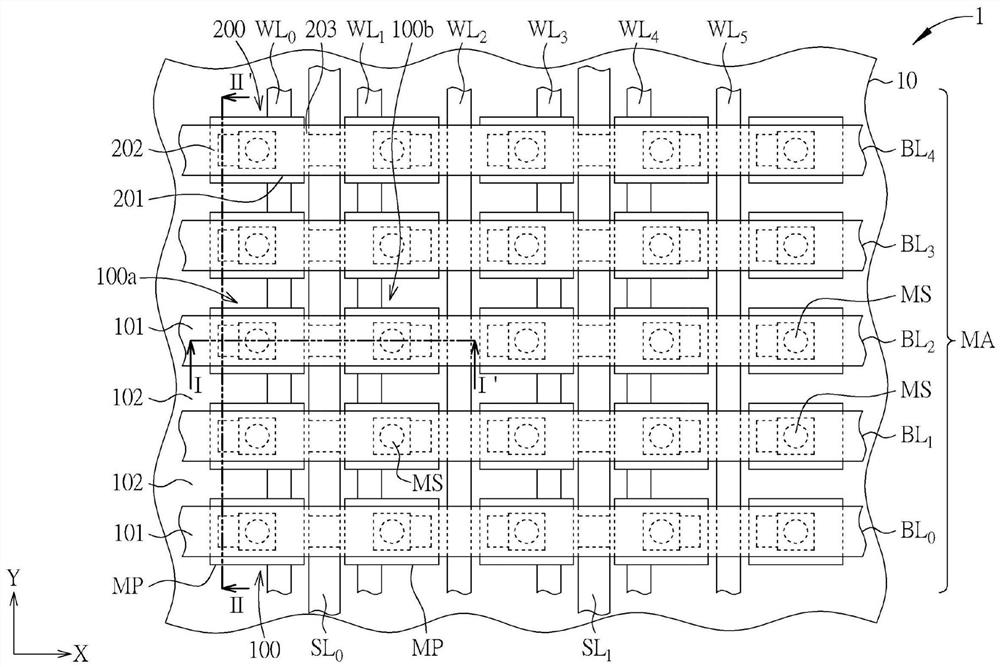

图1为本发明一实施例所绘示的一种磁性存储器装置的部分布局示意图;

图2为沿着图1中切线I-I’所示的剖面示意图;

图3为沿着图1中切线II-II’所示的剖面示意图;

图4为本发明另一实施例所绘示的磁性存储单元结构剖面示意图。

主要元件符号说明

1 磁性存储器装置

10 基底

100、100a、100b 存储单元

101 主动(有源)区域

101a 上表面

102 浅沟绝缘区域

102a 上表面

200、200a、200b 选择晶体管

201 栅极

202 漏极掺杂区(或漏极区)

203 源极掺杂区(或源极区)

310~340 介电层

321 氮掺杂碳化硅层

322 硅氧层

323 超低介电常数材料层

331 氮掺杂碳化硅层

332 超低介电常数材料层

341 氮掺杂碳化硅层

342 超低介电常数材料层

BE、BE

BL、BL

C

CP

MA 存储区

MP、MP

MS、MS

MTJ、MTJ

PW P型阱

SL、SL

SP

TE、TE

WL、WL

w

w

V

VP、VP

具体实施方式

在下文中,将参照附图说明细节,该些附图中的内容也构成说明书细节描述的一部分,并且以可实行该实施例的特例描述方式来绘示。下文实施例已描述足够的细节使该领域的一般技术人士得以具以实施。

当然,也可采行其他的实施例,或是在不悖离文中所述实施例的前提下作出任何结构性、逻辑性、及电性上的改变。因此,下文的细节描述不应被视为是限制,反之,其中所包含的实施例将由随附的权利要求来加以界定。

请参阅图1至图3,其中图1为依据本发明一实施例所绘示的一种磁性存储器装置的部分布局示意图,图2为沿着图1中切线I-I’所示的剖面示意图,图3为沿着图1中切线II-II’所示的剖面示意图。依据本发明实施例,如图1和图2所示,磁性存储器装置1包含一基底10,例如,P型硅基底,但不限于此。依据本发明实施例,基底10内可以设有一P型阱(PW),但不限于此。所述基底10上具有一存储区MA。在所述基底10上的所述存储区MA内,设有多个以阵列排列的存储单元100。在所述基底10上具有多个带状的且互相平行的主动区域101,彼此被带状的浅沟绝缘区域102所隔离开来。依据本发明实施例,所述带状的主动区域101和带状的浅沟绝缘区域102沿着一参考X轴延伸。

如图3所示,依据本发明实施例,通过将浅沟绝缘区域102进一步的凹陷蚀刻,可以使主动区域101的上端突出于浅沟绝缘区域102的上表面102a。依据本发明实施例,例如,主动区域101的上表面101a的宽度AA约略为70nm,而突出于浅沟绝缘区域102的高度约为35nm,但不限于此。

依据本发明实施例,在基底10上另有多条沿着一参考Y轴延伸的字符线WL

在图2中,仅例示的绘示出字符线WL

如图2所示,在基底10上设有多层介电层310~340,但不限于此。例如,介电层310可以是超低介电常数材料层。例如,所述超低介电常数材料层可以是介电常数范围例如是

依据本发明实施例,在介电层320上可以形成介电层330和介电层340,其中,介电层330可以包含例如氮掺杂碳化硅(NDC)层331和超低介电常数材料层332,介电层340可以包含例如氮掺杂碳化硅(NDC)层341和超低介电常数材料层342。

如图1所示,在存储器区MA内设置有多个接垫MP,其中接垫MP以阵列排列,且各接垫MP与选择晶体管200的漏极掺杂区202重叠。此外,在X轴方向上,各接垫MP可以与部分的字符线WL

依据本发明实施例,如图2所示,接垫MP

如图1所示,在存储器区MA内设置有多个柱状存储器堆叠MS,其中柱状存储器堆叠MS以阵列排列,且各柱状存储器堆叠MS对准各接垫MP。依据本发明实施例,图2例示设置于硅氧层322和氮掺杂碳化硅层321中的介层插塞VP

依据本发明实施例,如图2所示,介层插塞VP

如图2所示,柱状存储器堆叠MS

依据本发明实施例,底电极BE

图1例示多条沿着参考X轴延伸的位线BL

如图1和图2所示,在基底10上另设置有多条沿着参考Y轴方向延伸的源极线SL(图1仅例示SL

依据本发明实施例,例示的源极线SL

本发明的主要优点在于:通过上述磁性存储器装置1的设计,MRAM存储单元的尺寸可以进一步缩小至约0.022μm

请参阅图4,其为依据本发明另一实施例所绘示的磁性存储单元结构剖面示意图,其中相同的元件、材料或层仍沿用相同的符号来表示。如图4所示,磁性存储单元100包含基底10,具有存储区MA。在基底10上的存储区MA内设有选择晶体管200。在基底10上设有第一介电层310,其中,第一介电层310覆盖存储区MA和选择晶体管200。在第一介电层310中设置有接垫MP,其中,接垫MP位于第一水平面且电连接至选择晶体管200的漏极掺杂区(或漏极区)202。第二介电层320覆盖第一介电层310和接垫MP。

在第二介电层320中设置有柱状存储器堆叠MS,其中,柱状存储器堆叠MS包含电耦合至接垫MP的底电极BE、电耦合至设置于第二介电层320上的位线BL的上电极TE,以及介于底电极BE和上电极TE之间的磁隧穿结MTJ。

在图4中的磁性存储单元100与前述图1~图3的结构上差异在于:图4中的磁性存储单元100的源极线SL设于第二介电层320中,其中,源极线SL位于第二水平面且电连接至所述选择晶体管的源极掺杂区(或源极区)203,其中,所述第二水平面高于所述第一水平面。依据本发明实施例,接垫MP位于第一金属(M1)层中。依据本发明实施例,源极线SL可以位于第二金属(M2)层中,但不限于此。

同样的,如图4所示,第二介电层320可以包含氮掺杂碳化硅层321、硅氧层322,以及超低介电常数材料层323。磁性存储单元100包含介层插塞VP,设于硅氧层322和氮掺杂碳化硅层321中,且介层插塞VP电连接底电极BE和接垫MP,例如,介层插塞VP是钨金属介层插塞。

本发明另一方面披露一种形成磁性存储单元的方法,包含:提供一基底10,具有一存储区MA。在所述基底10上的所述存储区MA内形成一选择晶体管200。在所述基底10上形成一第一介电层310,其中,所述第一介电层310覆盖所述存储区MA和所述选择晶体管200。在所述第一介电层310中形成一接垫MP,其中,所述接垫MP位于一第一水平面且电连接至所述选择晶体管200的一漏极区202。形成一第二介电层320,覆盖所述第一介电层310和所述接垫MP。在所述第二介电层320中形成一柱状存储器堆叠MS,其中,所述柱状存储器堆叠MS包含一电耦合至所述接垫MP的底电极BE,以及一电耦合至设置于所述第二介电层320上的一位线BL的一上电极TE。形成一源极线SL,其中,所述源极线SL位于一第二水平面且电连接至所述选择晶体管200的一源极区203。

以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

- 磁性存储单元以及制造磁性存储单元的方法

- 磁性存储单元的直接写入方法与磁性存储单元结构