一种非易失性铁电存储器及其制备方法

文献发布时间:2023-06-19 09:44:49

技术领域

本发明属于铁电存储技术领域,涉及一种包含有在铁电存储层的表层中构图形成的埋入式导电层的非易失性(Non-volatile)铁电存储器,还涉及该种铁电存储器的制备方法。

背景技术

随着信息技术的高速发展,信息的处理能力不断增强,数据量急剧增长,云计算、云存储、物联网等新技术层出不穷,对存储器性能的要求不断提高,特别是在低能耗、高容量、长时间的数据保持等方面。

经过三十多年的快速发展,基于浮栅结构的闪存器件在市场上取得了巨大的成功。但是,随着半导体工艺技术节点发展的不断推进,闪存器件的可缩微性面临着严峻的挑战,目前已经逼近了物理尺寸极限。发展可缩微的新型非易失存储器已经成为目前信息技术发展的热点。

铁电存储器的存储介质层即为具有可反转(或称为“翻转”)的电畴的铁电薄膜层,目前,实验室内可测出的电畴反转的最快速度可达到0.2ns,实际上它还可以更快。通常地,电畴的反转速度决定了存储器的读写时间,电畴反转的矫顽电压决定了器件的读写电压,它会随着薄膜厚度的降低而几乎呈等比例地减小。因此,铁电存储器具有数据读速度快、驱动电压低和存储密度高等优点,近年来得到了广泛的关注和较快的发展。

江安全等人提出了公开号为WO2017/177376A1、名称为“大电流读出铁电单晶薄膜存储器及其制备方法和操作方法”的专利申请,以及公开号为WO2019/047489A1、名称为“铁电存储集成电路及其操作方法和制备方法”的专利申请,上述专利申请揭示了独特的非破坏读出(NDRO)的铁电存储器,其利用畴壁的直流导电特性存储信息。并且,上述专利申请还具体地揭示了一种畴壁导电通道形成于编程凸块内的具体铁电存储器件结构,其中,利用例如半导体刻蚀工艺铁电薄膜或铁电基体表面构图形成该编程凸块结构。

申请人发现,上述专利申请在构图形成编程凸块结构的铁电存储单元过程中,通常采用半导体制造工艺中的离子刻蚀工艺来对铁电材料进行刻蚀,从形成编程凸块结构;但是,该刻蚀过程容易对铁电材料(特别是对编程凸块周边的铁电材料的晶体结构)产生破坏,从而导致铁电性能下降、铁电存储层中电畴的信息保持能力下降、开态读电流减小,进而大大影响了铁电存储器性能。目前铁电存储器的存储性能还存在不足,需要进一步优化。

发明内容

本发明的目的在于提高基于畴壁导电通道存储信息的铁电存储器的存储性能而提供一种非易失性铁电存储器及其制备方法。

本发明的目的可以通过以下技术方案来实现:

一种非易失性铁电存储器,包括铁电存储层、第一电极和第二电极,所述铁电存储层中的电畴的极化方向基本不平行所述铁电存储层的法线方向;

所述第一电极和第二电极结构相同,均包括在所述铁电存储层的表层中构图形成的埋入式导电层以及形成在所述埋入式导电层上的电极层;在所述第一电极和第二电极之间施加在某一方向上的写信号时使能位于一对埋入式导电层之间的部分铁电存储层的电畴反转,以至于能够建立连接第一电极和第二电极的畴壁导电通道。

进一步地,所述埋入式导电层与电极层形成欧姆接触。

优选地,所述埋入式导电层是通过对所述铁电存储层的表面局部地进行黑化处理、扩散处理或离子注入处理来形成的。

进一步地,所述埋入式导电层是通过对所述铁电存储层的表面进行黑化处理来形成的,其中,在黑化处理过程中,采用锂、铬、铁、锌、铝、镁、铜、钴、镍、锰、钛中的一种或者多种的组合来对所述铁电存储层的表面进行还原处理,以至于实现对所述铁电存储层的局部的导电化处理。

进一步地,所述埋入式导电层是通过对所述铁电存储层的表面进行扩散处理来形成的,其中,在扩散处理过程中,采用银、铜、铬、钴、钛、铱、钌的一种或者多种的组合作为扩散源向所述铁电存储层的表面扩散,以至于实现对所述铁电存储层的局部的导电化处理。

进一步地,所述埋入式导电层是通过对所述铁电存储层的表面进行离子注入处理来形成的,其中,在离子注入处理过程中,向所述铁电存储层的表面注入铝、银、金、铂、铜、钴、铬、钛、钌、铱的一种或者多种的组合,以至于实现对所述铁电存储层的局部的导电化处理。

进一步地,所述铁电存储层中的电畴在所述埋入式导电层之间的水平连线方向上具有电畴分量。

优选地,所述埋入式导电层的电阻率为10

优选地,所述埋入式导电层与所述电极层的接触电阻小于或等于50MΩ。

进一步地,用于导电化处理来形成埋入式导电层的所述铁电存储层的表面为平面、凹凸面或不规则形状表面,所述埋入式导电层从铁电存储层表面向内延伸。

进一步地,所述电极层部分覆盖或全部覆盖所述埋入式导电层。

进一步地,在所述第一电极和第二电极之间施加与所述某一方向相反的写信号时使能位于一对埋入式导电层之间的部分铁电存储层中已反转的电畴发生翻转回到初始极化方向,以至于使所述畴壁导电通道消失。

优选地,所述畴壁导电通道为具有单向直流导电特性的畴壁导电通道。

进一步地,所述铁电存储层为铁电单晶材料。

优选地,所述铁电存储层选自钽酸锂盐LiTaO

本发明还提供一种非易失性铁电存储器的制备方法,包括步骤:

提供包含有铁电存储层的基片;

对所述铁电存储层的表面构图地进行导电化处理,从而形成至少一对埋入式导电层;以及

在所述埋入式导电层上沉积电极层,从而形成包含所述埋入式导电层和所述电极层的第一电极以及第二电极;

其中,所述铁电存储层中的电畴的极化方向基本不平行所述铁电存储层的法线方向,在所述第一电极和第二电极之间施加在某一方向上的写信号时使能包括位于一对埋入式导电层之间的部分所述铁电存储层的电畴反转,以至于能够建立电连接所述第一电极和第二电极的畴壁导电通道。

进一步地,还包括步骤:在导电化处理后进行清洗处理。

进一步地,在导电化处理步骤中,通过对所述铁电存储层的表面局部地进行黑化处理、扩散处理或离子注入处理。

进一步地,在导电化处理步骤中,采用锂、铬、铁、锌、铝、镁、铜、钴、镍、锰、钛中的一种或者多种的组合来对所述铁电存储层的表面局部地进行还原处理以实现所述黑化处理。

优选地,在黑化处理过程中,在100℃-600℃温度条件下,在真空、保护性气氛或还原性气氛中将所述基片置于硅酸镁锂、碳酸锂或氯化锂粉体中并进行埋烧。

优选地,导电化处理步骤所采用的锂、铬、铁、锌、铝、镁、铜、钴、镍、锰或钛为金属粉末或者通过薄膜沉积工艺形成的金属薄膜。

进一步地,在导电化处理步骤中,采用银、铜、铬、钴、钛、铱、钌的一种或者多种的组合作为扩散源向所述铁电存储层的表面进行扩散处理。

优选地,导电化处理步骤所采用的银、铜、铬、钴、钛、铱或钌为金属粉末或者通过薄膜沉积工艺形成的金属薄膜。

进一步地,在导电化处理步骤中,以铝、银、金、铂、铜、钴、铬、钛、钌、铱的一种或者多种的组合作为粒子注入源向所述铁电存储层的表面进行金属离子注入。

与现有技术相比,本发明具有如下有益效果:

本发明具有凸块结构的铁电存储器相对不具有凸块结构(即铁电薄膜层为平层结构)的铁电存储器在存储性能方面表现更优。

本发明通过在铁电存储层的表层中构图形成的埋入式导电层以及形成在埋入式导电层上的电极层形成第一电极和第二电极,进而形成左右电极之间的类似编程凸块的结构,埋入式导电层可以通过对铁电存储层的上表面局部地进行黑化处理、扩散处理或离子注入处理等来形成。一方面,制备过程中对铁电存储介质破坏小,存储性能(例如数据保持性能和开态读电流等)得到提升,提高非易失性,例如,开态读电流可达到10

附图说明

从结合附图的以下详细说明中,将会使本发明的上述和其他目的及优点更加完整清楚,其中,相同或相似的要素采用相同的标号表示。

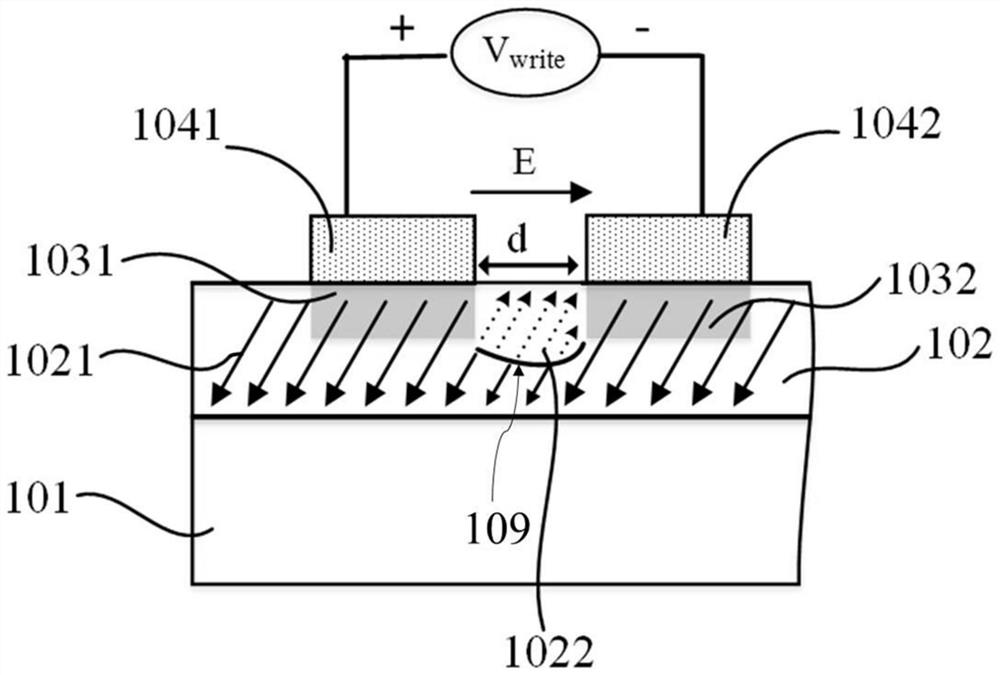

图1是按照本发明一实施例的非易失性铁电存储器图的截面结构示意图;

图2是按照本发明一实施例的铁电存储器的第一电极和第二电极的俯视平面结构示意图,其中(2a)、(2b)、(2c)分别示出三个示例;

图3是按照本发明一实施案例的铁电存储器试验样品的读写电极对的电流-电压(I-V)曲线示意图;

图4是按照本发明一实施例的铁电存储器的制备方法的流程图;

图5是以器件的局部截面结构变化示意图4所示实施例的制备方法的工序过程,其中,(5a)为铁电存储层形成于基片上,(5b)为在基片上形成覆盖层,(5c)为对覆盖层图案化处理,(5d)为形成还原金属层,(5e)为进行黑化处理,(5f)为构图形成沉积电极层;

图6是经过黑化处理形成的埋入式导电层的I-V测试特性;

图7是按照本发明又一实施例的铁电存储器的制备方法的流程图;

图8是以器件的局部截面结构变化示意图7所示实施例的制备方法的工序过程,其中,(8a)为铁电存储层形成于基片上,(8b)为在基片上形成覆盖层,(8c)为对覆盖层图案化处理,(8d)为进行离子注入处理,(8e)为构图形成沉积电极层,(8f)为构图形成沉积电极层;

图9是按照本发明还一实施例的铁电存储器的制备方法的流程图;

图10是以器件的局部截面结构变化示意图9所示实施例的制备方法的工序过程,其中,(10a)为铁电存储层形成于基片上,(10b)为在基片上形成覆盖层,(10c)为对覆盖层图案化处理,(10d)为形成还原金属层,(10e)为进行扩散处理,(10f)为构图形成沉积电极层。

图中标号:101-基片,102-铁电存储层,1031、1032-埋入式导电层,1041、1042-电极层,1021、1022-极化方向,109-畴壁导电通道,206、306、406-覆盖层,2051、2052、3051、3052、4051、4052-窗口区,2071、2072、4071、4072-还原金属层。

具体实施方式

下面结合附图和具体实施例对本发明进行详细说明。本实施例以本发明技术方案为前提进行实施,给出了详细的实施方式和具体的操作过程,但本发明的保护范围不限于下述的实施例。

在附图中,为了清楚起见,夸大了层和区域的厚度,图示中的各部分之间的尺寸比例关系并不反映实际的尺寸比例关系。

在以下实施例中,为了描述的清楚,示例性地给出了电畴方向或者极化方向,但是应当理解到,铁电存储器的电畴方向或极化方向并不限于如图所示实施例示出的方向。

在以下实施例中,铁电单晶薄膜层可以是外延单晶生长所形成的单晶薄膜、或者从单晶体中分离或切割所形成的薄膜层,其是指内部不存在多晶结构的“晶界”的单晶结构或类单晶结构,即最终形成的非破坏性读出铁电存储器的每个存储单元是一个单晶体结构,单元尺寸不限。

实施例1

本实施例提供一种非易失性铁电存储器,其截面结构示意图如图1所示。该铁电存储器主要包括包含铁电存储层102的基片101、电极层1041和1042,尤其地包括在铁电存储层102的表层中构图形成的埋入式导电层1031和1032。其中,电极层1041和1042分别对应埋入式导电层1031和1032设置,具体地,电极层1041与埋入式导电层1031形成欧姆接触,从而它们构成第一电极(也可以称为“左电极”),电极层1042与埋入式导电层1032可以形成欧姆接触,从而它们构成第二电极(也可以称为“右电极”));第一电极和第二电极可以用作该铁电存储器的读写电极对,其中,第一电极和第二电极可以相互分离地设置,在一实施例中,如图1所示,第一电极和第二电极之间具有间距d,该间距d的具体大小的范围可以大于或等于2纳米且小于或等于1微米,更优选地大于或等于5纳米且小于或等于0.5微米,例如可以为10纳米、100纳米等。将理解,间距d越小,越有利于提高铁电存储器的存储密度,并且越有利于减小写电压和读电压、增大读电流,并且读功耗和写功耗越小,因此,本发明实施例的铁电存储器可以按比例缩小(Scaling-down)。

基片101可以是铁电存储器中常用的各种基底材料,例如其可以为Si、SrTiO

铁电存储层102可以但不限于通过键合工艺、薄膜生成工艺等形成于初始基片101上,从而形成包含铁电存储层102的基片101。

铁电存储层102可以是铁电薄膜层,其具有合适畴结构,一般地,铁电存储层102在未进行以下示例说明的导电化处理之前,其表现为具有绝缘特性或者具有相对高的电阻率,并且容易在其表面上形成钝化层。铁电存储层102具体可以选择为专利号为WO2017/177376A1所公开的铁电单晶材料(例如铁电单晶薄膜),从而可以使得在开态下的读电流大大增加,该实施例的铁电存储器的性能得到提升。因此,公开号为WO2017/177376A1的专利全文在此以引用的形式包含于此。

但是,应该理解到,本发明实施例的铁电存储层102并不限于为铁电单晶层,其还可以为多晶的铁电薄膜层。铁电存储层102的厚度大于或等于埋入式导电层的深度或厚度。

如图1所示,铁电存储层102中的铁电畴的自发极化方向或初始极化方向1021为如图1中示意的方向,埋入式电极层1031和1032之间的铁电存储层102的电畴发生翻转后,其极化方向1022与极化方向1021完全相反。铁电存储层102中电畴的极化方向基本不平行铁电存储层102的法线方向,即铁电存储层102的法线与电畴的极化方向的夹角为不等于0和180o,例如45o,这样,铁电畴在铁电存储层102的面内(in-plane)上具有分量(例如铁电畴的自发极化在铁电存储层102的表面上或在埋入式导电层1031和1032之间的水平连线上具有电畴分量),易于实现用于控制电畴翻转的写操作。

在一实施例中,埋入式导电层1031/1032可以为铁电存储层102的表层局部地经导电化处理后的载流子浓度变大的高电导埋入区域,其电阻率可选地为10

如图1所示,电极层1041/1042的下表面可以与埋入式导电层1031/1032的上表面形成欧姆接触,并且控制它们形成相对低接触电阻,接触电阻小于或等于50MΩ(例如100Ω或更小)。将理解,通过控制埋入式导电层1031/1032的导电化处理过程,例如控制离子掺杂浓度,可以控制埋入式导电层1031/1032与电极层1041/1042的接触电阻。埋入式导电层1031/1032与电极层1041/1042可以具有相同的形状和/或图案,也可以具有不同的形状和/或图案。

在一实施例中,埋入式导电层1031和1032可以通过对铁电存储层102的上表面局部地进行黑化处理、扩散处理或离子注入处理来形成,因此,可以避免采用例如专利号为WO2017/177376A1中所公开的用于形成编程凸块的半导体刻蚀工艺,对铁电存储层102的破坏小。具体导电化处理将不限于黑化处理、离子注入处理或扩散处理,也可以通过其他方式来增加铁电存储层表面的载流子浓度来提高其电导率、降低基片的表层的电阻率,最终提高铁电畴保持性和开态读电流的大小。埋入式导电层1031和1032与铁电存储层102可能并不存在如图1中示出的相对清晰的界面,例如它们之间可能形成图1中未示出的缓变性的过渡界面。埋入式导电层1031和1032的具体结构和/或特性将通过以下示例的制备方面中详细示例说明。

需要说明的是,铁电存储层102的表面并不限于图1所示的平面状,用于导电化处理来形成埋入式导电层1031/1032的铁电存储层102的表面也可以为具有凸块、凹坑等形状的铁电存储层102的非平面表面,也可以为具有其他不规则形状的铁电存储层102的表面;埋入式导电层1031/1032可以从各种不规则形状的表面向铁电存储层内延伸。

鉴于埋入式导电层1031/1032的导电特性,在第一电极和第二电极之间施加固定在某一方向上的写信号(例如图1所示的写信号V

在一实施例中,在第一电极和第二电极之间施加与所述某一方向相反的写信号(例如与如图1所示的直流写信号V

图1所示实施例的铁电存储器可以采用例如黑化、金属原子扩散或金属离子注入技术等技术来形成埋入式导电层1031和1032,可以避免采用半导体刻蚀工艺对铁电存储层102产生的较大的破坏,因此可以实现平面状的电极层1041和1042无破坏性地向铁电存储层102的厚度方向延升,从而埋入式导电层1031可以与电极层1041整体形成第一电极、埋入式导电层1032可以与电极层1043整体形成第二电极;同时,第一电极和第二电极之间的铁电存储介质(例如埋入式导电层1031和1032之间的铁电存储介质)能够相对埋入式导电层1031和1032上凸,从而,第一电极、第二电极以及它们之间的铁电存储介质可以构成近似平行板的电容器结构。因此,图1所示实施例的铁电存储器能够大幅提高写入电畴信息(即逻辑状态信息)的保持时间和读出电流的大小。

图2所示为按照本发明一实施例的铁电存储器的第一电极和第二电极的俯视平面结构示意图,其中(2a)、(2b)、(2c)分别示出三个示例。如图2所示,电极层1041/1042的位置可以与埋入式导电层1031/1032的位置部分重合或者全部重合。示例地,在图2(a)中,电极层1041/1042覆盖大部分的埋入式导电层1031/1032,电极层1041和1042之间的间距d2大于埋入式导电层1031和1032之间的间距d2,埋入式导电层1031/1032的上方的电极层1041/1042的宽度W2也大于埋入式导电层1031/1032的宽度W1;在图2(b)中,电极层1041/1042基本覆盖埋入式导电层1031/1032,电极层1041和1042之间的间距d2基本等于埋入式导电层1031和1032之间的间距d2,埋入式导电层1031/1032的上方的电极层1041/1042的宽度W2大于埋入式导电层1031/1032的宽度W1;在图2(c)中,电极层1041/1042全部覆盖埋入式导电层1031/1032,电极层1041和1042之间的间距d2小于埋入式导电层1031和1032之间的间距d2,埋入式导电层1031/1032的上方的电极层1041/1042的宽度W2大于埋入式导电层1031/1032的宽度W1。

将理解,电极层1041/1042的具体形状并不限于以上实施例,其可以根据具体需要来设计其形状、尺寸等。

图3所示为按照本发明一实施案例的铁电存储器试验样品的读写电极对的电流-电压(I-V)曲线示意图,其中读写电极对的埋入式导电层是示例地通过黑化处理方法图形化形成的。

如图3中曲线1所示,对铁电存储器的读写电极对(即第一电极和第二电极)执行从-20V到+20V电压扫描,进行I-V曲线测量,可以发现电流在娇顽电压Vc约等于17V处突然从关态跳跃至开态,最大电流可以达到20μA,这预示着读写电极对之间的部分铁电存储层的电畴翻转、完成逻辑状态信息“1”的写入操作。当对以上试验样品器件再次进行从0至20V电压扫描时,发现该器件始终处于开态(如图3曲线2的I-V曲线所示),这预示着以上所写入的逻辑信息“1”的状态保持良好;相反,当施加一个-20V的写电压后,以上读写电极对之间的部分铁电存储层的电畴又反转回到初始状态,在0-20V之间再次扫描测量的I-V曲线,发现该曲线又恢复到原先曲线1对应的状态,这预示着已经完成逻辑状态信息“0”的写入操作。因此,当读电压固定在0和16.5V之间时,可以读出以上+/-20V写电压偏置条件下所写入的分别对应两种不同电畴状态下的开/关电流信息。

实施例2

以上图1所示实施例的铁电存储器示例地可以通过图4和图5示例的方法制备得到,以下结合图1、图4和图5示例说明该制备方法。

首先,步骤S410,提供包含有铁电存储层的基片。在该步骤中,如(5a),铁电存储层102可以通过外延生长、键合、薄膜沉积等方法形成在基片101上;铁电存储层选自钽酸锂盐LiTaO

步骤S420,如(5b)所示,在基片101上形成覆盖层206。覆盖层206具体可以为光刻胶,例如使用甩胶机在基片101的铁电存储层102的表面形成一层光刻胶206。

步骤S430,如(5c)所示,对覆盖层206图案化处理以形成待处理的窗口区2051和2052。该图案化处理可以通过光刻技术的曝光等过程实现,其中,窗口区的形状和/或尺寸可以根据需要形成的埋入式导电层的形状和/或尺寸来确定,从而,最终可以获得想要形成的形状和/或尺寸的埋入式导电层的1031和1032。窗口区2051和2052暴露待导电化处理的铁电存储层102。

步骤S440,如(5d)所示,对应窗口区2051和2052形成还原金属层2071和2072。在该步骤中,可以通过磁控溅射、热蒸发、电子束热蒸发等薄膜淀积工艺沉积一层还原金属层,然后,进行剥离剩余的覆盖层206来构图形成如(5d)所示的还原金属层2071和2072;其中,还原金属层2071和2072相对铁电存储层102具有还原性的金属,其可以为锂、铬、铁、锌、铝、镁、铜、钴、镍、锰、钛中的一种或者多种的组合,优选为锌、铝、铁等还原性强的金属;还原金属层的厚度可选为10nm-500nm。

步骤S450,如(5e)所示,进行黑化处理以在铁电存储层102中形成埋入式导电层1031和1032。在该步骤中,通过黑化处理,可以大大增加铁电存储层102的局部表面的例如氧空位的浓度,从而完成对铁电存储层102的局部表面的导电化处理。在一实施例中,可以将基片101置于100℃-600℃温度条件下的真空、保护性气氛或还原性气氛中,并在硅酸镁锂、碳酸锂或氯化锂粉体中对基片进行埋烧;具体地,可以将碳酸锂粉末放入石英刚玉坩埚中,基片101平放埋入碳酸锂粉末的还原试剂中,然后将该坩埚装入热处理炉中,然后,将热处理炉内气压抽至5pa,再用氩气与氢气的混合气体洗气5min-20min,最后进行退火处理;当降温到室温,开炉门取出基片,基片上将形成有如(5e)所示的埋入式导电层1031和1032;其中,氢气与氩气的摩尔比可选地为1:100-7:100,气体流量可选地为0.5L/min-10L/min;黑化处理温度可选地为100℃-600℃(例如450℃),升温速率可选地控制在1-5℃/min,恒温时间可选地为1-10h,升降温速率可选地为1-5℃/min。

步骤S460,将黑化后的基片进行清洗处理。在该步骤中,首先,采用稀盐酸溶液(其配比为浓盐酸:水=1:2(体积分数比))清洗,清洗时间可以为0.5-5min;然后,采用氢氧化钠溶液(其配比为氢氧化钠粉末与水的质量分数比为30:100)清洗,清洗时间可以为0.5-5min;最后用去离子水冲洗、吹干,在90℃热板上烘烤2-10min。

经观察,以铌酸锂基片为示例,铌酸锂基片的颜色相比于黑化处理之前的颜色有所加深,可以表明还原反应已经发生。可以通过原子力显微镜(AFM)进行表面形貌测试,确定基片101的表面平整(特别是铁电存储层102的表面)。通过如图6所示的电流-电压电学测量数据表明,黑化部分的铁电存储层(即埋入式导电层1031和1032)的电导率提高了2-5个数量级;其中,图6所示为经过黑化处理形成的埋入式导电层的I-V测试特性,其中示出了分别采用Al、Mg和Zn三种金属作为还原金属层的三种样品的I-V测试结果,300nm表示还原金属层的厚度、3%H

步骤S470,如(5f)所示,在埋入式导电层1031和1032上构图形成沉积电极层1041和1042,从而形成第一电极和第二电极。在该步骤中,可以通过微纳加工工艺,对经过还原性金属黑化处理后的表层区域对应地构图形成电极层1041和1042,从而形成了作为读写电极对的第一电极和第二电极。电极层1041和1042之间存在间隙d,间隙d的宽度可选地大于或等于2纳米且小于或等于1微米;电极层1041和1042的位置可以分别与埋入式导电层1031和1032的位置部分重合或者全部重合;电极层1041和1042的厚度可选地大于或等于10纳米且小于或等于500纳米。

至此,基本制备形成了如(5f)所示的铁电存储器,其中,埋入式导电层1031和1032之间的电畴在未偏置如图1所示的写信号V

实施例3

以上图1所示实施例的铁电存储器示例地可以通过图7和图8示例的方法制备得到,以下结合图1、图7和图8示例说明该制备方法。

首先,步骤S710,提供包含有铁电存储层的基片。在该步骤中与以上实施例的步骤S410基本类似,在此不再赘述。

步骤S720,如(8b)所示,在基片101上形成覆盖层306。覆盖层306具体可以为光刻胶,例如使用甩胶机在基片101的铁电存储层102表面形成一层光刻胶306。

步骤S730,如(8c)所示,对覆盖层306图案化处理以形成待处理的窗口区3051和3052。该图案化处理可以通过光学曝光,电子束曝光等工艺实现,其中,窗口区的形状和/或尺寸可以根据需要形成的埋入式导电层的形状和/或尺寸来确定,从而,最终可以获得想要形成的形状和/或尺寸的埋入式导电层的1031和1032。窗口区3051和3052暴露待导电化处理的铁电存储层102。

步骤S740,如(8d)所示,进行离子注入处理以在铁电存储层102中形成埋入式导电层1031和1032。在一实施例中,以窗口区3051和3052为离子注入区、以剩余的覆盖层306作掩膜,采用铝、银、金、铂、铜、钴、铬、钛、钌、铱的一种或者多种的组合作为离子注入源向窗口区的铁电存储层102的表面进行扩散处理。通过离子注入处理,可以大大增加铁电存储层102的局部表面的载流子浓度,从而完成对铁电存储层102的局部表面的导电化处理。

步骤S750,将离子注入后的基片进行清洗处理。在该步骤中,可以根据不同的离子注入源采用不同的清洗溶液;最后,用去离子水冲洗、吹干,并在90℃热板上烘烤2-10min。

步骤S760,如(8e)所示,在埋入式导电层1031和1032上构图形成沉积电极层1041和1042,从而形成第一电极和第二电极。该步骤S760与之前图4所示实施例中的步骤S470基本相同,在此不再赘述。

实施例4

以上图1所示实施例的铁电存储器示例地可以通过图9和图10示例的方法制备得到,以下结合图1、图9和图10示例说明该制备方法。

首先,步骤S910,提供包含有铁电存储层的基片。在该步骤中,如(10a),铁电存储层102可以通过外延生长、键合、薄膜沉积等方法形成在基片101上。

步骤S920,如(10b)所示,在基片101上形成覆盖层406。覆盖层406具体可以为光刻胶,例如使用甩胶机在基片101的铁电存储层102表面形成一层光刻胶406。

步骤S930,如(10c)所示,对覆盖层406图案化处理以形成待处理的窗口区4051和4052。窗口区4051和4052暴露待导电化处理的铁电存储层102。

步骤S940,如(10d)所示,对应窗口区4051和4052形成还原金属层4071和4072。在该步骤中,可以通过磁控溅射、热蒸发、电子束热蒸发等薄膜淀积工艺沉积一层扩散金属层,然后,剥离剩余的覆盖层406来构图形成如(10d)所示的扩散金属层4071和4072;其中,扩散金属层4071和4072可以为银、铜、铬、钴、钛、铱、钌中的一种或者多种的组合,优选为银、铜、铬、钴、钛等金属;扩散金属层4071和4072的厚度可选地为1nm-500nm(例如,10nm、50nm或100nm)。

步骤S950,如(10e)所示,进行扩散处理以在铁电存储层102中形成埋入式导电层1031和1032。在该步骤中,通过扩散处理,可以大大增加铁电存储层102的局部表面的载流子浓度,从而完成对铁电存储层102的局部表面的导电化处理。在一实施例中,可以将基片101放入石英刚玉坩埚中,然后将该坩埚装入热处理炉中进行退火处理;然后当降温到室温,开炉门取出铁电基片。其中,扩散处理温度为100℃-700℃,升温速率控制在1-5℃/min;恒温时间为1-10h;升降温速率为1-5℃/min。

步骤S960,将扩散处理后的基片进行清洗处理。在该步骤中,清洗基片根据不同的扩散金属采用不同的清洗溶液。最后用去离子水冲洗、吹干,在90℃热板上烘烤2min-10min。。

步骤S970,如(10f)所示,在埋入式导电层1031和1032上构图形成沉积电极层1041和1042,从而形成第一电极和第二电极。该步骤S970与之前图4所示实施例中的步骤S470基本相同,在此不再赘述。

至此,基本制备形成了如(10f)所示的铁电存储器,其中,埋入式导电层1031和1032之间的电畴在未偏置如图1所示的写信号V

在以上描述中,使用方向性术语(例如“上”、“下”等)以及类似术语描述的各种实施方式的部件表示附图中示出的方向或者能被本领域技术人员理解的方向。这些方向性术语用于相对的描述和澄清,而不是要将任何实施例的定向限定到具体的方向或定向。

以上例子主要说明了本发明的铁电存储器及其制备方法,尤其说明了读操作方法及原理。尽管只对其中一些本发明的实施方式进行了描述,但是本领域普通技术人员应当了解,本发明可以在不偏离其主旨与范围内以许多其他的形式实施,例如,第一电极和第二电极的形状变化,将以上实施例的电极层单独地定义为第一电极或第二电极但还是对应该电极层设置埋入式导电层,在制备过程中电极层和埋入式导电层同步地形成,等。因此,所展示的例子与实施方式被视为示意性的而非限制性的,在不脱离如所附各权利要求所定义的本发明精神及范围的情况下,本发明可能涵盖各种的修改与替换。

- 非易失性铁电存储器设备的制备方法和由此获得的存储器设备

- 一种非易失性铁电存储器及其制备方法