一种能够减小微功耗比较器输出级瞬态电流的控制电路

文献发布时间:2023-06-19 11:05:16

技术领域

本发明涉及芯片比较器电路技术,特别是一种能够减小微功耗比较器输出级瞬态电流的控制电路,通过在输出级的PMOS管连接结构中增加第一反相器和在输出级的NMOS管的连接结构中增加第二反相器,能够利用双反相器的延时效应使得输出端PMOS管Mpout和输出端NMOS管Mnout不出现同时导通的状态,从而避免因Mpout与Mnout同时导通的瞬间而出现的比较器输出级的较大瞬时输出电流,以保护微功耗比较器和提高微功耗比较器的稳定性。

背景技术

比较器是芯片集成电路中的常用器件,微功耗比较器通常指电源电流在微安级甚至纳安级的比较器。微功耗比较器的输出级一般采用反相器结构,包括一个PMOS管和一个NMOS的组合。如果比较器的前级信号为全电压范围的逻辑信号,那么就会存在比较器输出级的PMOS管与NMOS管同时导通的瞬间,此时瞬时的电流较大。较大的瞬态电流对微功耗比较器是不能忍受的,有可能导致微功耗比较器受损,或者破坏微功耗比较器的稳定性。本发明人认为,如果在输出级的PMOS管连接结构中增加第一反相器和在输出级的NMOS管的连接结构中增加第二反相器,能够利用双反相器的延时效应使得输出端PMOS管Mpout和输出端NMOS管Mnout不出现同时导通的状态,从而避免因Mpout与Mnout同时导通的瞬间而出现的比较器输出级的较大瞬时输出电流,以保护微功耗比较器和提高微功耗比较器的稳定性。有鉴于此,本发明人完成了本发明。

发明内容

本发明针对现有技术中存在的缺陷或不足,提供一种能够减小微功耗比较器输出级瞬态电流的控制电路,通过在输出级的PMOS管连接结构中增加第一反相器和在输出级的NMOS管的连接结构中增加第二反相器,能够利用双反相器的延时效应使得输出端PMOS管Mpout和输出端NMOS管Mnout不出现同时导通的状态,从而避免因Mpout与Mnout同时导通的瞬间而出现的比较器输出级的较大瞬时输出电流,以保护微功耗比较器和提高微功耗比较器的稳定性。

本发明的技术方案如下:

一种能够减小微功耗比较器输出级瞬态电流的控制电路,其特征在于,包括第一反相器和第二反相器,所述第一反相器的输入端分别连接输出端PMOS管的栅极、第三PMOS管的漏极和第三NMOS管的漏极,所述输出端PMOS管的漏极与输出端NMOS管的漏极互连后连接输出信号端,所述输出端PMOS管的源极和所述第三PMOS管的源极均连接电源电压端,所述第三NMOS管的栅极连接所述第二反相器的输出端,所述第二反相器的输入端分别连接所述输出端NMOS管的栅极、第一NMOS管的漏极和第二PMOS管的漏极,所述第二PMOS管的栅极连接所述第一反相器的输出端,所述第一NMOS管的源极和所述输出端NMOS管的源极均连接接地端,所述第二PMOS管的源极连接第一PMOS管的漏极,所述第一PMOS管的源极连接电源电压端,所述第一PMOS管的栅极与所述第三PMOS管的栅极互连后连接输入信号端,所述第三NMOS管的源极连接第二NMOS管的漏极,所述第二NMOS管的源极连接接地端,所述第二NMOS管的栅极与所述第一NMOS管的栅极互连后连接所述输入信号端。

所述第一反相器的电源接点连接电源电压端,所述第一反相器的接地点连接接地端。

所述第二反相器的电源接点连接电源电压端,所述第二反相器的接地点连接接地端。

本发明的技术效果如下:本发明一种能够减小微功耗比较器输出级瞬态电流的控制电路,通过针对输出端PMOS管和输出端NMOS管增加双反相器信号延时结构,能够利用双反相器的延时效应使得输出端PMOS管Mpout和输出端NMOS管Mnout不出现同时导通的状态,从而避免因Mpout与Mnout同时导通的瞬间而出现的比较器输出级的较大瞬时输出电流,以保护微功耗比较器和提高微功耗比较器的稳定性。

附图说明

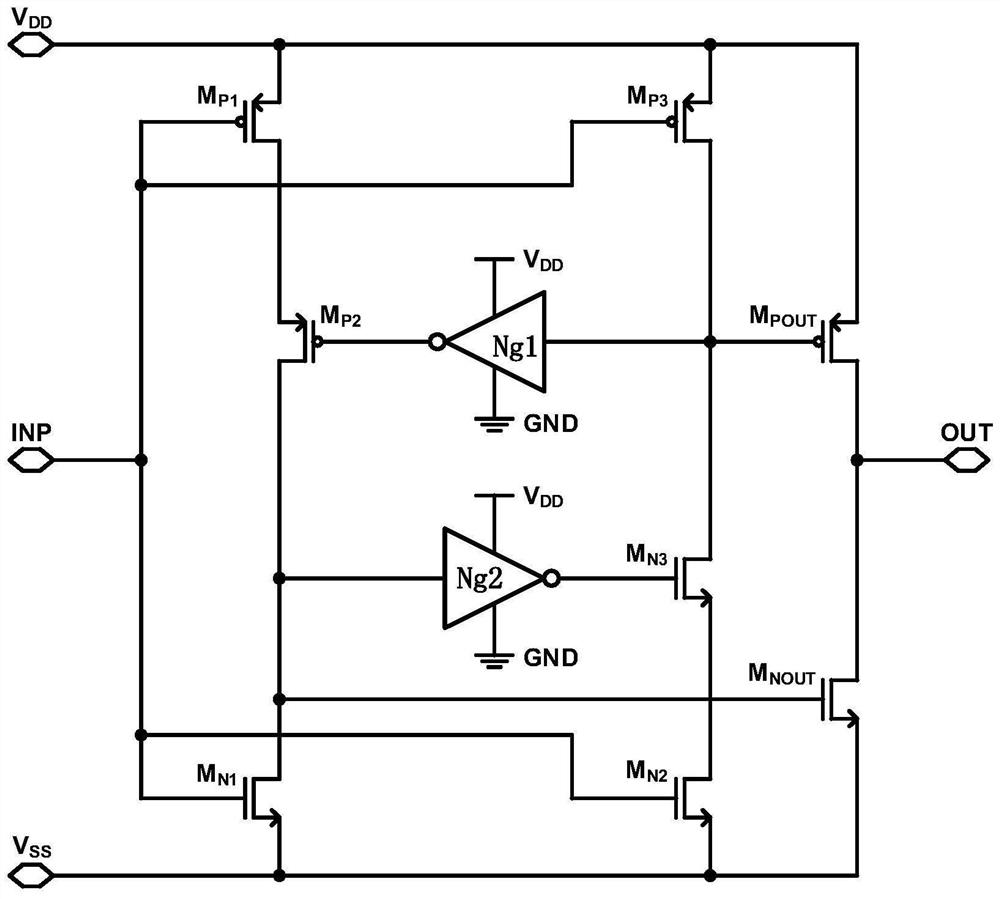

图1是实施本发明一种能够减小微功耗比较器输出级瞬态电流的控制电路结构示意图。

附图标记列示如下:VDD-电源电压端或电源电压;VSS-接地端;INP-输入信号端或输入信号;GND-接地端;OUT-输出信号端;Mpout-输出端PMOS管;Mnout-输出端NMOS管;Mp1~Mp3-第一至第三PMOS管;Mn1~Mn3-第一至第三NMOS管;Ng1-第一反相器;Ng2-第二反相器。

具体实施方式

下面结合附图(图1)对本发明进行说明。

图1是实施本发明一种能够减小微功耗比较器输出级瞬态电流的控制电路结构示意图。如图1所示,一种能够减小微功耗比较器输出级瞬态电流的控制电路,包括第一反相器Ng1和第二反相器Ng2,所述第一反相器Ng1的输入端分别连接输出端PMOS管Mpout的栅极、第三PMOS管Mp3的漏极和第三NMOS管Mn3的漏极,所述输出端PMOS管Mpout的漏极与输出端NMOS管Mnout的漏极互连后连接输出信号端OUT,所述输出端PMOS管Mpout的源极和所述第三PMOS管Mp3的源极均连接电源电压端VDD,所述第三NMOS管Mn3的栅极连接所述第二反相器Ng2的输出端,所述第二反相器Ng2的输入端分别连接所述输出端NMOS管Mnout的栅极、第一NMOS管Mn1的漏极和第二PMOS管Mp2的漏极,所述第二PMOS管Mp2的栅极连接所述第一反相器Ng1的输出端,所述第一NMOS管Mn1的源极和所述输出端NMOS管Mnout的源极均连接接地端VSS,所述第二PMOS管Mp2的源极连接第一PMOS管Mp1的漏极,所述第一PMOS管Mp1的源极连接电源电压端VDD,所述第一PMOS管Mp1的栅极与所述第三PMOS管Mp3的栅极互连后连接输入信号端INP,所述第三NMOS管Mn3的源极连接第二NMOS管Mn2的漏极,所述第二NMOS管Mn2的源极连接接地端VSS,所述第二NMOS管Mn2的栅极与所述第一NMOS管Mn1的栅极互连后连接所述输入信号端INP。所述第一反相器Ng1的电源接点连接电源电压端VDD,所述第一反相器Ng1的接地点连接接地端GND。所述第二反相器Ng2的电源接点连接电源电压端VDD,所述第二反相器Ng2的接地点连接接地端GND。

如图1所示,INP为输入,经过电路变为OUT输出信号。Ng1与Ng2为反相器。电路简单原理如下,首先假设INP信号为高,那么Mp1、Mp3关断,Mn1、Mn2打开,Mnout的ngate为低,Mpout的pgate为低,OUT为高。当INP从高到低的过程中,由于pgate状态为低,所以Mp2为关断状态,同理ngate为低Mn3导通。INP从高到低转换中,此时Mp3与Mn2构成反相器结构,当INP信号降低到一定程度,pgate反转从低到高,此时由于反相器Ng1延时的效应,导致Mp2仍然处于关闭状态,ngate仍处于低,输出Mpout与Mnout都处于关闭状态。反相器Ng1的延时效应过后Mp2导通ngate变高,此时Mnout导通,OUT为低。同理当INP信号从低到高的过程中由于反相器Ng2的延时效应,会使ngate先变低而此时pgate仍为高状态,输出Mpout与Mnout都处于关闭状态。反相器Ng2的延时效应过后Mn3导通pgate变低,此时Mpout导通,OUT变高。通过调整Ng1与Ng2反相器的延时效应,即可控制输出Mpout与Mnout不出现同时导通的状态,这会大大降低输出瞬时的电流,也就是说,微功耗比较器输出级瞬态电流能够得到有效控制。

在此指明,以上叙述有助于本领域技术人员理解本发明创造,但并非限制本发明创造的保护范围。任何没有脱离本发明创造实质内容的对以上叙述的等同替换、修饰改进和/或删繁从简而进行的实施,均落入本发明创造的保护范围。

- 一种能够减小微功耗比较器输出级瞬态电流的控制电路

- 一种能够减小微功耗比较器输出级瞬态电流的控制电路