半导体结构及其形成方法

文献发布时间:2023-06-19 11:21:00

技术领域

本申请涉及半导体制造技术领域,尤其涉及一种半导体结构及其形成方法。

背景技术

在半导体制造过程中,为了防止潮气或灰尘进入芯片,通常在衬底上围绕芯片设置密封环。将密封环接地还能够频率来自芯片外的静电干扰。

然而,由于密封环通常都设置在衬底上方,故其无法在芯片切割过程中阻止外部应力作用至衬底内,以致于对位于衬底内的半导体结构带来机械损伤。

因此,需要一种能够防止衬底在芯片切割过程受到机械损伤的半导体结构及其形成方法。

发明内容

鉴于以上所述现有技术的缺点,本申请的目的在于提供一种能够在不增加额外的工艺步骤的情况下防止衬底在芯片切割过程受到机械损伤的半导体结构及其形成方法。

本申请的一个方面提供了一种半导体结构,其包括半导体衬底、第一沟槽结构和第二沟槽结构,所述第一沟槽结构形成在所述半导体衬底中,用于形成沟槽式电容器,所述第二沟槽结构形成在所述半导体衬底中并环绕所述第一沟槽结构设置。

在一些实施例中,所述第二沟槽结构包括一个或多个沟槽,所述多个沟槽互相环绕设置,且所述所述多个沟槽中的至少一个结构连续。

在一些实施例中,所述第二沟槽结构包括一个或多个结构不连续的沟槽,所述多个沟槽互相环绕设置。

在一些实施例中,所述多个结构不连续的沟槽都包括缺口,所述缺口以相互交错的方式设置。

在一些实施例中,在所述多个结构不连续的沟槽中,相邻沟槽的间距为2μm至5μm。

在一些实施例中,所述第二沟槽结构中的每个沟槽的深度为25μm至35μm。

在一些实施例中,所述第二沟槽结构中的每个沟槽的宽度为0.8μm至1.2μm。

在一些实施例中,所述第二沟槽结构与所述第一沟槽结构的间距为8μm至12μm。

在一些实施例中,所述的半导体结构还包括切割道,所述切割道形成在所述半导体衬底中并环绕所述第二沟槽结构,所述第二沟槽结构与所述切割道的间距为8μm至12μm。

本申请的一个方面提供了一种半导体结构的形成方法,其包括:提供半导体衬底;以及刻蚀所述半导体衬底,同时形成第一沟槽结构和第二沟槽结构,其中,所述第一沟槽结构用于形成沟槽式电容器,所述第二沟槽结构环绕所述第一沟槽结构设置。

在一些实施例中,所述第二沟槽结构包括一个或多个沟槽,所述多个沟槽互相环绕设置,且所述所述多个沟槽中的至少一个结构连续。

在一些实施例中,所述第二沟槽结构包括一个或多个结构不连续的沟槽,所述多个沟槽互相环绕设置。

在一些实施例中,所述多个结构不连续的沟槽都包括缺口,所述缺口以相互交错的方式设置。

在一些实施例中,在所述多个结构不连续的沟槽中,相邻沟槽的间距为2μm至5μm。

在一些实施例中,所述第二沟槽结构与所述第一沟槽结构的间距为8μm至12μm。

在一些实施例中,所述第二沟槽结构中的每个沟槽的深度为25μm至35μm。

在一些实施例中,所述第二沟槽结构中的每个沟槽的宽度为0.8μm至1.2μm。

在一些实施例中,所述的半导体结构的形成方法还包括:刻蚀所述半导体衬底,以形成切割道,其中,所述切割道环绕所述第二沟槽结构设置,所述第二沟槽结构与所述切割道的间距为8μm至12μm。

本申请所提出半导体结构及其形成方法通过在形成用于设置电容器的沟槽的同时形成用于阻隔外部机械损伤的沟槽,以最小的代价(即,无需新增任何工艺步骤)实现了在芯片切割时防止衬底受到机械性损伤的技术效果。

附图说明

以下附图详细描述了本申请中披露的示例性实施例。其中相同的附图标记在附图的若干视图中表示类似的结构。本领域的一般技术人员将理解这些实施例是非限制性的、示例性的实施例,附图仅用于说明和描述的目的,并不旨在限制本公开的范围,其他方式的实施例也可能同样的完成本申请中的发明意图。应当理解,附图未按比例绘制。其中:

图1为一种半导体结构的示意图;

图2为根据本申请实施例的半导体结构的形成方法的流程图;

图3至图6为根据本申请实施例的半导体结构的形成过程的结构示意图;

图7a为根据本申请实施例的半导体结构的沟槽结构的示意图;

图7b为本申请实施例的沿图7a中的线A-A截取的剖视图;

图7c为根据本申请另一实施例的沿图7a中的线A-A截取的剖视图;

图8a为根据本申请实施例的半导体结构的沟槽结构的示意图;

图8b为根据本申请实施例的沿图8a中的线B-B截取的剖视图;

图8c为根据本申请另一实施例的沿图8a中的线B-B截取的剖视图。

具体实施方式

以下描述提供了本申请的特定应用场景和要求,目的是使本领域技术人员能够制造和使用本申请中的内容。对于本领域技术人员来说,对所公开的实施例的各种局部修改是显而易见的,并且在不脱离本公开的精神和范围的情况下,可以将这里定义的一般原理应用于其他实施例和应用。因此,本公开不限于所示的实施例,而是与权利要求一致的最宽范围。

除非另有说明,或如根据用途环境可显而易见,将给本文中使用的任何术语、缩略语、首字母缩写或科学符号及记号赋予本发明最接近地归属的技术学科中的其普通含义。可在本文中呈现的说明通篇中使用以下术语、缩略语及首字母缩写且通常应赋予其以下含义,除非本文中所述的其它说明对其加以反驳或详尽说明。

应理解,当称例如层、区或衬底的元件“在另一元件上”时,其可直接在另一元件上,或者也可存在介入元件。相反,当将元件称为“直接在另一元件上”时,不存在介入元件。还应理解,当元件称为“连接”或“耦合”到另一元件时,其可直接连接或耦合到另一元件,或者也可存在介入元件。相反,当元件称为“直接连接”或“直接耦合”到另一元件时,不存在介入元件。

下面结合实施例和附图对本发明技术方案进行详细说明。

如图1所示,一种半导体结构包括半导体衬底10、形成于半导体衬底10中的沟槽20、形成于沟槽20中的电容器30、连接电容器的接触层50、连接接触层50的金属互连层60、位于半导体衬底10上方的密封环40。

在这种半导体结构中,虽然设置了密封环40以保证衬底上方的器件不受潮气、灰尘、静电等外部干扰,但是在芯片切割过程中,密封环40无法阻止外部应力作用至衬底内。例如,由于外部应力而产生的裂缝70可能延伸至衬底内,从而对位于衬底内的电容器30造成损伤。

为了解决上述问题,本发明实施例提供一种半导体结构的形成方法,如图2所示,包括以下步骤:

步骤S102:提供半导体衬底;

步骤S104:刻蚀所述半导体衬底,同时形成第一沟槽结构和第二沟槽结构,其中,所述第一沟槽结构用于形成沟槽式电容器,所述第二沟槽结构环绕所述第一沟槽结构设置。

下面结合图3至图6对上述各个步骤进行详细说明。应注意,以其他顺序执行以上和以下步骤的方法也落入本公开的保护范围。

如图3所示,提供半导体衬底100。

半导体衬底100的材料可以为硅(Si)、锗(Ge)、硅锗(GeSi)、碳化硅(SiC)、绝缘体上硅(SOI)、绝缘体上锗(GOI),或者其它的材料,例如砷化镓等III-V族化合物。半导体衬底100的材质可以是单晶硅、多晶硅、非晶硅中的一种。半导体衬底100的材质也可以是硅锗化合物。半导体衬底100还可以是绝缘体上硅结构或硅上外延层结构。在半导体衬底100中,可形成有半导体器件(未示出),例如具有栅极、源极和漏极的金属氧化物半导体器件。

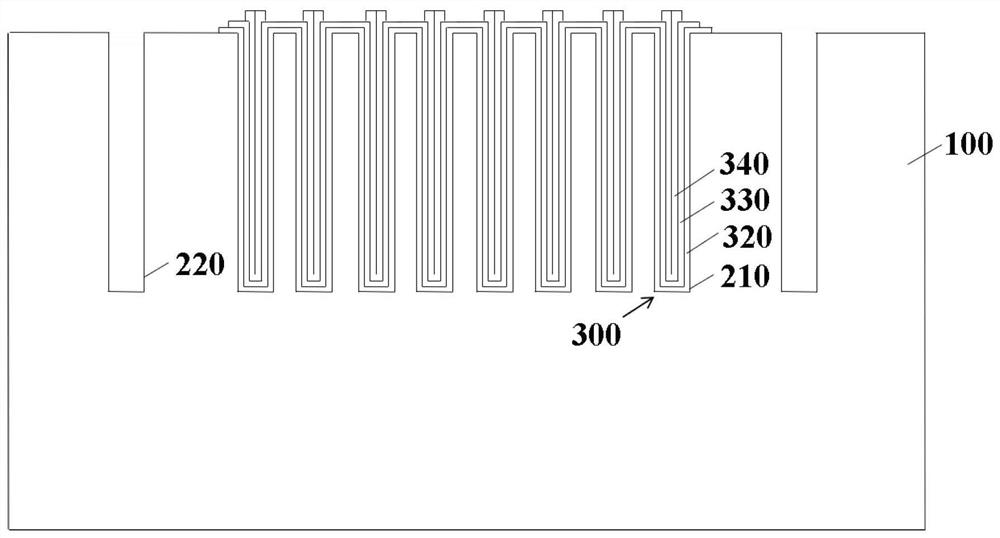

如图4所示,刻蚀半导体衬底100,同时形成第一沟槽结构210和第二沟槽结构220。

第一沟槽结构210可包含多个沟槽,所述多个沟槽中的每一个的深度为25μm至35μm,所述多个沟槽中的每一个的宽度为0.8μm至2.0μm,例如,1.0μm、1.2μm、1.5μm、1.8μm等。第二沟槽结构220包含一个或多个沟槽,所述一个或多个沟槽中的每一个的深度D为25μm至35μm,所述一个或多个沟槽中的每一个的宽度W为0.8μm至1.2μm。第一沟槽结构210与第二沟槽结构220的间距为8μm至12μm。第二沟槽结构220被配置为在半导体衬底100被切割时防止第一沟槽结构210受到外部应力导致的机械性损伤。具体地,当沿着切割道(scribeline)切割半导体芯片时,切割力可能导致半导体衬底100中出现裂缝(如图1中所示),第二沟槽结构220的存在能够防止裂缝进一步延伸至第一沟槽结构210,从而确保半导体衬底100中的器件的安全性。

在本实施例中,第一沟槽结构210和第二沟槽结构220通过同一蚀刻工艺(例如,干法蚀刻或湿法蚀刻)形成,从而能够以最小的代价(即,无需新增任何工艺步骤)实现了保护半导体衬底的技术效果。

如图5所示,在一些实施例中,本申请的半导体结构的形成方法还可包括:在第一沟槽结构210中形成沟槽式电容器300。

沟槽式电容器300包括下电极320、极间层330和上电极340。

在第一沟槽结构210中形成沟槽式电容器300的具体步骤如下。

首先,在第一沟槽结构210中的每一个沟槽的底壁和侧壁以及半导体衬底100上形成下电极320。下电极320可包括依次层叠的第一金属氮化物层、金属层及第二金属氮化物层,其中,所述第一金属氮化物层可以为氮化钛或氮化钽,所述金属层可以为金属铝或金属铜,所述第二金属氮化物层可以为氮化钛或氮化钽。随后,在下电极320上形成极间层330。极间层330的材料可以为二氧化硅、氮化硅、氮氧化硅等其他介质材料。最后,在极间层330上形成上电极340。上电极340的材料可以与下电极320相同或相似。下电极320、极间层330和上电极340均可通过原子层沉积(ALD)技术来进行沉积。

在一些实施例中,可以以相同的方式在第一沟槽结构210中的每一个沟槽中堆叠多层沟槽式电容器300。

如图6所示,在一些实施例中,本申请的半导体结构的形成方法还可包括:在沟槽式电容器300上方形成接触层500;在接触层500上形成金属互连层600;以及在第二沟槽结构220上形成密封环400。

在一些实施例中,本申请的半导体结构的形成方法还可包括:刻蚀半导体衬底100,以形成切割道(未示出),其中,所述切割道环绕第二沟槽结构220,第二沟槽结构220与所述切割道的间距为8μm至12μm。

图7a为根据本申请实施例的半导体结构的沟槽结构的示意图,并且图7b为本申请一实施例的沿图7a中的线A-A截取的剖视图。

在图7a和图7b所示的实施例中,第二沟槽结构220仅包含一个沟槽,该沟槽的结构连续,即该沟槽具有连续的环形结构(沿垂直于半导体衬底100的方向观察)。在本申请中,结构连续指的是不存在任何断点或缺口的结构。当该沟槽的结构连续时,能够为位于半导体衬底100内的第一沟槽结构210提供全方位的防护。在一些实施例中,第二沟槽结构220可包含多个沟槽,所述多个沟槽中的至少一个结构连续。在一些实施例中,可以将多个沟槽设置为互相环绕,以获得更好的纵深防护效果。在一些实施例中,还可以通过增加沟槽的宽度和/或深度来提高防护效果。

图7c为根据本申请另一实施例的沿图7a中的线A-A截取的剖视图。

在图7c所示的实施例中,第二沟槽结构220仅包含一个沟槽,该沟槽的结构不连续。如图所示,该沟槽的环形截面上存在断点或缺口225。在本申请中,结构不连续指的是存在一个或多个断点或缺口的结构。当第一沟槽结构210的密度不大时,即使第二沟槽结构220的沟槽构成一个不连续的环形,其也能够为位于半导体衬底100内的第一沟槽结构210提供足够的抗机械损伤的效果。在一些实施例中,第二沟槽结构220可包含一个或多个结构不连续的沟槽。在一些实施例中,第二沟槽结构220可以既包含结构连续的沟槽,也包含结构不连续的沟槽。虽然图7c中的结构不连续的沟槽由四个矩形部分形成,但应注意,结构不连续的沟槽中的一个或多个部分可以是正方形、矩形、圆形、椭圆形、菱形、三角形、梯形、波浪形、五边形、六边形、其他多边形和/或它们的组合。

图8a为根据本申请实施例的半导体结构的沟槽结构的示意图,并且图8b为根据本申请实施例的沿图8a中的线B-B截取的剖视图。

在图8a和图8b所示的实施例中,第二沟槽结构220包括两个第一沟槽221和环绕第一沟槽221设置的第二沟槽222。第一沟槽221和第二沟槽222均结构连续,从而能够为第一沟槽结构210提供双重保护。在一些实施例中,第二沟槽结构220可包括三个或更多个结构连续的沟槽,从而能够为第一沟槽结构210提供多重保护。在一些实施例中,第二沟槽结构220可包括两个结构连续的沟槽和一个结构不连续的沟槽。在一些实施例中,第二沟槽结构220可包括两个结构不连续的沟槽和一个结构连续的沟槽。在本实施例中,相邻沟槽(例如第一沟槽221和第二沟槽222)的间距Y可以为2μm至5μm。在一些实施例中,还可以通过增加相邻沟槽的间距Y、沟槽的宽度和/或沟槽的深度来提高防护效果。

图8c为根据本申请另一实施例的沿图8a中的线B-B截取的剖视图。

在图8c所示的实施例中,第二沟槽结构220包括两个第一沟槽221和环绕第一沟槽221设置的第二沟槽222。第一沟槽221和第二沟槽222均结构不连续。第一沟槽221的缺口227与第二沟槽222的缺口226以相互交错的方式设置,从而能够有效地阻挡外来裂缝延伸至第一沟槽结构210。具体地,即使外来的裂缝延伸通过缺口226,从而突破了第二沟槽222形成的防线,其也会被第一沟槽221阻挡。在一些实施例中,为了使布局更加紧凑,可以仅在一个方向(例如,半导体结构密集的方向)设置保护沟槽。在一些实施例中,第二沟槽结构220可包括三个或更多个结构不连续的沟槽。

虽然图8c中的结构不连续的沟槽由多个矩形部分形成,但应注意,不连续的环形沟槽中的一个或多个部分可以是正方形、矩形、圆形、椭圆形、菱形、三角形、梯形、波浪形、五边形、六边形、其他多边形和/或它们的组合。

综上所述,在阅读本详细公开内容之后,本领域技术人员可以明白,前述详细公开内容可以仅以示例的方式呈现,并且可以不是限制性的。尽管这里没有明确说明,本领域技术人员可以理解本申请意图囊括对实施例的各种合理改变,改进和修改。这些改变,改进和修改旨在由本公开提出,并且在本公开的示例性实施例的精神和范围内。

- 半导体封装结构、半导体封装结构的形成方法以及半导体组装结构的形成方法

- 栅极结构的形成方法、半导体器件的形成方法以及半导体器件