存储器系统的控制方法

文献发布时间:2023-06-19 11:22:42

技术领域

本发明关于一种存储器系统的控制方法,尤指一种传送存取指令的时间长度基本上为时钟信号的时钟周期的1.5倍的存储器系统的控制方法。

背景技术

随着电子产品及通讯相关应用的需求不断增长,存储器已扮演关键角色。为了在相同时间内可存取更多数据,系统对数据存取的带宽的要求持续增加。

然而,对于访问存储器的接口而言,存储器装置端的时间余量(time margin)议题已成为集成电路及印刷电路板的设计挑战。除了提高存储器存取的速度,也须考虑存储器存取的正确性,以避免误存取发生。因此,本领域仍欠缺适宜的解决方案,以兼顾存取存储器的速度及正确性。

发明内容

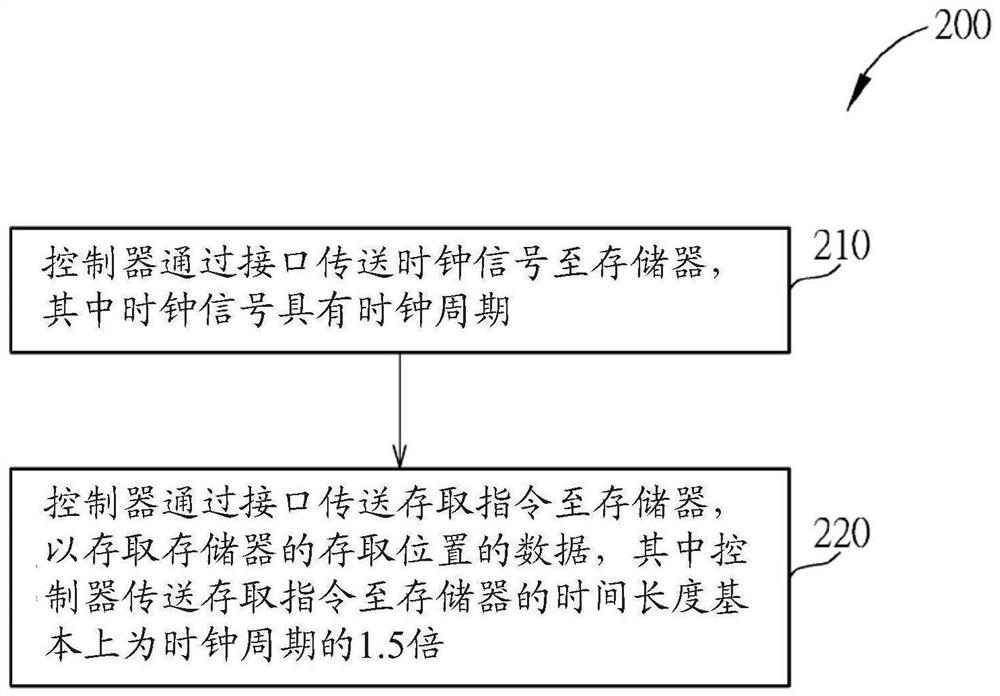

实施例提供一种存储器系统的控制方法。该存储器系统包含控制器,耦合于该控制器的接口,和存储器,所述存储器通过该接口耦合于该控制器。该控制方法包含该控制器通过该接口传送时钟信号至该存储器,其中该时钟信号具有一时钟周期;以及该控制器通过该接口传送存取指令至该存储器,以存取该存储器的存取位置的数据,其中该控制器传送该存取指令至该存储器的时间长度基本上为该时钟周期的1.5倍。

附图说明

图1是实施例中,存储器系统的示意图。

图2是图1的控制方法的流程图。

图3是图1的实施例中,传送信号和指令的示意图。

图4是另一实施例中,图1的控制系统的示意图。

图5至图7是图4的实施例中,传送信号和指令的示意图。

具体实施方式

本文所述的长度是时间长度,且本文所述的指令的长度是传送指令的时间长度。

用以控制存储器的指令的长度,为存储器控制领域的重要参数。举例而言,若将用以控制存储器的指令的时间长度,设定为一个时钟周期,会导致时间余量不足,而使信号的失真程度偏高,此情况下,从眼图(eye diagram)可见其张开程度不足。然而,若将每指令的长度设定更大,例如两个时钟周期,虽可有效增加时间余量,且可于眼图测得较大的张开程度,但会导致一段时间内可发送的指令数量减低,从而使操作速度减慢。此外,指令可分为存取指令(access command)和激活指令(active command)两种,若考虑到存取指令之间还要传送激活指令,将造成存取指令更被延迟。

根据本发明的一个实施例,用于读取、写入的指令为存取指令,其他种类的指令为激活指令。每种指令可对应于多个信号的逻辑状态的组合,其可规划于真值表。本文所述的存取指令,举例来说,可为列地址选通(column address strobe,简称CAS)指令。举例而言,所述列地址选通(CAS)指令可用以存取存储器的储存体地址(bank address),即位于行(row)、列(column)的数据。本文所述的激活指令,举例来说,可为存取指令以外的指令,例如预充电(precharge,简称PRE)指令、模式寄存器集(mode register set,简称MRS)指令、行地址选通(row address strobe,简称RAS)指令和/或刷新(refresh,简称REF)指令等。举例而言,所述行地址选通(RAS)指令可用以激活(activate)存储器的存储体行(bank row),即页(page)。

图1是一个实施例中存储器系统100的示意图。图2是图1的控制方法200的流程图。

存储器系统100包含控制器110、接口120和存储器130。接口120耦合于控制器110。存储器130通过接口120耦合于控制器110。

举例而言,控制器110可为存储器控制器(memory controller,简称MC)。存储器130可为双倍数据率(double data rate,简称DDR)存储器。接口120可为双倍数据率物理层接口(double data rate physical interface,简称DFI)。

根据一个实施例,存储器系统100可包含单控制装置、单接口及单存储装置。根据另一实施例,存储器系统100可包含多个控制装置、单接口和多个存储装置,因此,控制器110可包含多个控制装置,存储器130可包含多个存储装置,如后文所述(例如图4)。

如图1和图2所示,控制方法200包含至少以下步骤。

步骤210:控制器110通过接口120传送时钟信号CK至存储器130,其中时钟信号CK具有时钟周期Tck;以及

步骤220:控制器110通过接口120传送存取指令至存储器130,以存取存储器130的存取位置ADD1的数据,其中控制器110传送存取指令至存储器的时间长度Tcmd基本上为时钟周期Tck的1.5倍。

图3是图1的实施例中,传送信号及指令的示意图。图3中,由左至右的水平方向是时间轴。图3可以是单控制装置通过单接口控制单存储装置的信号图。图3中,是以列到列延迟时间(column to column delay,常简称为tCCD)为6个时钟周期的情况举例说明。图3的指令信号CMD可描述控制器110传送的指令,其中,指令信号CMD基本上可对应于多个信号,以对应于真值表的规划。同理,后文提及的指令信号CMD1和CMD2基本上可对应于多个信号。

如图3所示,存取指令C1的长度基本上可为1.5个时钟周期Tck。控制器110还可通过接口120传送存取指令C2至存储器130,以存取存储器130的存取位置ADD2的数据。其中,控制器110传送存取指令C2至存储器130的时间长度基本上为时钟周期Tck的1.5倍。图3中,传送存取指令C1可先于传送存取指令C2。同理,传送存取指令C2后,控制器110还可通过接口120传送存取指令C3、C4及C5等至存储器130。

如图3所示,控制器110还可通过接口120传送激活指令CI1至存储器130,传送激活指令CI1的时间可在传送存取指令C1及存取指令C2的时间之间。同理,在传送存取指令C2及存取指令C3之间,控制器110还可通过接口120传送激活指令CI2、CI3及CI4至存储器130。此外,控制器110还可传送激活指令CI5及CI6。在两个指令之间,若无法再安插指令,则可为空闲状态(IDLE)。根据一个实施例,激活指令的长度基本上可为时钟周期Tck的1.5倍。

如图3所示,控制器110还可通过接口120传送芯片选取信号CS至存储器130。其中,芯片选取信号CS具有有效脉冲P

芯片选取信号CS可用以选取存储器130对应的芯片及选取传送的指令。当时钟信号CK位于特定的信号沿(上升沿或下降沿),且芯片选取信号CS位于有效脉冲P

举例而言,在时钟信号CK位于上升沿e1时,因此时芯片选取信号CS位于有效脉冲P

如图3所示,由于将存取指令的长度设定为1.5倍时钟周期Tck,在存取指令C2和C3之间,因指令的长度许可,可在时间轴安排传送三个激活指令(例如CI2、CI3和CI4)。此情况下,眼图的开启程度,可优于存取指令的长度仅一倍时钟周期Tck的情况。此外,在存取指令的长度为两倍时钟周期Tck的情况下,在两存取指令之间,最多只可传送两个激活指令,而无法传送三个激活指令。因此,相较于存取指令的长度为一个或两个时钟周期的情况,由于将存取指令的长度设定为时钟周期Tck的1.5倍,可兼顾操作速度及存取的正确性,也可测得足够开启的眼图。

图4是另一实施例中,图1的控制系统100的示意图。相似于图1,控制系统100也包含控制器110、接口120及存储器130。然而,图4中,控制器110包含控制装置1101和1102,且存储器130包含存储装置1301和1302。换言之,图4为多个控制装置,通过单接口控制多个存储装置的实施例。举例而言,图4中,存储装置1301和1302可为不同芯片的双倍数据率存储装置。控制装置1101和1102可用以分别控制存储装置1301和1302。

图5至图7是图4的实施例中传送信号和指令的示意图。图5的时钟信号CK如图3,具有时钟周期Tck。图5的指令信号CMD1表示控制装置1101传送至存储装置1301的指令,且指令信号CMD2表示控制装置1102传送至存储装置1302的指令。

当芯片选取信号CS1位于有效脉冲P

如图5所示,当时钟信号CK位于上升沿e11、e12、e13、e14及e15时,因芯片选取信号CS1位于有效脉冲P

如图4和图5所示,若将存取指令C11和C21视为第一存取指令和第二存取指令,则第一存取指令所述的存取位置ADD51位于存储装置1301,且第二存取指令所述的存取位置ADD52位于存储装置1302。第一存取指令可由控制装置1101传送至存储器130,以及第二存取指令可由控制装置1102传送至存储器130。

图5是仅传送存取指令的情况。相较于图5,图6进一步描述指令信号CMD2还包含激活指令的情况。换言之,图5是描述未考虑激活指令的情况,而图6进一步描述控制装置1102可传送激活指令的情况。相较于图5,如图6所示,在存取指令C22和C23之间还传送了激活指令CI26。因此,从图5到图6,对应于选取存取指令C13的上升沿e13基本上只被延迟了一个时钟周期Tck。

相较于图5,图7描述指令信号CMD1和CMD2还包含激活指令的情况。换言之,图7进一步描述控制装置1101和1102可传送激活指令的情况。相较于图6,如图7所示,在存取指令C12和C13之间还传送了激活指令CI17。因此,从图5到图7,对应于选取存取指令C13的上升沿e13基本上只被延迟了两个时钟周期Tck。

在每指令的长度为两个时钟周期Tck的情况下,当指令信号CMD1和CMD2包含激活指令,对应于同一存取指令的时钟信号的上升沿会被延迟四个时钟周期Tck。因此,以图7为例,将指令的长度由两个时钟周期Tck调整为1.5个时钟周期Tck,可将存取指令的延迟时间从四个时钟周期Tck降低为两个时钟周期Tck,故可减少存取指令的延迟时间达50%,且可测得比指令长度仅为一个时钟周期Tck的情况更佳的眼图。

综上,由于将指令长度调整为时钟周期的1.5倍,本发明的实施例所提供的存储器系统及控制方法,可兼顾操作速度及存取的正确性,且可在眼图测得足够的开启程度,因此,对于解决处理本领域的问题,带来了很大的帮助。

以上所述仅为本发明的较佳实施例,凡依申请权利要求书的范围所做的任何变化与改进,都属于本发明的保护范围。

符号说明

100 存储器系统

110 控制器

1101、1102 控制装置

120 接口

130 存储器

1301、1302 存储装置

ADD1、ADD2、ADD51、ADD52 存取位置

200 控制方法

210、220 步骤

CK 时钟信号

Tck 时钟周期

Tcmd 时间长度

CS、CS1、CS2 芯片选取信号

P

P

C1、C2、C3、C4、C5、C11、C12、C13、 存取指令

C14、C15、C21、C22、C23、C24、C25

CI1、CI2、CI3、CI4、CI5、CI6、CI26、CI17 激活指令

IDLE 空闲状态

e1、e2、e3、e4、e5、e11、e12、e13、e14、 上升沿

e15、e21、e22、e23、e24、e25

CMD、CMD1、CMD2 指令信号

- 存储器装置、主机装置、存储器系统、存储器装置控制方法、主机装置控制方法以及存储器系统控制方法

- 存储器控制器、存储器系统及存储器系统的控制方法