底部钉扎SOT-MRAM位结构和制造方法

文献发布时间:2023-06-19 11:27:38

本申请是2016年10月24日所提出的申请号为201610939473.7、发明名称为“底部钉扎SOT-MRAM位结构和制造方法”的发明专利申请的分案申请。

技术领域

本公开的实施例总体上涉及数据储存和计算机存储系统,更具体地涉及自旋-轨道转矩磁阻随机存取存储器(SOT-MRAM)芯片结构。

背景技术

计算机的核心是磁记录装置,其通常可包括旋转磁介质或固态介质装置。当今存在许多不同的存储技术来存储在计算系统中使用的信息。总体上,这些不同存储技术可以分为两个主要类别:易失性存储器和非易失性存储器。易失性存储器一般指的是需要电能来保留存储的数据的计算机存储器类型。另一方面,非易失性存储器一般指的是不需要电能来保留存储的数据的计算机存储器类型。易失性存储器的示例可包括某些类型的随机存取存储器(RAM),比如动态RAM(DRAM)和静态RAM(SRAM)。非易失性存储器的示例可包括只读存储器(ROM)、磁阻RAM(MRAM)和闪存(比如NOR和NAND闪存)等。

近些年,在大容量储存器和存储应用中需要更高密度的装置,其维持比较低的每位成本。当今,一般在计算行业中占主导地位的存储技术是DRAM和NAND闪存,然而,这些存储技术不能够解决下一代计算系统的当前和未来容量需求。

最近,出现的许多技术得到持续关注,作为下一代存储器的潜在竞争者。一个这种存储技术是磁阻随机存取存储器(MRAM)。MRAM提供了快速该部时间、近乎无限的读/写耐久性、耐辐射性和高储存密度。与常规RAM芯片技术不同,MRAM数据不储存为电荷,而是替代地使用磁元件的磁极化状态储存数据位。这些元件由两个磁极化层(由薄绝缘层分隔开)形成,每一层可维持磁极化场,它们一起形成磁隧道结(MTJ)结构。包括MTJ存储元件的MRAM单元可设计用于MTJ层结构相对于膜表面的面内或垂直极化。两层之一(指的是固定或参考层)的磁化固定并设定为特定极性,例如通过将该层耦合到反铁磁体;第二层(指的是自由层)的极化在外部写入机构(比如强磁场或自旋极化电流)的影响下自由地旋转(其以MRAM形式用作自旋扭矩传输或STT-MRAM)。

然而,由于驱动足够量的电流来切换通过MTJ(包括通过阻挡层),STT-MRAM装置中的MTJ存储元件会受到磨损的影响。通常,需要大量电流来切换单元的状态。随着时间的过去,由于大量电流,阻挡层破裂,从而导致MTJ失效。

因此,在本领域中需要一种改进的MRAM装置。

发明内容

本公开的实施例总体上涉及数据储存和计算机存储系统,更具体地涉及SOT-MRAM芯片结构。SOT-MRAM芯片结构包括多个引线、多个存储器单元以及多个晶体管。引线可以由具有大自旋-轨道耦合强度和高电阻率的材料制成。每个单独的引线可包括多个第一部分和与第一部分区分开的多个第二部分。第二部分的电阻率小于第一部分的电阻率,所以引线的总电阻率减小,导致改进的功率效率和信噪比。

在一个实施例中,SOT-MRAM芯片结构包括由具有Pt、Ta、W、Hf、Ir、CuBi、CuIr或AuW的材料制成的多个引线、耦合到多个引线中的每个引线的多个存储器单元以及多个晶体管。每个晶体管耦合到多个存储器单元的对应存储器单元。

在另一实施例中,SOT-MRAM芯片结构包括多个引线,每个引线具有多个第一部分和与第一部分区分开的多个第二部分。多个第一部分中的每个第一部分具有第一宽度,多个第二部分中的每个第二部分具有第二宽度,第一宽度小于第二宽度。SOT-MRAM芯片结构还包括耦合到每个引线的第一部分的多个存储器单元以及多个晶体管。每个晶体管耦合到多个存储器单元的对应存储器单元。

在另一实施例中,SOT-MRAM芯片结构包括多个引线,每个引线具有多个第一部分和与第一部分区分开的多个第二部分。多个第一部分中的每个第一部分由第一材料制成,多个第二部分中的每个第二部分由第二材料制成,第一材料与第二材料不同。SOT-MRAM芯片结构还包括耦合到每个引线的第一部分的多个存储器单元以及多个晶体管。每个晶体管耦合到多个存储器单元的对应存储器单元。

附图说明

参考实施例更具体地描述上面简述的本公开,使得可以更详细地理解本公开的上述特征,一些实施例在附图中示出。然而,应注意的是,附图仅示出本公开的典型实施例,因此不应理解为限制本发明的范围,因为本公开可应用于其它等效实施例。

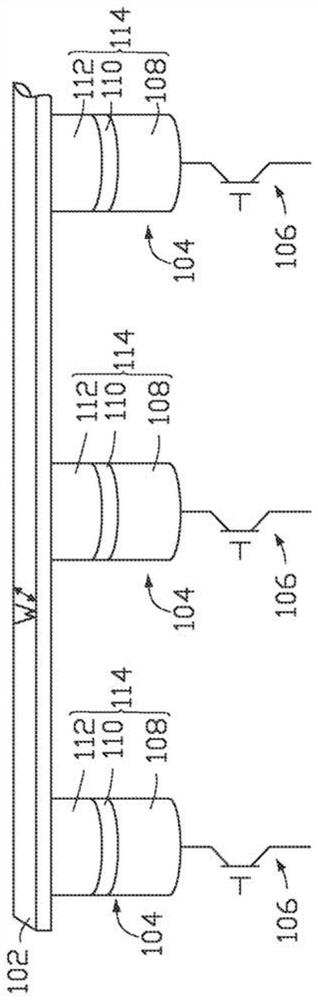

图1是根据本文所述一个实施例的单个引线、多个存储器单元和多个晶体管的示意性透视图。

图2是根据本文所述另一实施例的单个引线、多个存储器单元和多个晶体管的示意性透视图。

图3是根据本文所述又一实施例的单个引线、多个存储器单元和多个晶体管的示意性透视图。

图4A-4J示意性地示出形成根据本文所述一个实施例的引线和存储器单元的工艺步骤。

图5A-5E示意性地示出形成根据本文所述另一实施例的引线和存储器单元的工艺步骤。

图6A-6D示意性地示出形成根据本文所述又一实施例的引线的存储器单元的工艺步骤。

为了便于理解,必要时,使用相同的附图标记来表示附图中共用的相同元件。可以预见的是,一个实施例中公开的元件可有益地用在其它实施例中,而不用特别引用。

具体实施方式

下面,参考本公开的实施例。然而,应理解的是,本公开不限于特定描述的实施例。确切地,可以预见下列特征和元件的任意组合(不管是否涉及不同实施例)实施和实践本公开。而且,尽管本公开的实施例可实现比其它可能方案和/或现有技术更好的优点,但是是否由给定实施例实现特定优点并不限制本公开。因此,下面的方面、特征、实施例和优点仅是说明性的,不被认为是所附权利要求的元件或限定特征,除非权利要求中明确引用。类似地,参考“本公开”不应理解为本文公开的任何创造性主题的归纳,不应理解为所附权利要求的元件或限定特征,除非权利要求中明确引用。

本公开的实施例总体上涉及数据储存和计算机存储系统,更具体地涉及SOT-MRAM芯片结构。SOT-MRAM芯片结构包括多个引线、多个存储器单元以及多个晶体管。引线可以由具有大自旋-轨道耦合强度和高电阻率的材料制成。多个引线的每个引线可包括多个第一部分和与第一部分区分开的多个第二部分。第二部分的电阻率小于第一部分的电阻率,所以引线的总电阻率减小,导致改进的功率效率和信噪比。

图1是根据本文所述一个实施例的单个引线102、多个存储器单元104和多个晶体管106的示意性透视图。引线102、多个存储器单元104和多个晶体管106可以是SOT-MRAM芯片结构的一部分。SOT-MRAM芯片结构可包括多个引线102,每个引线可附接至多个存储器单元104。引线102可以由具有大自旋-轨道耦合强度的材料制成,比如Pt、Ta、W、Hf、Ir、CuBi、CuIr或AuW。具有大自旋-轨道耦合强度的材料可具有高电阻率,比如从约150μΩcm至约250μΩcm。具有大自旋-轨道耦合强度的材料在本文中称为自旋-轨道转矩(SOT)材料。SOT材料的电阻率远大于导电金属(比如铜)的电阻率。在一个实施例中,引线102可具有约为多个存储器单元104的一个存储器单元104的尺寸的恒定宽度W。宽度W可以在约10nm至约500nm的范围内。多个存储器单元104可电耦合至引线102。图1中示出三个存储器单元104,但是多于三个存储器单元104可电耦合至引线102。每个存储器单元104包括具有参考层108、阻挡层110和自由层112的MTJ元件114。自由层112可以与引线102接触。替代地,堆叠中层(in-stack layer)(未示出)可以位于自由层112和引线102之间。自由层112可包括Ni、Fe、Co、B、Ge、Mn之一和/或Ni、Fe、Co、B、Ge或Mn的合金,和/或它们的组合物和混合物,比如NiFe、CoFe或CoFeB。自由层112的磁矩可以在层平面中或垂直于层平面。阻挡层110可以由非磁金属(比如Cu或Ag)或绝缘材料(比如氧化铝、MgO或HfO)制成。参考层108可包括Ni、Fe、Co、B、Ge、Mn之一和/或Ni、Fe、Co、B、Ge或Mn的合金,和/或它们的组合物和混合物,比如NiFe、CoFe或CoFeB,和/或Co/Pt、Co/Pd或Co/Ni超点阵(superlattices)。参考层108的磁矩可以在层平面中或垂直于层平面。参考层108可以简单钉扎或反平行(AP)钉扎。多个晶体管106的每个晶体管106可以电耦合至对应存储器单元104,如图1所示。晶体管106可以是能够切换电功率的任何半导体装置,比如互补金属氧化物半导体(CMOS)晶体管。

在操作期间,通过半选择机制完成写入,半选择机制包括使电流流过引线102和经由电耦合至存储器单元104的晶体管106偏压单个存储器单元104的组合。自旋轨道转矩(SOT)可源自由电流流过引线102产生的自旋霍尔或Rashba效应。仅使电流流过引线102不足以切换存储器单元104的状态。在一个实施例中,流过引线102的电流是导致存储器单元104切换的电流的一半。为了选择特定存储器单元104用于写入处理,将电压施加到存储器单元104,以产生电压受控磁各向异性(VCMA)效应。VCMA效应可以在原子轨道在存储器单元104的MTJ中的界面处的占有率的电场诱导变化(其与自旋轨道耦合协作产生各向异性的变化)方面来解释。例如,界面处的电子密度的减少会增加垂直各向异性。由于该磁电耦合不是应变介导的,所以其不是耐久有限的,从而使得其与逻辑和存储应用兼容。SOT和VCMA的组合选择特定存储器单元104用于写入处理。在此,阻挡层110的阻抗被调谐成足够大使得流过引线102的电流比较小。通过使电流流过引线102并使用晶体管106来选择特定存储器单元104来完成读取。

在另一实施例中,阻挡层110阻抗可以制得足够低,使得跨过特定存储器单元104的MTJ的电流是导致存储器单元104切换的电流的一半。在此,SOT和来自电流的直接自旋转矩传输的组合会选择特定存储器单元104用于写入处理。

为了增加作用在存储器单元104上的转矩,引线102的厚度可以约为所使用的SOT材料的自旋扩散长度,其通常为约5-10nm,引线102的宽度W可以约为存储器单元104的尺寸(以增加电流密度)。由于引线102由具有高电阻率的SOT材料制成,引线102具有比较小的厚度和宽度,所以会出现诸如热产生或低功率效率(由于高电阻率施加的大电压)的问题。为了改进功率效率和降低引线102中的热产生,引线102可以被修改为减少引线102的电阻。

图2是根据本文所述另一实施例的引线102、多个存储器单元104和多个晶体管106的示意性透视图。如图2所示,引线102可包括多个第一部分202和与第一部分区分开的多个第二部分204。第一部分202和第二部分204可以由相同材料制成,比如SOT材料。多个第一部分202的每个第一部分202具有宽度W和多个第二部分204的每个第二部分204具有宽度W

图3是本文所述又一实施例的引线102、多个存储器单元104和多个晶体管106的示意性透视图。如图3所示,引线102可包括多个第一部分302和与第一部分302区分开的多个第二部分304。多个第一部分302的每个第一部分302具有宽度W,多个第二部分304的每个第二部分304具有相同的宽度W。每个第一部分302可以电耦合到存储器单元104,每个第二部分304可以位于两个第一部分302之间。每个第二部分304不与存储器单元104接触。换言之,每个第二部分304位于相邻存储器单元104之间。引线102的第一部分302可以由SOT材料制成,比如Pt、Ta、W、Hf、Ir、CuBi、CuIr或AuW。引线102的第二部分304可以由电阻率比第一部分302低的材料制成。在一个实施例中,引线102的第二部分304可以由一层或多层制成,至少一层由电阻率比第一部分302低的材料构成。在一个实施例中,第二部分304由导电金属(比如铜或铝)的单层或者导导金属/SOT材料的双层制成,SOT材料可以是与第一部分302相同的材料。在另一实施例中,第二部分304由掺杂材料制成,比如掺杂有氮的Ta。第二部分304的掺杂材料可包括基材和掺杂物。基材可以是与第一部分302相同的材料。通过用掺杂物掺杂基材,第二部分304的电阻率小于第一部分302的电阻率。在一些实施例中,第一部分302由包括基材和掺杂物的掺杂材料制成。基材可以是与第二部分304相同的材料。通过用掺杂物掺杂基材,第一部分302的电阻率高于第二部分304的电阻率。使第二部分304由电阻率小于第一部分302的材料制成导致引线102的总体减小的电阻率。由于引线102具有由电阻率小于第一部分302的材料制成的第二部分304,所以由于施加到引线102的较少的电压,功率效率得以增加。

返回参见图2,引线102的总电阻率还可通过使用用于第二部分204的更加导电的材料来减少。在一个实施例中,第一部分202可以SOT材料制成,比如Pt、Ta、W、Hf、Ir、CuBi、CuIr、AuW,第二部分204可由与第二部分304(图3)相同的材料制成。在一个实施例中,第二部分204可以由一层或多层制成,至少一层由电阻率小于第一部分202的材料构成。第二部分204的更宽的宽度W

图4A-4J示意性地示出形成根据本文所述一个实施例的引线102和多个存储器单元的存储器单元104的工艺步骤。如图4A所示,包括金属垫404的基底402可电耦合到晶体管106。下层406可形成在基底402上。下层406可包括多层,比如用于催促MTJ生长的晶粒层和用于钉扎参考层的AFM层。第一铁磁层408可以形成在下层406上并与下层接触,阻挡层410可以形成在第一铁磁层408上并与第一铁磁层接触,第二铁磁层412可以形成在阻挡层410上并与阻挡层接触。第一铁磁层408可以由与参考层108(图1)相同的材料制成,阻挡层410可以由与阻挡层110(图1)相同的材料制成,第二铁磁层412可以由与自由层(图1)相同的材料制成。第一SOT层414可以形成在第二铁磁层412上并与第二铁磁层接触。第一SOT层414可以由SOT材料制成,并具有约2nm至约5nm的厚度。牺牲层416可以形成在第一SOT层414上并与第一SOT层接触。牺牲层416可以由易于蚀刻的材料制成,比如铜、铝或银。牺牲层416的厚度可以为约2nm至约10nm。硬掩模418可以形成在牺牲层416上并与牺牲层接触。硬掩模418可以由具有低蚀刻率的材料制成,比如类金刚石碳、氧化铝、TaN或W。层406-418可以由任何合适的方法形成,比如物理气相沉积、化学气相沉积或等离子体化学气相沉积,并可以在相同处理室中形成。

接下来,在硬掩模418上形成并图案化光致抗蚀剂422,该图案被转移至硬掩模418以使用活性离子蚀刻或湿蚀刻形成硬掩模420,如图4B所示。为了更好地示出堆叠,可以省略晶体管106。接下来,如图4C所示,图案被转换至基底402上的所有层。移除下层406的一部分以形成下层424,移除第一铁磁层408的一部分以形成参考层426,移除阻挡层410的一部分以形成阻挡层428,移除第二铁磁层412的一部分以形成自由层430,移除第一SOT层414的一部分以形成第二SOT层432,移除牺牲层416的一部分以形成牺牲层434。参考层426可以是参考层108(图1),阻挡层428可以是阻挡层110(图1),自由层430可以是自由层112(图1)。参考层426、阻挡层428和自由层430可形成存储器单元104。移除工艺可以是任何合适的移除工艺,比如离子铣削或RIE。介电材料425可以沉积在基底402和层堆叠上。介电材料425可以是氧化铝、SiO

接下来,如图4E所示,移除介电材料425的一部分,从而介电材料的剩余部分438与牺牲层434平齐。通过离子铣削或RIE移除介电材料425的一部分。可以通过RIE移除硬掩模420,如图4F所示。接下来,移除牺牲层434以及介电材料425的剩余部分438的一部分,暴露第二SOT层432,如图4G所示。在一个实施例中,牺牲层434以及介电材料425的剩余部分438具有相同蚀刻率,顶表面440在移除工艺之后是平坦的。移除工艺可以是离子铣削或RIE。

第三SOT层442形成在顶表面440上,如图4H所示。第三SOT层442可以由与引线102相同的材料制成。光致抗蚀剂444可以形成在第三SOT层442上,如图4I所示。光致抗蚀剂444可以图案化为具有恒定宽度W的条纹或者具有带较窄宽度W的多个区域和带较宽宽度W

图5A-5E示意性地示出形成根据本文所述又一实施例的引线102和存储器单元104的工艺步骤。如图5A所示,起始结构与如图4I所示结构相同,存储器单元104可以包括参考层426、阻挡层428和自由层430。接下来,光致抗蚀剂444的图案被转移至第三SOT层442,形成SOT层502,如图5B所示。导电层504沉积在SOT层442的一部分被移除的区域中,形成具有SOT层502和导电层504的平坦顶表面506。替代地,代替移除SOT层442的一部分以形成SOT层502,用掺杂物(比如氮)掺杂SOT层442的未被光致抗蚀剂444覆盖的部分以减少电阻率。因此,SOT层442的由光致抗蚀剂444覆盖的部分是SOT层502,SOT层442的掺杂部分是导电层504。替代地,代替掺杂SOT层442的未被光致抗蚀剂444覆盖的部分,具有较低电阻率的材料可沉积在SOT层442的未被光致抗蚀剂444覆盖的部分。具有较低电阻率的材料可以是导电金属。因此,导电层504可以是包括SOT层和导电金属层的双层。导电层504可以由与引线102的第二部分304(图3)相同的材料制成。图5C是图5B所示顶表面506的顶视图。如图5C所示,顶表面506包括SOT层502和导电层504的交替条纹。SOT层502的每个条纹可以在多个存储器单元104(由虚线表示)上。

接下来,光致抗蚀剂可以沉积在顶表面506上并图案化以形成多个光致抗蚀剂508,如图5D所示。每个光致抗蚀剂条纹508可以与多个存储器单元104对准,并可垂直于SOT层502和导电层504的条纹。移除SOT层502和导电层504的未被光致抗蚀剂条纹508覆盖的部分,形成多个引线510,如图5E所示。光致抗蚀剂条纹508可以通过剥离工艺移除。每个引线510可包括多个第一部分512和与第一部分512区分开的多个第二部分514。第一部分512可以是SOT层502的剩余部分,第二部分514可以是导电层504的剩余部分。引线510可以是引线102,第一部分512可以是第一部分302(图3),第二部分514可以是第二部分304(图3)。

图6A-6D示意性地示出形成根据本文所述另一实施例的引线102和存储器单元104的工艺步骤。如图6A所示,超始结构与如图4J所示结构相同,存储器单元104可以包括参考层426、阻挡层428和自由层430。图6B是图6A所示结构的顶视图。如图6B所示,多个引线446形成在介电材料425的剩余部分438上。接下来,光致抗蚀剂可沉积在多个引线446和介电425的剩余部分438上。光致抗蚀剂可以图案化以形成多个光致抗蚀剂条纹602,如图6C所示。每个光致抗蚀剂条纹602可以与多个存储器单元104对准,并可垂直于引线446。引线446的未被光致抗蚀剂条纹602覆盖的部分可以用掺杂物掺杂,以减小电阻率。接下来,光致抗蚀剂条纹602可以通过剥离工艺移除,多个引线604形成在介电材料425的剩余部分438上。每个引线604可包括多个第一部分606和与第一部分606区分开的多个第二部分608。第一部分512可以是引线446的由光致抗蚀剂条纹602覆盖的部分,第二部分514可以是引线446的掺杂部分。引线604可以是引线102,第一部分606可以是第一部分302(图3),第二部分608可以是第二部分304(图3)。

总之,公开了一种包括多个引线、多个存储器单元和多个晶体管的SOT-MRAM芯片结构。引线可包括耦合到存储器单元的第一部分和不耦合到存储器单元的第二部分。第一部分由具有大自旋-轨道耦合强度的SOT材料制成,第一部分比较薄和窄。第二部分比第一部分更宽和/或由更加导电的材料制成。具有第二部分减少了引线的总电阻率,从而导致增加的功率效率。

尽管前述内容涉及本公开的实施例,但是在不脱离本发明的基本范围的情况下,可以得到其它和另外实施例,本发明的范围由下面的权利要求确定。

- 底部钉扎SOT-MRAM位结构和制造方法

- 底部钉扎SOT‑MRAM位结构和制造方法