一种高频地波雷达的任意工作周期同步组网方法及设备

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及地波雷达主机系统、雷达组网技术领域,具体涉及一种高频地波雷达的任意工作周期同步组网方法及设备。

背景技术

高频地波雷达(HF Surface Wave Radar)是我国海洋环境立体监测网的重要组成部分,利用其超视距、全天候、大范围、高分辨率、低成本的优点,实现了传统“点探测”到“面探测”的突破。

高频地波雷达组网技术主要应用于收发分站(发射和接收在不同的位置)的单站高频地波雷达主机系统的发射信号时序与接收信号时序的同步,或是收发同站(发射和接收设备在同一位置)的多站组网地雷达系统中一个站雷达的接收信号时序与其他雷达的发射信号的时序同步。

而现有大部分高频地波雷达是独立工作状态,获取的回波信号较为单一,而且容易受到相邻雷达的同频段干扰;而小部分已经组网的雷达,利用1pps信号卫星信号同步方法,是在1pps信号的上升沿后(每个1pps信号的周期为1秒)立即实现同步时序波形更新,从而要求1秒被工作周期整除(如工作周期为500ms、250ms、200ms),因此雷达参数具有一定的局限性,影响了雷达的性能。同时,现有的采用光纤网络同步方式在沿海及偏远岛礁无法实施,采用微波中继方式易受海上环境(下雨、大雾)影响而不稳定,采用原子钟的同步方式使系统成本高而难以推广,采用GPS卫星单系统的同步方式容易受到国外的限制、封锁。

发明内容

有鉴于此,本发明提供了一种高频地波雷达的任意工作周期同步组网方法及设备,可跟踪多频卫星信号,能够实现任意工作周期的高频地波雷达同步组网,适用于收发分站的单站高频地波雷达主机系统和收发同站的多站组网雷达系统,精度高、成本低。

为了解决上述技术问题,本发明是这样实现的。

一种高频地波雷达的任意工作周期同步组网设备,包括:全系统多频卫星接收模块、恒温晶振、FPGA数字信号处理器、数字PLL模块和电源模块;

所述全系统多频卫星接收模块,与多频卫星天线相连,用于同时跟踪多频率卫星信号,输出1pps信号和报文信号;该全系统多频卫星接收模块的报文信号引脚直接与FPGA数字信号处理器相连;1pps引脚分两路信号后,其中1路pps信号与FPGA数字信号处理器相连,以提供时间报文信号提供时序,另1路pps信号与数字PLL模块的参考引脚相连,以提供参考输入;

所述数字PLL模块的时钟输入引脚与恒温晶振信号输出相连,在数字PLL模块中输入时钟信号经倍频后,输出至少2路高精度的驯服时钟信号,1路驯服时钟信号驱动FPGA数字处理器,1路驯服时钟信号用于驱动地波雷达主机系统;

所述的FPGA数字信号处理器,通过串口、时序同步控制引脚与地波雷达主机系统相连;地波雷达主机系统通过串口向FPGA数字信号处理器发送包括雷达工作周期T

所述电源模块为本组网设备的用电设备提供电源。

优选地,所述全系统多频卫星接收模块同时跟踪包括北斗卫星导航系统BDS、全球定位系统GPS、格洛纳斯卫星导航系统GLONASS、伽利略卫星导航系统Galileo的多频卫星信号。

优选地,所述全系统多频卫星接收模块采用和芯星通科技有限公司的UT4B0高精度授时模块。

优选地,所述数字PLL模块采用ADI公司以AD9548为核心的数字PLL。

优选地,所述FPGA数字信号处理器采用Xilinx公司的Xilinx Spartan-7系列XC7S6-1CSGA225I芯片。

优选地,所述恒温晶振采用Abracon公司的AOCJY-20MHz。

本发明还提供了一种高频地波雷达的任意工作周期同步组网方法,该方法为组网的每个地波雷达主机系统配备一个上述任意一种同步组网设备;组网的多个地波雷达主机系统均以一相同的历史时刻为共同起始时刻,记为T

步骤1、地波雷达主机系统启动时,地波雷达主机系统向同步组网设备的FPGA数字信号处理器下发雷达工作周期T

步骤2、地波雷达主机系统启动后,同步组网设备的FPGA数字信号处理器接收到1pps信号时,将接收时刻作为当前时刻,并等待当前时刻的报文信号,FPGA数字信号处理器接收到全系统多频卫星接收模块的报文信号后,解析出当前时刻T

步骤3、计算同步时刻时间差T

T

步骤4、计算时间差T

N

T

步骤5、计算同步时刻的1pps到来之后,需要的延时时间T

T

X=T

步骤6、等待同步时刻的1pps信号;当同步时刻的1pps信号到来后,FPGA数字信号处理器开始计数,计数值为Y;当计数值Y等于延时寄存器值X时,FPGA数字信号处理器输出时序同步信号给地波雷达主机系统。

优选地,所述同步组网设备每间隔1小时执行一次步骤2-6,自动同步一次。

有益效果:

(1)本发明的同步方法,采用假定组网的多个雷达系统均以某一相同的历史时刻为共同起始时刻,利用报文信号和1pps信号,计算下一个1pps信号与雷达工作帧周期的时间延时,从而保证每个组网雷达系统的工作周期相互之间实现同步。该方法实现了对雷达工作周期长短没有任何限制,实现了雷达任意工作周期的同步组网,突破了传统方法要求雷达工作周期必须满足1s的整分时间的限制。

(2)本发明的同步装置采用了可同时跟踪BDS、GPS、GLONASS、Galileo多频卫星信号的接收模块,不仅可以大大提高同步组网的精度,而且在特殊时期(战争)失去GPS等信号时,仍可以利用我国的北斗BDS授时,保证系统组网精度。

(3)本发明的优选实施方式,基于本发明的同步方法和装置,通过选择合适的器件使得雷达组网的同步时间<10ns,提高了雷达回波信号的相干性,从而增强了收发分站雷达系统、收发共站组网雷达系统的探测精度、性能。

附图说明

图1为本发明实施例的组网雷达的信号收发示意图。

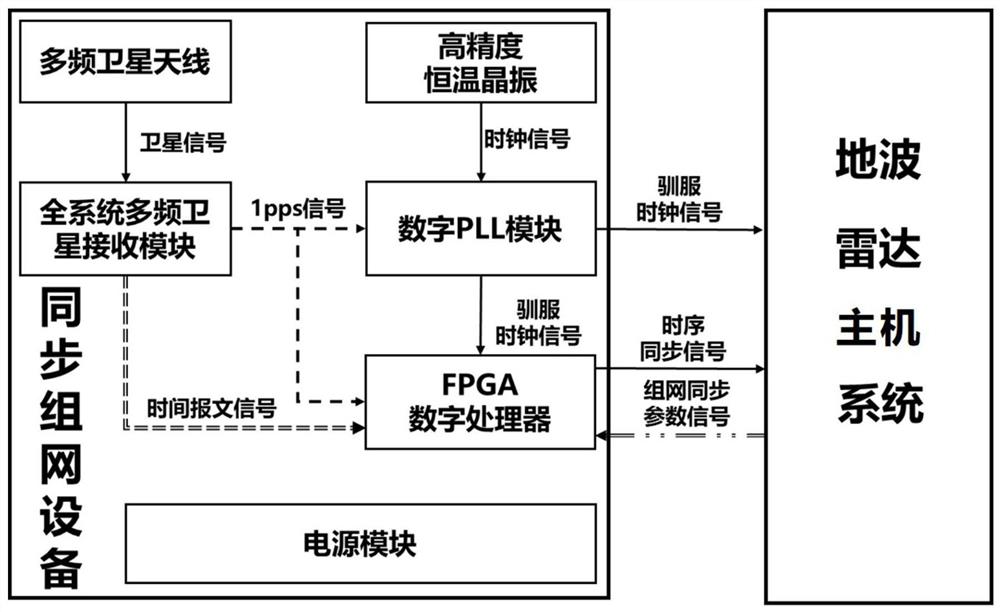

图2为本发明实施例的同步组网设备及其与地波雷达主机系统了解关系示意图。

图3为本发明实施例的同步组网方法的流程图。

图4为本发明实施例的同步组网方法及设备的时序图。

具体实施方式

下面结合附图并举实施例,对本发明进行详细描述。

本发明提供了一种高频地波雷达的任意工作周期同步组网方案,如图1所示,如图1所示,该方案为组网的每个地波雷达主机系统配备一个同步组网设备,采用假定组网的多个地板雷达系统均以某一相同的历史时刻为共同起始时刻,同步组网设备利用报文信号和1pps信号,并结合每个组网雷达系统的工作周期,计算下一个1pps信号与雷达工作帧周期的时间延时,从而保证每个组网雷达系统的工作周期相互之间实现同步。该方法实现了对雷达工作周期长短没有任何限制,实现了雷达任意工作周期的同步组网,突破了传统方法要求雷达工作周期必须满足1s的整分时间的限制。

图2为本发明高频地波雷达的任意工作周期同步组网设备及其与地波雷达主机系统的联系关系示意图。如图2所示,同步组网设备包括全系统多频卫星接收模块、恒温晶振、FPGA数字信号处理器、数字PLL模块和电源模块。在本优选实施例中,全系统多频卫星接收模块采用和芯星通科技有限公司的UT4B0高精度授时模块,数字PLL模块采用ADI公司的AD9548,FPGA数字信号处理器采用的是Xilinx公司的Xilinx Spartan-7系列XC7S6-1CSGA225I芯片,高精度恒温晶振采用的是Abracon公司的AOCJY-20MHz。

全系统多频卫星接收模块,与多频卫星天线相连,用于同时跟踪多频率卫星信号,输出1pps信号和报文信号;该全系统多频卫星接收模块的报文信号引脚直接与FPGA数字信号处理器相连;1pps引脚分两路信号后,其中1路pps信号与FPGA数字信号处理器相连,以提供报文信号时序,另1路pps信号与数字PLL模块的参考引脚相连,以提供参考输入。本优选实施例的全系统多频卫星接收模块可同时跟踪BDS、GPS、GLONASS、Galileo多频卫星信号,实现输出高精度1pps信号,实时输出报文信号。

数字PLL模块的时钟输入引脚与恒温晶振信号输出相连,参考输入为1pps信号,在内部的PLL控制环路、鉴频鉴相器的控制下,在数字PLL模块中输入时钟信号经倍频后,可以输出多路高精度、高稳定度的驯服时钟信号,1路驯服时钟信号驱动FPGA数字处理器,1路驯服时钟信号用于驱动地波雷达主机系统。本优选实施例的数字PLL模块采用的AD9548是一款配有直接数字频率合成器(DDS)的数字PLL芯片。

FPGA数字信号处理器,通过串口、时序同步控制引脚与地波雷达主机系统相连;地波雷达主机系统通过串口向FPGA数字信号处理器发送组网时序参数(脉冲周期、雷达工作周期T

电源模块为本组网设备的用电设备提供电源。

参见图3、图4,利用本发明高频地波雷达的任意工作周期同步组网设备进行多站地波雷达主机系统同步组网工作的方法,包括如下步骤:

首先假定组网的多个地波雷达主机系统均以某一相同的历史时刻为共同起始时刻,记为T

步骤1、地波雷达主机系统启动时,地波雷达主机系统向同步组网设备的FPGA数字信号处理器下发雷达工作周期T

步骤2、雷达系统启动后,同步组网设备的FPGA数字信号处理器接收到1pps信号时,将接收时刻作为当前时刻,并等待当前时刻的时间报文信号(时间报文信号与对应的1pps信号有一定的延迟,延迟时间<100ms),FPGA数字信号处理器接收到全系统多频卫星接收模块的时间报文信号后,解析出当前时刻T

步骤3、计算同步时刻时间差T

T

步骤4、计算时间差T

N

T

步骤5、计算同步时刻的1pps到来之后,需要的延时时间T

T

X=T

上述步骤中,步骤3、步骤4、步骤5参数的计算,必须在同步时刻的1pps到来之前完成。通过步骤3-5,将不同工作周期的地波雷达主机系统的延迟时间进行了各自计算。

步骤6、等待同步时刻的1pps信号;当同步时刻的1pps信号到来后,FPGA数字信号处理器开始计数,计数值为Y;当计数值Y等于延时寄存器值X时,FPGA数字信号处理器输出时序同步信号给地波雷达主机系统。

地波雷达主机系统按照时序同步信号,在上升沿开始工作,即完成了组网同步。

完成同步后,为防止系统时钟的积累误差,雷达同步组网模块会每间隔1小时会自动同步一次。因此可以每隔1小时执行一次步骤2-6。

以上的具体实施例仅描述了本发明的设计原理,该描述中的部件形状,名称可以不同,不受限制。所以,本发明领域的技术人员可以对前述实施例记载的技术方案进行修改或等同替换;而这些修改和替换未脱离本发明创造宗旨和技术方案,均应属于本发明的保护范围。

- 一种高频地波雷达的任意工作周期同步组网方法及设备

- 高频地波雷达组网的时钟同步控制方法及其装置