阵列基板、显示面板及显示装置

文献发布时间:2023-06-19 11:32:36

技术领域

本申请涉及显示技术领域,具体涉及一种阵列基板、显示面板及显示装置。

背景技术

有机发光二极管(Organic Light Emitting Diode,OLED)是当今显示器研究领域的热点之一,与液晶显示器(Liquid Crystal Display,LCD)相比,OLED显示屏具有低能耗、生产成本低、自发光、宽视角及响应速度快等优点,目前,在手机、PDA、数码相机等显示领域OLED阵列基板已经开始取代传统的LCD阵列基板。

在OLED阵列基板中设置有像素电路以驱动OLED发光元件,像素电路包括驱动晶体管,然而驱动晶体管的栅极电位存在不稳定的情况,影响显示效果。

发明内容

本申请提供一种阵列基板、显示面板及显示装置,能够提高驱动晶体管的栅极电位的稳定性,改善显示效果。

第一方面,本申请实施例提供一种阵列基板,其包括呈阵列分布的多个像素电路以及与各列像素电路电连接的第一信号线;第一信号线包括分支部;各像素电路包括存储电容、驱动晶体管和与驱动晶体管栅极部电性连接的第一连接部;存储电容的一个极板与驱动晶体管的栅极部至少部分重叠,分支部与第一连接部至少部分交叠。

第二方面,基于同一发明构思,本申请实施例提供一种显示面板,其包括如第一方面实施例的阵列基板。

第三方面,本申请实施例提供一种显示装置,其包括如第二方面实施例的显示面板。

根据本申请实施例,由于第一信号线包括分支部,第一信号线与固定电压端电连接,因此分支部上的电位与第一信号线上的电位相同且均为固定电位,并且第一连接部与驱动晶体管的栅极部电连接,分支部与第一连接部至少部分交叠,因此分支部与第一连接部所交叠的部分构成了像素电路的辅助存储电容,从而使得像素电路中与驱动晶体管的栅极部电连接的电容既包括存储电容又包括分支部与第一连接部的交叠部分构成的辅助存储电容,增大了像素电路中与驱动晶体管的栅极部电连接的电容的容值,因此能够提高驱动晶体管的栅极电位的稳定性,改善显示效果。

附图说明

通过阅读以下参照附图对非限制性实施例所作的详细描述,本申请的其它特征、目的和优点将会变得更明显,其中,相同或相似的附图标记表示相同或相似的特征,附图并未按照实际的比例绘制。

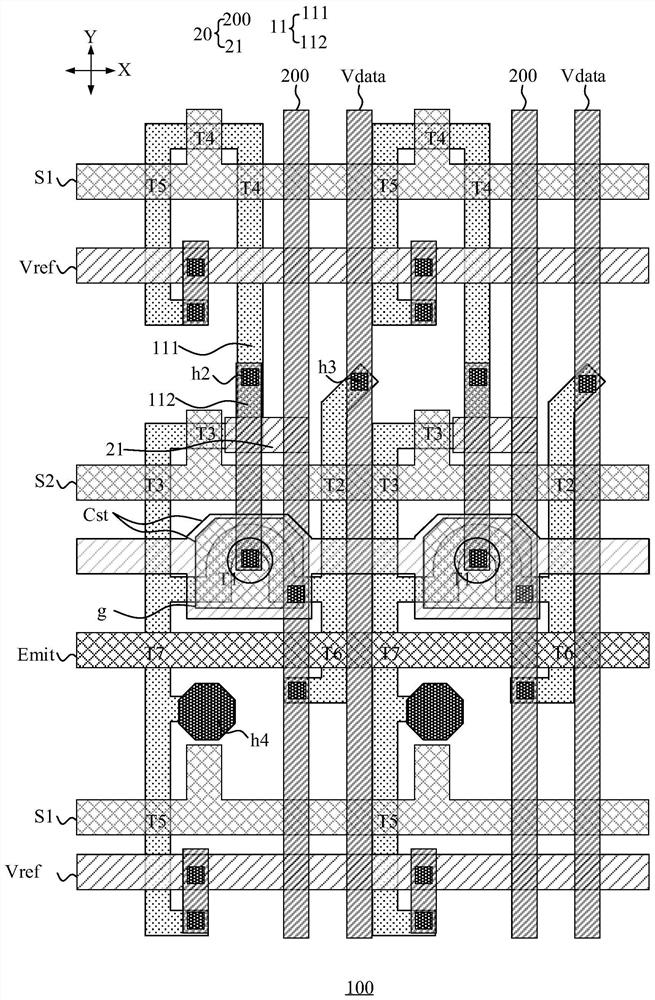

图1示出本申请一种实施例提供的阵列基板的俯视示意图;

图2示出本申请一种实施例提供的像素电路的电路结构示意图;

图3示出图2的一种时序示意图;

图4示出本申请一种实施例提供的阵列基板的截面示意图;

图5示出本申请一种实施例提供的阵列基板的截面示意图;

图6示出本申请一种实施例提供的阵列基板的局部版图俯视结构示意图;

图7示出本申请一种实施例提供的阵列基板的局部版图仰视结构示意图;

图8至图18示出本申请一些实施例提供的阵列基板的局部版图俯视结构示意图;

图19示出图15中AA向的一种剖面结构示意图;

图20示出图15中AA向的另一种剖面结构示意图;

图21示出本申请又一种实施例提供的阵列基板的局部版图仰视结构示意图;

图22示出本申请另一种实施例提供的像素电路的电路结构示意图;

图23示出本申请一种实施例提供的显示面板的结构示意图。

图24示出本申请一种实施例提供的显示装置的结构示意图。

具体实施方式

下面将详细描述本申请的各个方面的特征和示例性实施例,为了使本申请的目的、技术方案及优点更加清楚明白,以下结合附图及具体实施例,对本申请进行进一步详细描述。应理解,此处所描述的具体实施例仅被配置为解释本申请,并不被配置为限定本申请。对于本领域技术人员来说,本申请可以在不需要这些具体细节中的一些细节的情况下实施。下面对实施例的描述仅仅是为了通过示出本申请的示例来提供对本申请更好的理解。

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。

应当理解,在描述部件的结构时,当将一层、一个区域称为位于另一层、另一个区域“上面”或“上方”时,可以指直接位于另一层、另一个区域上面,或者在其与另一层、另一个区域之间还包含其它的层或区域。并且,如果将部件翻转,该一层、一个区域将位于另一层、另一个区域“下面”或“下方”。

在OLED阵列基板中设置有像素电路以驱动OLED发光元件,OLED发光元件是电流驱动,像素电路包括驱动晶体管,然而驱动晶体管的阈值电压的漂移会造成显示不均等问题,因此,现有技术中采用像素补偿电路补偿驱动晶体管阈值电压的漂移。然而,这仅仅是从等效电路的角度对驱动晶体管的阈值电压进行补偿。在实际的补偿电路的版图设计中,信号线,晶体管,存储电容之间的存在较多的寄生电容和信号干扰。由于存储电容起到在一帧的时间内保持驱动晶体管的栅极电位的作用,而在版图设计中,存储电容占用的面积较大,这和高像素密度(Pixels Per Inch,PPI)的趋势是相悖的。并且,想要增加存储电容占用的面积还需要考虑其会不会带来寄生电容和信号干扰的问题,因此,存储电容的版图布局设计牵一发而动全身,其成为制约高PPI,高刷新率等技术的,难以突破的重大技术问题。

本申请实施例提供一种阵列基板、显示面板及显示装置,以下将结合附图对本申请实施例提供的阵列基板、显示面板及显示装置进行说明。

如图1所示,本申请实施例提供的阵列基板100包括多个像素电路10。多个像素电路10可以阵列分布于显示区。例如,多个像素电路10可以在相交的第一方向X和第二方向Y上呈阵列分布。

示例性的,阵列基板100还可以包括驱动芯片IC、第一栅极驱动电路VSR1、第二栅极驱动电路VSR2、电源信号线PVDD、数据信号线Vdata,参考信号线Vref,第一扫描信号线S1,第二扫描信号线S2,发光控制信号线Emit。

第一栅极驱动电路VSR1可以包括多个级联的移位寄存器,第一栅极驱动电路VSR1通过第一扫描信号线S1、第二扫描信号线S2与像素电路10连接,第一栅极驱动电路VSR1用于向像素电路10提供扫描信号。驱动芯片IC为第一栅极驱动电路VSR1提供第一起始信号STV1。另外,当前行的第二扫描信号线S2可以复用为下一行的第一扫描信号线S1。

第二栅极驱动电路VSR2可以包括多个级联的移位寄存器,第二栅极驱动电路VSR2通过发光控制信号线Emit与像素电路10连接,第二栅极驱动电路VSR2用于向像素电路10提供发光控制信号线。驱动芯片IC为第二栅极驱动电路VSR2提供第一起始信号STV2。

另外,第一栅极驱动电路VSR1与驱动芯片IC之间以及第二栅极驱动电路VSR2与驱动芯片IC之间可以连接有时钟信号线(图中未示出),驱动芯片IC向第一栅极驱动电路VSR1以及第二栅极驱动电路VSR2提供时钟信号。

示例性的,也可以设置能够同时产生扫描信号和发光控制信号的栅极驱动电路。本申请对此不作限定。

如图2所示,像素电路10包括存储电容Cst以及驱动晶体管T1。示例性的,图2以像素电路10包括存储电容Cst以及七个晶体管为例,其中,T2为数据写入晶体管,T3为补偿晶体管,T4为栅极初始化晶体管,T5为阳极初始化晶体管,T6为电源写入晶体管,T7为发光控制晶体管,D为发光元件,PVEE为公共电源信号线。各晶体管及信号线的连接方式如图2所示,在此不再详细赘述。其中,N1、N2、N3及N4表示连接节点。

电源信号线PVDD用于向驱动晶体管T1提供电源电压,电源信号线PVDD上的电压可以为正电压。公共电源信号线PVEE上的电压可以为负电压。参考信号线Vref用于提供重置电压信号,参考信号线Vref上的电压可以为负电压。

以图2所示的像素电路10中的各晶体管均为P型晶体管为例,如图3所示,像素电路10的驱动过程可以包括重置阶段、数据写入阶段及发光阶段。在重置阶段,第一扫描信号线S1提供低电平信号,栅极初始化晶体管T4及阳极初始化晶体管T5导通,重置驱动晶体管T1的栅极电位及发光元件的阳极电位。在数据写入阶段,第二扫描信号线S2提供低电平信号,数据写入晶体管T2及补偿晶体管T3导通,数据信号线Vdata上的数据信号写到驱动晶体管T1的栅极,且对驱动晶体管T1的阈值电压进行补偿。在发光阶段,发光控制信号线Emit提供低电平信号,电源写入晶体管T6、发光控制晶体管T7导通,驱动晶体管T1产生的驱动电流传输至发光元件,发光元件发光。

图2、图3仅仅是一种示例,并不用于限定本申请。

为了更好的从整体上理解实施例提供的阵列基板的结构,请参考图4及图5。如图4所示,阵列基板可以包括显示区AA、非显示区NA,非显示NA可以包括油墨区INK。示例性的,阵列基板包括衬底01及设置于衬底01一侧的器件层02。图4还示出了平坦化层PLN、像素定义层PDL、发光元件(包括阳极RE、有机发光层OM及阴极SE)、支撑柱PS、薄膜封装层(包括第一无机层CVD1、有机层IJP及第二无机层CVD2)、光学胶层OCA、盖板CG。另外,图4还示出了第一栅极驱动电路VSR1、第一挡墙Bank1及第二挡墙Bank2。第一栅极驱动电路VSR1可设置于器件层02的非显示区。

像素电路10可设置于器件层02内,像素电路10与发光元件的阳极RE连接。如图5所示,阵列基板的器件层02可包括在远离衬底01方向上层叠设置的栅极金属层M1、电容金属层MC及源漏金属层M2。栅极金属层M1与衬底01之间设置有半导体层b。各金属层之间以及半导体层b与栅极金属层M1之间设置有绝缘层。示例性的,栅极金属层M1与半导体层b之间设有栅极绝缘层GI,电容金属层MC与栅极金属层M1之间设有电容绝缘层IMD,源漏金属层M2与电容金属层MC之间设有层间介质层ILD。

半导体层b为晶体管的有源层所在的半导体层,栅极金属层M1为晶体管的栅极所在的金属导电层,电容金属层MC为电容的其中一个极板所在的金属导电层,源漏极金属层M2为晶体管的源极和漏极所在的金属导电层。

示例性的,第一扫描信号线S1、第二扫描信号线S2以及发光控制信号线Emit可设置于栅极金属层M1。参考信号线Vref可设置于电容金属层MC,电源信号线PVDD以及数据信号线Vdata可设置于源漏极金属层M2。当然,也可以按照其它方式设置各信号线所在膜层,本申请对此不作限定。

如图6和图7所示,本申请实施例提供的阵列基板100还包括与各像素电路10电连接的第一信号线20。为了清楚的示出阵列基板的结构,图6和图7为不同角度的示意图,其中,图6示意的是从正面观察(可以理解为源漏金属层M2在上层)的示意图,图7示意的是从背面观察(可以理解为半导体层b在上层)的示意图。

另外,图6中仅仅示意出了阵列基板100的局部区域,这并不用于限定本申请。

示例性的,第一信号线20可以与与固定电压端电连接(图中未示出),也就是说第一信号线20上的电位为固定电位。

在一些可选的实施例中,第一信号线20包括电源信号线PVDD,第一信号线20可以包括本体部200,本体部200可以为电源信号线PVDD。示例性的,第一信号线20的本体部200可以沿第二方向Y延伸。当然,第一信号线20也可以不包括本体部,下面的实施例中会介绍第一信号线20不包括本体部的具体示例。

参考图6和图7,像素电路10包括存储电容Cst、驱动晶体管T1以及与驱动晶体管T1的栅极部g电性连接的第一连接部11。存储电容Cst的一个极板与驱动晶体管T1的栅极部g至少部分重叠,也就是说,存储电容Cst与驱动晶体管T1的栅极部g电连接,并且驱动晶体管T1的栅极部g至少部分复用为存储电容Cst的一个极板。

另外,驱动晶体管T1的栅极部g及第一连接部11可以设置于不同的膜层。例如,第一连接部11至少部分位于源漏金属层M2,第一连接部11与驱动晶体管T1的栅极部g通过过孔连接,为避免信号串扰,存储电容Cst的设置在电容金属层MC的一个极板包括通孔,连接驱动晶体管T1的栅极部g与第一连接部11的过孔穿过存储电容Cst的极板上的通孔。

第一信号线20包括分支部21。可以理解的是,分支部21上的电位与第一信号线20上的电位相同。示例性的,在第一信号线20包括本体部的情况下,分支部21与第一信号线20的本体部200电连接。

分支部21与第一连接部11至少部分交叠。也就是说,分支部21与第一连接部11位于不同膜层,且分支部21在阵列基板100所在平面上的正投影与第一连接部11在阵列基板100所在平面上的正投影至少部分交叠。

示例性的,以第一信号线20为电源信号线PVDD为例进行说明,请参考图图6或图7,存储电容Cst设计在构成补偿晶体管T3和发光控制晶体管T7的半导体层、构成数据写入晶体管T2和电源写入晶体管T6的半导体层、第二扫描信号线S2和发光控制信号线Emit围成的区域之内;如果直接增加存储电容Cst的面积,则需要在第一方向X或者第二方向Y增加Cst的宽度,如果要保持寄生电容基本不变,则以上指出包围Cst的扫描信号线或者半导体部都需要同步的向第一方向X或者第二方向Y外扩,以保持其和Cst的间隙距离不变。这会导致像素电路的版图布局第一方向X或者第二方向Y的间距(pitch)增加,造成PPI的降低。如果只增加Cst的面积而上述扫描信号线和半导体部不发生移动保持Pitch不变,则Cst和这些扫描信号线和半导体部之间的间距会减小。而此间隙本已经处于比较小的尺度,间隙的减小将使得寄生电容的干扰急剧增加;而且在制程过程中,较小的间隙可能造成处于同膜层的信号线之间短路,降低生产的良率。

而在本实施例中,申请人不再局限于存储电容的概念,通过将与驱动晶体管T1的栅极部g直接电连接的第一连接部11作为增加“存储电容”的部分,将分支部21与第一信号线20的本体部200之间电连接,分支部21与第一连接部11所交叠的部分构成辅助存储电容,一方面,当数据信号写入到存储电容的过程当中时,数据信号通过数据线号线Vdata,经过驱动晶体管T1和补偿晶体管T3先到达第一连接部11,从第一连接部11传输到驱动晶体管的栅极连接的存储电容Cst的过程中出来会对存储电容进行充电之外,也会对分支部21和第一连接部11构成的辅助存储电容进行充电,从而增大了像素电路10中与驱动晶体管T1的栅极部g电连接的电容的容值,提升驱动晶体管T1的栅极电位(即图2中N节点电位)的稳定性,降低串扰对驱动晶体管T1的栅极电位的影响,从而改善crosstalk问题。

另一方面,由于分支部21和第一连接部11构成的辅助存储电容的容值比较小,电容的充电时间常数t

另外,在高频驱动下,由于一帧的时间大大缩短,因此,每一行的充电时间也进一步减小,导致充电时间减小,因此只能减小存储电容Cst的容值,加快充电速度。然而,由于高频驱动下,数据信号,扫描信号,时钟信号的跳变速率都大大增加,导致信号耦合和串扰的问题加重,需要增加存储电容的容值,稳定N1节点的电位;因此,就产生了矛盾,导致高频驱动下的显示效果大打折扣。而本申请可以在增加了辅助存储电容,相当于将现有技术中的一个存储电容分成了两部分,进而可以降低存储电容的容值,从而降低了充电时间,解决了高频驱动存储电容存在的矛盾。

在另一些可选的实施例中,第一信号线20可以为参考信号线Vref,参考信号线Vref用于提供重置电压信号。例如,第一信号线20可以用于向像素电路10中的驱动晶体管的栅极提供重置电压信号,也可以用于向发光元件的阳极提供重置电压信号。第一信号线20提供的重置电压信号可以为负电压。

当显示的数据电压为黑态电压的时候,N1节点的电位接近于电源信号线PVDD的电位,这样存储电容Cst两端的电压差比较小,也就是Q=C*U中的U比较小,而存储电容Cst的容值C是固定不变的,因此,导致数据电压为黑态电压时存储电容Cst的电荷量Q=C*U比较小。而本申请实施例中,第一信号线20为参考信号线Vref时,也就是构成辅助电容的分支部21和第一连接部11中的分支部21的电位与参考信号线Vref的电位相同,参考信号线Vref的电位与电源信号线PVDD的电位之间的差值较大,可以在黑态电压时使得N1节点存储更多的电荷。

示例性的,本行像素电路10中的栅极初始化晶体管T4的输入端可以与上一行像素电路的N4节点电连接。示例性的,第四过孔h4可用于连接发光元件D的阳极,本行的发光元件D的阳极可以与下一行第一扫描信号线S1所连接的阳极初始化晶体管T5(图6中位于下面的T5)电连接。示例性的,本行的第二扫描信号线S2可以与下一行的第一扫描信号线S1电连接,也就是说,本行的第二扫描信号线S2上的扫描信号与下一行的第一扫描信号线S1上的扫描信号相同。上述仅仅是一些示例,并不用于限定本申请。

另外,本申请实施例提供的像素电路的结构仅仅是一种示例,在像素电路10包括存储电容Cst、驱动晶体管T1以及分支部21与第一连接部11至少部分交叠的基础上,本申请对像素电路10的具体电路结构以及阵列基板的具体版图结构不作限定。

可以理解的是,在第一信号线20为电源信号线PVDD的情况下,分支部21与第一连接部11的交叠部分构成的辅助存储电容与存储电容Cst是并联关系。在第一信号线20为参考信号线Vref的情况下,分支部21与第一连接部11的交叠部分构成的辅助存储电容与存储电容Cst为非并联关系。

在一些可选的实施例中,如图8所示,分支部21包括连接分支部212和第一分支部211。连接分支部212通过第一过孔h1与第一信号线20电连接。可以理解的是,第一信号线20还包括本体部200,连接分支部212是与第一信号线20的本体部200连接的。第一分支部211与第一连接部11至少部分交叠。可以理解的是,连接分支部212与第一信号线20的本体部200可以位于不同膜层。示例性的,第一分支部211和连接分支部212可以位于同一膜层。

本申请实施例中,将第一分支部211与第一信号线20之间通过连接分支部212连接,第一分支部211与第一连接部11所交叠的部分构成辅助存储电容。

示例性的,如果将第一过孔h1设置在第二扫描信号线S2靠近驱动晶体管T1的一侧,为了避免第二扫描信号线S2与第一过孔h1交叠,需要将第二扫描信号线S2在第二方向Y上朝着远离驱动晶体管T1的一侧移动,导致第二方向Y的pitch增加,造成PPI的降低。另外,由于存储电容Cst的两个极板分别位于栅极金属层和电容金属层,并且存储电容Cst的下方为“几”字形的半导体部,因此第一分支部211设置于其中任何一个膜层都需要增加线距,版图设计难度将会大大提升,也会造成PPI的降低。因此将第一过孔h1设置于第二扫描信号线S2远离驱动晶体管T1的一侧,能够避免降低PPI,且不会导致增加第一过孔h1的制备难度。另外,以第一连接部11包括第一半导体连接部111和第一金属连接部112,数据信号线Vdata与数据写入晶体管T2通过第三过孔h3连接为例,将第一过孔h1设置于第二扫描信号线S2远离驱动晶体管T1的一侧,可以形成第一金属连接部112与第三过孔h3之间垂直于阵列基板所在平面的垂直状隔离柱,以隔绝第一金属连接部112与第三过孔h3之间的信号耦合。

当然,也可以将第一过孔h1设置于其它位置,本申请对此不作限定。

示例性的,连接分支部212与第一信号线20的本体部200位于同一膜层时,连接分支部212与第一信号线20的本体部200之间可以直接连接,不必再设置第一过孔h1。

在一些可选的实施例中,如图6或图7所示,像素电路10包括栅极初始化晶体管T4。栅极初始化晶体管T4通过第一连接部11与驱动晶体管T1的栅极部g电连接。第一连接部11包括第一半导体连接部111和第一金属连接部112。第一半导体连接部111和第一金属连接部112可以位于不同膜层,第一半导体连接部111和第一金属连接部112通过第二过孔h2连接,第二过孔h2位于第一分支部211远离驱动晶体管T1的一侧。

第一半导体连接部111和补偿晶体管T3的半导体部连接,通过将第二过孔h2设置于第一分支部211远离驱动晶体管T1的一侧,使得第一分支部211与第一金属连接部112及第一半导体连接部111均交叠,第一分支部211与第一金属连接部112能够形成辅助存储电容,且第一分支部211与第一半导体连接部111也能够形成辅助存储电容,能够进一步增大辅助存储电容的容值。

示例性的,第一分支部211可以位于第一金属连接部112与第一半导体连接部111之间,使得第一分支部211与第一金属连接部112构成的辅助存储电容的极板间距以及第一分支部211与第一半导体连接部111构成的辅助存储电容的极板间距均比较小,从而进一步增大辅助存储电容的容值。

示例性的,第一半导体连接部111位于半导体层b,第一金属连接部112可位于源漏金属层M2,第一分支部211位于电容金属层MC。第一分支部211与第一半导体连接部111之间间隔有栅极绝缘层GI和电容绝缘层IMD,第一分支部211与第一金属连接部112之间间隔有层间介质层ILD,从而使得第一分支部211与第一金属连接部112构成的辅助存储电容的极板间距以及第一分支部211与第一半导体连接部111构成的辅助存储电容的极板间距均比较小,从而进一步增大辅助存储电容的容值。

另外,将第一分支部211设置于电容金属层MC而不是栅极金属层M1,第一分支部211和相邻的第二扫描信号线S2之间的间隙可以更小一些。例如,第一分支部211和相邻的第二扫描信号线S2都设置在栅极金属层M1,两者之间的间隙可能至少需要2μm,导致需要增加pitch,降低PPI,而将第一分支部211设置于电容金属层MC,第二扫描信号线S2设置于栅极金属层M1,两者之间的间隙可以是1μm,可避免增加pitch,进而避免降低PPI。

示例性的,栅极初始化晶体管T4的半导体部与第一半导体连接部111可位于同一膜层且直接连接,驱动晶体管T1的栅极部g与第一金属连接部112可位于不同膜层且通过过孔连接。

示例性的,栅极初始化晶体管T4可以为双栅晶体管,从而进一步提高驱动晶体管T1的栅极电位的稳定性。

在一些可选的实施例中,如图9或图10所示,像素电路10包括栅极初始化晶体管T4和数据写入晶体管T2。栅极初始化晶体管T4通过第一连接部11与驱动晶体管T1的栅极部g电连接,第一连接部11包括第一半导体连接部111和第一金属连接部112,第一半导体连接部111和第一金属连接部112通过第二过孔h2连接,数据写入晶体管T2通过第三过孔h3与数据信号线Vdata连接。

分支部21还可以包括第二分支部213,第二分支部213在阵列基板100所在平面上的正投影位于第二过孔h2与第三过孔h3在阵列基板所在平面上的正投影之间。可以理解的是,第二分支部213上的电位与第一信号线20上的电位相同,均为固定电位,且由于第二分支部213位于第二过孔h2与第三过孔h3之间,因此第二分支部213形成了第二过孔h2与第三过孔h3之间沿第二方向Y的隔离结构,隔绝第二过孔h2与第三过孔h3之间的信号耦合。

示例性的,第二分支部213可以通过连接分支部212与第一信号线20的本体部200连接。第二分支部213位于连接分支部212远离驱动晶体管T1的一侧。第二分支部213的延伸方向可以和第一信号线20的本体部200的延伸方向相同。

示例性的,第一分支部211、连接分支部212及第二分支部213可以位于同一膜层。

示例性的,如图10所示,第二分支部213可以与第一半导体连接部111及第一金属连接部112中的至少一者交叠,且第二分支部213与第二过孔h2无交叠。第二分支部213与第一半导体连接部111和/或第一金属连接部112所交叠的部分也构成了像素电路10的辅助存储电容,能够进一步增大像素电路10中与驱动晶体管T1的栅极部g电连接的电容的容量,从而进一步提高驱动晶体管T1的栅极电位的稳定性。

可以理解的是,第一分支部211与第一连接部11所交叠的部分构成的辅助存储电容与第二分支部213与第一半导体连接部111和/或第一金属连接部112所交叠的部分构成的辅助存储电容为并联的关系。另外,由于第二分支部213与第二过孔h2无交叠,第二分支部213不同位置的走线宽度可以不同。

在一些可选的实施例中,如图11所示,仍以像素电路10包括栅极初始化晶体管T4和数据写入晶体管T2为例,栅极初始化晶体管T4、数据写入晶体管T2、第一连接部11、数据信号线Vdata及各个过孔的结构及连接方式如上述实施例相同。不同之处在于,连接分支部212在阵列基板所在平面上的正投影可以位于第二过孔h2与第三过孔h3在阵列基板所在平面上的正投影之间,且第一过孔h1位于第二过孔h2远离驱动晶体管T1的一侧。如此连接分支部212可以复用为第二过孔h2与第三过孔h3之间的隔离结构,以隔绝第二过孔h2与第三过孔h3之间的信号耦合,可以不必额外设置如图9或图10所示的第二分支部213。

也就是说,图11所示的连接分支部212在远离驱动晶体管T1方向上的延伸长度大于图9或图10所示的连接分支部212在远离驱动晶体管T1方向上的延伸长度。

在一些可选的实施例中,如图12或图13所示,分支部21还包括第一遮挡部214,像素电路10包括补偿晶体管T3。补偿晶体管T3连接在驱动晶体管T1的栅极与驱动晶体管T1的第二极之间。补偿晶体管T3用于补偿驱动晶体管T1的阈值电压。示例性的,补偿晶体管T3的半导体部与第二扫描信号线S2交叠的部分为补偿晶体管T3的沟道。补偿晶体管T3的沟道受到光照的照射后,会导致补偿晶体管T3的漏电流增大,从而导致驱动晶体管T1的栅极电位不稳定,引起抖屏等问题。本申请实施例中,第一遮挡部214与补偿晶体管T3的沟道至少部分交叠。第一遮挡部214可用于阻挡光线照射至补偿晶体管T3的沟道,降低补偿晶体管T3的漏电流,能够进一步提高驱动晶体管T1的栅极电位的稳定性,改善显示效果。

示例性的,补偿晶体管T3也可以为双栅晶体管,从而进一步提高驱动晶体管T1的栅极电位的稳定性。

另外,补偿晶体管T3为双栅晶体管时,补偿晶体管T3具有两个沟道,第一遮挡部214可以与补偿晶体管T3的两个沟道均至少部分交叠。

示例性的,第一分支部211、连接分支部212及第一遮挡部214可以位于同一膜层。

在一些可选的实施例中,如图13所示,分支部21还包括连接部215,连接部215连接同一行像素电路10所对应的相邻的分支部21。示例性的,连接部215将同一行像素电路10所对应的相邻的第一连接部21连接起来。以第一信号线20的本体部200沿第二方向Y延伸为例,分支部21整体上沿第一方向X延伸,多条本体部200与多条分支部21构成网格状的第一信号线20,能够降低第一信号线20的压降。

在一些可选的实施例中,如图13所示,像素电路10包括数据写入晶体管T2,数据写入晶体管T2通过第三过孔h3与数据信号线Vdata连接,第三过孔h3可以位于连接部215远离驱动晶体管T1的一侧。连接部215构成了第三过孔h3与补偿晶体管T3之间的隔离结构,连接部215可以隔离第三过孔h3与补偿晶体管T3之间的信号耦合,避免crosstalk。

同理,如果将第三过孔h3设置在连接部215靠近驱动晶体管T1的一侧,面临着与第一过孔h1设置在第二扫描信号线S2靠近驱动晶体管T1的一侧相同的问题,能够避免降低PPI,且不会导致增加第三过孔h3的制备难度。

在一些可选的实施例中,如图14所示,分支部21还包括第二遮挡部216,像素电路包括栅极初始化晶体管T4。栅极初始化晶体管T4与驱动晶体管T1的连接关系可以如上文实施例中所述,在此不再赘述。栅极初始化晶体管T4用于为驱动晶体管T1的栅极提供重置电压,以重置驱动晶体管T1的栅极电位。示例性的,栅极初始化晶体管T4的半导体部与第一扫描信号线S1交叠的部分为栅极初始化晶体管T4的沟道。同理,栅极初始化晶体管T4的沟道受到光照的照射后,会导致栅极初始化晶体管T4的漏电流增大,从而导致驱动晶体管T1的栅极电位不稳定,引起抖屏等问题。本申请实施例中,第二遮挡部216与栅极初始化晶体管T4的沟道至少部分交叠。第二遮挡部216可用于阻挡光线照射至栅极初始化晶体管T4的沟道,降低栅极初始化晶体管T4的漏电流,能够进一步提高驱动晶体管T1的栅极电位的稳定性,改善显示效果。

示例性的,如图14所示,第二遮挡部216也可以通过过孔与第一信号线20的本体部200连接。第二遮挡部216也可以通过第一连接部212与第一信号线20的本体部200连接,若第二遮挡部216与参考信号线Vref存在交叠的部分,为了避免信号串扰,可以将第二遮挡部216与参考信号线Vref交叠的部分设置于不同膜层。

示例性的,栅极初始化晶体管T4为双栅晶体管时,栅极初始化晶体管T4具有两个沟道,第二遮挡部216可以与栅极初始化晶体管T4的两个沟道均至少部分交叠。

示例性的,可以将同一行像素电路10对应的相邻的第二遮挡部216连接起来,以第一信号线20的本体部沿第二方向Y延伸为例,第二遮挡部216整体上沿第一方向X延伸,多条本体部200与多条第二遮挡部216也能构成网格状的第一信号线20,进一步降低第一信号线20的压降。

示例性的,第一分支部211、连接分支部212及第二遮挡部216可以位于同一膜层。

在一些可选的实施例中,如图15所示,仍以像素电路10包括栅极初始化晶体管T4为例,栅极初始化晶体管T4通过第一连接部11与驱动晶体管T1的栅极部g电连接。第一连接部11包括第一半导体连接部111和第一金属连接部112,第一半导体连接部111和第一金属连接部112通过第二过孔h2连接。

第一分支部211包括第一子分支部2111和第二子分支部2112,第一子分支部2111靠近第一过孔h1,且第一子分支部2111与第一半导体连接部111交叠;第二子分支部2112靠近驱动晶体管T1的栅极部g,且第二子分支部2112与第一金属连接部112交叠。

本申请实施例中,第一子分支部2111与第一半导体连接部111交叠的部分构成一个辅助存储电容,第二子分支部2112与第一金属连接部112交叠的部分构成另一个辅助存储电容,增加了辅助存储电容的数量,进一步增大了像素电路10中与驱动晶体管T1的栅极部g电连接的电容的容值,能够进一步提高驱动晶体管T1的栅极电位的稳定性,改善显示效果。

可以理解的是,第一子分支部2111与第一半导体连接部111交叠的部分构成的辅助存储电容和第二子分支部2112与第一金属连接部112交叠的部分构成的辅助存储电容是并联的关系。

示例性的,第一子分支部2111、第二子分支部2112与连接分支部212可以位于同一膜层。

在一些可选的实施例中,如图16所示,阵列基板100具有显示区AA和非显示区NA。像素电路设置于显示区AA。阵列基板100还包括设置于非显示区的信号总线30。信号总线30用于提供重置电压信号。同一行像素电路对应的相邻的分支部21相互连接,也就是说,同一行像素电路对应的分支部21构成一条沿行方向延伸的走线,并且分支部21与信号总线30电连接。图11所示的示例可以理解为第一信号线20不包括本体部。另外,图16所示的分支部21相当于复用为了图1所示的参考信号线Vref。

示例性的,分支部21包括第二连接分支部217。像素电路包括阳极初始化晶体管T5和栅极初始化晶体管T4。第二连接分支部217可以与阳极初始化晶体管T5和栅极初始化晶体管T4中的至少一者电连接,信号总线30上的重置电压信号通过分支部21传送给阳极初始化晶体管T5和栅极初始化晶体管T4中的至少一者。可以理解的是,图16所示的示例中分支部21相当于复用为图1所示的参考信号线Vref,不需要再设置参考信号线Vref,相当于可以减少一条参考信号线Vref的布线,压缩在第二方向Y上的pitch,提高PPI。另外,由于减少了一条参考信号线Vref的布线,相当于增加了透光区域的面积,可以增加透光率。

示例性的,仍以第一连接部11包括第一半导体连接部111和第一金属连接部112为例,分支部21与第一金属连接部112交叠构成一个辅助存储电容,且第二连接分支部217与第一半导体连接部111交叠构成另一个辅助存储电容,增加了辅助存储电容的数量,进一步增大了像素电路中与驱动晶体管T1的栅极部g电连接的电容的容值,能够进一步提高驱动晶体管T1的栅极电位的稳定性,改善显示效果。

在一些可选的实施例中,如图17所示,像素电路包括阳极初始化晶体管T5,分支部21与阳极初始化晶体管T5的半导体部通过过孔连接。示例性的,分支部21可以包括第三连接分支部218,分支部21通过第三连接分支部218与半导体部连接。阳极初始化晶体管T5的半导体部还与参考信号线Vref电连接,因此分支部21上的电位与参考信号线Vref上的电位相同均是固定电位,使得分支部21与第一连接部11交叠的部分构成辅助存储电容。

在一些可选的实施例中,如图18所示,仍以像素电路包括栅极初始化晶体管T4和阳极初始化晶体管T5为例,栅极初始化晶体管T4通过第一连接部11与驱动晶体管T1的栅极部g电连接,阵列基板100还包括第二信号线40。第一信号线20用于提供第一重置电压信号,第二信号线40用于提供第二重置电压信号。第一重置电压信号和第二重置电压信号可以不同。第一信号线20与阳极初始化晶体管T5电连接,第二信号线40与栅极初始化晶体管T4电连接。如此,可以为阳极初始化晶体管T5及栅极初始化晶体管T4提供不同的重置电压信号,以满足发光元件的阳极及驱动晶体管T1的栅极的不同的复位需求。

示例性的,如图18所示,第一信号线20包括本体部200,分支部21与本体部连接,且分支部21与阳极初始化晶体管T5的半导体通过过孔连接。

在一些可选的实施例中,如图19所示,如上文所述,阵列基板包括衬底01和设置于衬底上的器件层02,器件层02包括在远离衬底01方向上层叠设置的栅极金属层M1、电容金属层MC及源漏金属层M2。示例性的,栅极金属层M1与衬底01之间设置有半导体层b。各金属层之间以及半导体层b与栅极金属层M1之间设置有绝缘层。

本文中,存储电容Cst的一个极板与驱动晶体管T1的栅极部至少部分重叠,也就是说,本文中的存储电容Cst的一个极板设置于栅极金属层M1,另一个极板设置于电容金属层MC。其中,图19中未示出驱动晶体管T1的源漏极。

在一些可选的实施例中,分支部21设置于电容金属层MC。分支部21和存储电容Cst的另一个极板可以同材质,如此可以在同一工艺步骤中同时形成分支部21和存储电容Cst的另一个极板。

示例性的,第一连接部11的第一半导体连接部111和第一金属连接部112通过第二过孔h2连接。第一半导体连接部111可以设置于半导体层b,第一连接部11的第一金属连接部112可设置于源漏金属层M2。另外,第一金属连接部112通过过孔与驱动晶体管T1的栅极部g连接。

在另一些可选的实施例中,如图20所示,器件层02还包括位于源漏金属层M2背向衬底一侧的走线金属层M3。走线金属层M3为器件层02中任意位于源漏极金属层M2远离衬底01一侧的金属导电层。与图19所示不同的是,数据信号线Vdata可设置于走线金属层M3。如此,数据信号线Vdata与第二过孔h2的距离更远,能够减小据信号线Vdata与第二过孔h2之间的耦合电容,例如在高频驱动下,可以降低crosstalk。

在另一些可选的实施例中,阵列基板的版图布局也可以如图21所示,像素电路10的电路结构也可以如图22所示。图21、图22与图6、图2的相同之处不再赘述,不同之处在于,一方面,图21中的参考信号线包括沿第一方向X延伸的第一参考信号线Vref1和沿第二方向Y延伸的第二参考信号线Vref2,第一参考信号线Vref1和第二参考信号线Vref2电连接限定出多个像素区域,一个像素区域内设置有沿第一方向X排布的三个像素电路10。另一方面,图21中本行像素电路10中的栅极初始化晶体管T4的输入端可以与本行像素电路10对应的第一参考信号线Vref1电连接,本行像素电路10中的第四过孔h4可以与本行的像素电路10中的阳极初始化晶体管T5电连接。又一方面,图21及图22中的栅极初始化晶体管T4和阳极初始化晶体管T5连接不同的扫描信号线,例如,阳极初始化晶体管T5连接第一扫描信号线ScanA,栅极初始化晶体管T4连接第二扫描信号线ScanB,数据写入晶体管T2及补偿晶体管T3连接第三扫描信号线ScanC。

示例性的,第一参考信号线Vref1可以设置于阵列基板的半导体层。

图21中的分支部21可以与图1至图15中任意一项实施例相同,在此不再赘述。

另外,如图21一行像素电路可以包括两条整体上沿第一方向X延伸的分支部21,两条分支部21可以均与第一连接部11交叠,其中一条分支部21可以与补偿晶体管T3的沟道至少部分交叠,另一条分支部21可以与栅极初始化晶体管T4的沟道至少部分交叠。

示例性的,图21中的第一金属连接部112可设置与栅极金属层M1。

示例性的,图6至图18所示的阵列基板可用于小尺寸显示面板中,图21所示的阵列基板可用于大尺寸显示面板中。

需要说明的是,在不矛盾的情况下,上述提供的各实施例可以互相结合。

本申请实施例提供还一种显示面板,包括如上述任一实施例所述的阵列基板。图23示出本申请一种实施例提供的显示面板的结构示意图。如图23所示,该显示面板200包括上述任一实施例所述的阵列基板100及位于阵列基板100上的发光层201。示例性的,发光层201可以是有机发光层,即该显示面板200可以是有机发光二极管(Organic LightEmitting Diode,OLED)显示面板。

本申请还提供了一种显示装置,包括本申请提供的阵列基板。请参考图24,图24是本申请实施例提供的一种显示装置的结构示意图。图24提供的显示装置1000包括本申请上述任一实施例提供的阵列基板100。图24实施例仅以手机为例,对显示装置1000进行说明,可以理解的是,本申请实施例提供的显示装置,可以是可穿戴产品、电脑、电视、车载显示装置等其他具有显示功能的显示装置,本申请对此不作具体限制。本申请实施例提供的显示装置,具有本申请实施例提供的阵列基板的有益效果,具体可以参考上述各实施例对于阵列基板的具体说明,本实施例在此不再赘述。

依照本申请如上文所述的实施例,这些实施例并没有详尽叙述所有的细节,也不限制该申请仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本申请的原理和实际应用,从而使所属技术领域技术人员能很好地利用本申请以及在本申请基础上的修改使用。本申请仅受权利要求书及其全部范围和等效物的限制。

- 阵列基板,显示面板,显示装置及阵列基板的制作方法

- 阵列基板、显示面板、显示装置和阵列基板的制作方法