存储器装置

文献发布时间:2023-06-19 12:02:28

技术领域

本发明是有关于一种存储器装置。

背景技术

随着集成电路中元件的关键尺寸逐渐缩小至制备工艺方法所能感知的极限,设计者已经开始寻找可达到更大存储器密度的技术,从而达到较低的位成本(costs per bit)。

发明内容

本发明是有关于一种存储器装置。

根据本发明的一方面,提出一种存储器装置包括叠层结构、存储元件、通道元件与半导体层。叠层结构包括源极层、绝缘层、与栅电极层。绝缘层在源极层上。栅电极层在绝缘层上。存储元件在栅电极层的电极侧壁表面上。存储单元定义在通道元件与栅电极层之间的存储元件中。半导体层电性连接在源极层与通道元件之间。半导体层与源极层之间具有一接口。接口是横向偏移在绝缘层的一绝缘侧壁表面的内侧。

根据本发明的另一方面,提出一种存储器装置包括叠层结构、存储元件、通道元件与半导体层。叠层结构包括一源极层与多个栅电极层。栅电极层在源极层的相同侧上。存储元件在栅电极层的电极侧壁表面上。存储单元定义在通道元件与栅电极层之间的存储元件中。半导体层电性连接在通道元件与源极层之间。半导体层并包括第一半导体部分与第二半导体部分。第二半导体部分电性连接在第一半导体部分与通道元件之间。第一半导体部分的一半导体侧壁表面是横向偏移在第二半导体部分的一半导体侧壁表面的外侧。

根据本发明的又另一方面,提出一种存储器装置包括叠层结构、存储元件、通道元件与半导体层。叠层结构包括源极层与栅电极层。栅电极层在源极层的相同侧上。存储元件在栅电极层的电极侧壁表面上。存储单元定义在通道元件与栅电极层之间的存储元件中。半导体层包括第一半导体部分与第二半导体部分。第二半导体部分电性连接在第一半导体部分与通道元件之间。第一半导体部分的横向尺寸是大于第二半导体部分的横向尺寸。

为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

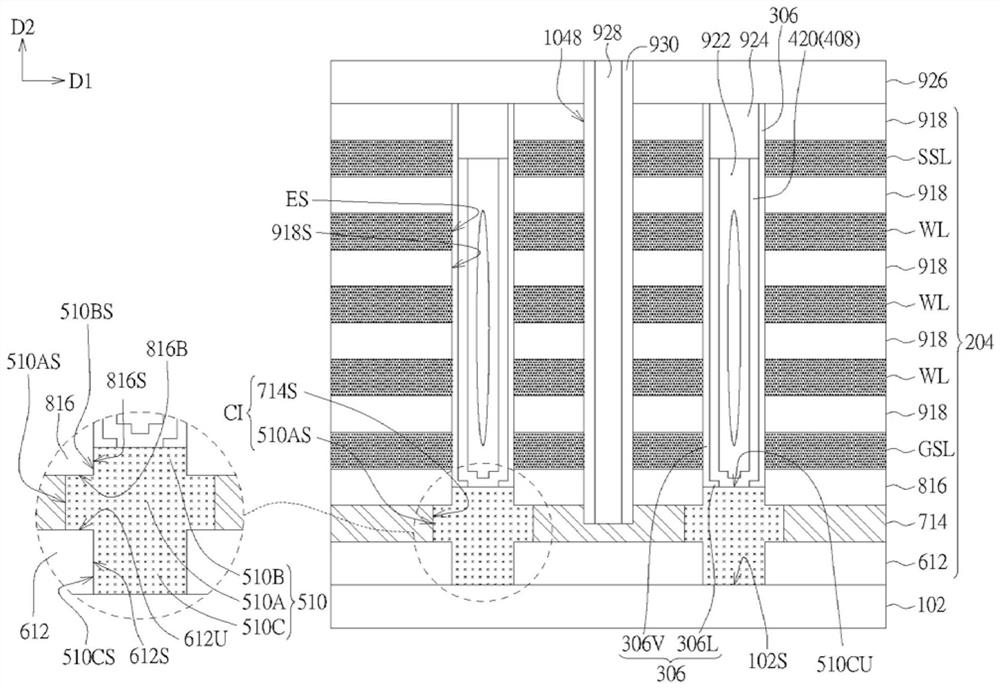

图1绘示一实施例的存储器装置的剖面示意图。

图2绘示另一实施例的存储器装置的剖面示意图。

图3A至图3O绘示一实施例的存储器装置的制造方法。

图4A至图4E绘示另一实施例的存储器装置的制造方法。

【符号说明】

102:半导体衬底

102S:上半导体表面

204:叠层结构

306:存储元件

306L:横向延伸存储部分

306V:纵向延伸存储部分

408:通道元件

420、432、434:通道层

510:半导体层

510A:第一半导体部分

510AS:半导体侧壁表面

510B:第二半导体部分

510BS:半导体侧壁表面

510C:第三半导体部分

510CU:上半导体表面

510CS:半导体侧壁表面

612:绝缘层

612U:上绝缘表面

612S:绝缘侧壁表面

714:源极层

714S:电极侧壁表面

816:绝缘层

816B:下绝缘表面

816S:绝缘侧壁表面

918:绝缘膜

918S:绝缘侧壁表面

922:介电膜

923:空气间隙

924:垫元件

926:介电层

928:导电源极元件

930:介电元件

1036:材料层

1038:开孔

1040:材料层

1042:叠层结构

1044:材料层

1046:凹口

1048:凹槽

1050:氧化层

1052:狭缝

CI:接口

D1:第一方向

D2:第二方向

ES:电极侧壁表面

GSL、SSL、WL:栅电极层

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

以下是以一些实施例做说明。须注意的是,本发明并非显示出所有可能的实施例,未于本发明提出的其他实施例也可能可以应用。再者,图式上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本发明保护范围之用。另外,实施例中的叙述,例如局部结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本发明欲保护的范围做限缩。实施例的步骤和结构各自细节可在不脱离本发明的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

请参照图1,其绘示一实施例的存储器装置的剖面示意图。存储器装置可包括半导体衬底102、叠层结构204、存储元件306、通道元件408与半导体层510。

叠层结构204可包括绝缘层612、源极层714、绝缘层816、栅电极层SSL、栅电极层GSL、栅电极层WL、与绝缘膜918。绝缘层612可在半导体衬底102上。源极层714可在绝缘层612上。绝缘层816可在源极层714上。栅电极层(包括栅电极层SSL、栅电极层GSL、栅电极层WL)与绝缘膜918可交错叠层在绝缘层816上。源极层714与栅电极层(包括栅电极层SSL、栅电极层GSL、栅电极层WL)可通过绝缘层816与绝缘膜918彼此电性隔离。

半导体层510电性连接在源极层714与通道元件408之间。半导体层510可包括第一半导体部分510A、第二半导体部分510B与第三半导体部分510C。第一半导体部分510A可电性连接在第二半导体部分510B与第三半导体部分510C之间。第二半导体部分510B可电性连接在第一半导体部分510A与通道元件408之间。第三半导体部分510C可邻接在半导体衬底102的上半导体表面102S上,并邻接绝缘层612的绝缘侧壁表面612S。

源极层714与半导体层510的第一半导体部分510A之间可具有一接口CI。接口CI包括源极层714的电极侧壁表面714S与第一半导体部分510A的半导体侧壁表面510AS之间相邻接的部分。接口CI可为纵向结晶接口。接口CI是横向偏移在绝缘层816的绝缘侧壁表面816S的内侧。接口CI是横向偏移在绝缘层612的绝缘侧壁表面612S的内侧。本发明中,所谓的横向可为平行于如图所示的第一方向D1的方向。第一方向D1可例如为X方向。半导体层510的第一半导体部分510A可邻接在绝缘层816的下绝缘表面816B与绝缘层612的上绝缘表面612U之间。半导体层510的第一半导体部分510A与第三半导体部分510C可邻接在源极层714与半导体衬底102之间。

举例来说,第一半导体部分510A的半导体侧壁表面510AS、第二半导体部分510B的半导体侧壁表面510BS与第三半导体部分510C的半导体侧壁表面510CS是在半导体层510的相同侧。第一半导体部分510A的半导体侧壁表面510AS可横向偏移在第二半导体部分510B的半导体侧壁表面510BS的外侧。第一半导体部分510A的半导体侧壁表面510AS可横向偏移在第三半导体部分510C的半导体侧壁表面510CS的外侧。第二半导体部分510B的半导体侧壁表面510BS可实质上对齐第三半导体部分510C的半导体侧壁表面510CS。

如图所示,第一半导体部分510A的横向尺寸可大于第二半导体部分510B的横向尺寸。第一半导体部分510A的横向尺寸可大于第三半导体部分510C的横向尺寸。一实施例中,第二半导体部分510B的横向尺寸可相同于第三半导体部分510C的横向尺寸。

源极层714的导电性质可不同于第一半导体部分510A、第二半导体部分510B与第三半导体部分510C的导电性质。半导体衬底102的导电型可相反于源极层714的导电型。一实施例中,半导体衬底102具有P导电型材料。源极层714具有N导电型材料。半导体层510具有未掺杂或P型杂质掺杂的材料。

存储元件306可包括相邻接的横向延伸存储部分306L及纵向延伸存储部分306V。横向延伸存储部分306L在第三半导体部分510C的上半导体表面510CU上。纵向延伸存储部分306V可在栅电极层(包括栅电极层SSL、栅电极层GSL、栅电极层WL)的电极侧壁表面ES、绝缘膜918的绝缘侧壁表面918S与绝缘层816的绝缘侧壁表面816S上。本发明中,所谓的纵向可为平行于如图所示的第二方向D2的方向。第二方向D2可为Z方向。

此实施例中,通道元件408包括通道层420,通道层420可延伸在第三半导体部分510C的上半导体表面510CU、横向延伸存储部分306L的存储侧壁表面与上存储表面、与纵向延伸存储部分306V的存储侧壁表面上。

介电膜922可在通道层420上。垫元件924可在介电膜922上,并电性连接通道元件408。实施例中,垫元件924可电性连接上方的位线接触(未显示),并电性连接位线。介电层926可在叠层结构204上。导电源极元件928可延伸穿过栅电极层SSL、栅电极层GSL、栅电极层WL、绝缘膜918与绝缘层816。导电源极元件928电性连接源极层714。导电源极元件928可通过介电元件930电性隔离栅电极层SSL、栅电极层GSL、栅电极层WL。源极层714与半导体层510的第一半导体部分510A与第二半导体部分510B电性连接在导电源极元件928与通道元件408之间。

存储器装置包括3D垂直通道NAND串列。位于最上层的栅电极层SSL可用做串列选择线,位于最下层的栅电极层GSL可用做接地选择线,两者之间的其它中间层的栅电极层WL可用做字线。存储单元可定义在通道元件408与栅电极层WL之间的存储元件306中。NAND串列包括电性串连的该些存储单元。一实施例中,存储器装置的操作方法包括通过提供电压至栅电极层GSL,以控制半导体层510中反转通道的形成,如此,源极层714与半导体层510之间无PN结,且来自位线的电流路径可依序流经垫元件924、通道元件408、半导体层510、源极层714而至导电源极元件928传出。提供在纵方向上、由下至上的电流路径的源极层714(例如重掺杂N型材料)与导电源极元件928(例如金属材料)可具有低的电阻性质,因此可降低电流路径的整体电阻,可提高存储器装置的操作效率。电流并不会流至导电型(例如P导电型)相反的半导体衬底102中。由于源极线与半导体衬底102之间无PN结,故没有结电容。此可降低电阻电容延迟(RC delay)与较高速度的操作。

请参照图2,其绘示另一实施例的存储器装置的剖面示意图。图2的存储器装置与图1的存储器装置的差异说明如下。此实施例中,通道元件408包括通道层432与通道层434。通道层432可位于横向延伸存储部分306L的上存储表面与纵向延伸存储部分306V的存储侧壁表面上。通道层434可延伸在第三半导体部分510C的上半导体表面510CU、横向延伸存储部分306L的存储侧壁表面与通道层432的通道侧壁表面上。介电膜922可在通道层434上。

一实施例中,如图1所示的存储器装置可利用参照图3A至图3O所示的步骤流程制造。

请参照图3A,提供半导体衬底102。半导体衬底102可包括例如硅衬底,或其它合适的半导体材料。半导体衬底102可包括第一导电型材料,例如以第一导电型杂质掺杂的材料,例如P型井区。可在半导体衬底102上形成叠层结构1042。一实施例中,可在半导体衬底102上形成绝缘层612。可在绝缘层612上形成源极层714。源极层714可包括第二导电型材料,例如以第二导电型杂质掺杂的材料。一实施例中,源极层714包括N型材料,例如重掺杂的N型材料。可在源极层714上形成绝缘层816。可在绝缘层816上交错叠层绝缘膜918与材料层1036。绝缘层612、绝缘层816与绝缘膜918的材质可不同于材料层1036的材质。一实施例中,绝缘层612、绝缘层816与绝缘膜918的材质可包括氧化物例如氧化硅。材料层1036的材质可包括氮化物例如氮化硅。但本发明不限于此。

请参照图3B,可利用黄光光刻刻蚀工艺进行图案化步骤,以形成开孔1038穿过绝缘膜918、材料层1036、绝缘层816、源极层714与绝缘层612,并露出半导体衬底102。半导体衬底102可用作刻蚀停止层。一实施例中,开孔1038露出的层膜的侧壁表面可彼此对齐。

请参照图3C,可在开孔1038的底部形成材料层1040。材料层1040可利用沉积方式形成。一实施例中,可利用选择性外延方法,从露出开孔1038的源极层714的电极侧壁表面714S与半导体衬底102的上半导体表面102S成长出邻接在源极层714与半导体衬底102之间的材料层1040。实施例中,材料层1040并不限于如图所示的轮廓,而可包含从电极侧壁表面714S与上半导体表面102S外延成长的任何可能轮廓。举例来说,材料层1040的上表面可能为平整的表面或非平整的表面。一实施例中,材料层1040可为半导体层,材料包括例如SiGe

请参照图3D,可利用沉积方法形成存储元件306在开孔1038中与叠层结构1042的上表面上。存储元件306可包括任意的电荷捕捉结构,例如一氧化物-氮化物-氧化物(ONO)结构、ONONO结构、ONONONO结构、或一氧化物-氮化物-氧化物-氮化物-氧化物(BE-SONOS)结构等。举例来说,电荷捕捉层可使用氮化物例如氮化硅,或是其他类似的高介电常数物质包括金属氧化物,例如三氧化二铝(Al

请参照图3E,可形成材料层1044在存储元件306上。一实施例中,材料层1044可包括未掺杂的多晶硅材料。但本发明不限于此,材料层1044亦可使用其它合适的材质。

请参照图3F,可利用非等向刻蚀方式,移除材料层1044在开孔1038中的底部分与在叠层结构1042的上表面上的部分,留下材料层1044位于开孔1038的侧壁上的部分。然后,可利用合适的刻蚀方式,移除存储元件306未被材料层1044遮盖的部分,从而露出材料层1040。

请参照图3G,可利用合适的刻蚀方式移除图3F所示的材料层1044。一实施例中,此刻蚀步骤可使用湿式刻蚀方法,可使用例如NH

请参照图3H,可利用合适的刻蚀方式移除图3G所示的材料层1040。一实施例中,选用的刻蚀方式可对材料层1040具有刻蚀选择性,而实质上不刻蚀其它元件,例如源极层714、半导体衬底102等。

请参照图3I,可对源极层714进行回刻蚀步骤以形成与开孔1038连通的凹口1046,并使源极层714的电极侧壁表面,从如图3H所示实质上可对准绝缘层816的绝缘侧壁表面816S与绝缘层612的绝缘侧壁表面612S的位置,向源极层714的内部横向转移成为电极侧壁表面714S。电极侧壁表面714S偏移在绝缘层816的绝缘侧壁表面816S的内侧,并偏移在绝缘层612的绝缘侧壁表面612S的内侧。一实施例中,源极层714被刻蚀掉的部分的横向尺寸(或电极侧壁表面714S的横向偏移尺寸,或凹口1046的横向尺寸)可例如为5nm至50nm,例如为20nm,但本发明并不限于此。选用的回刻蚀方式可对源极层714具有刻蚀选择性,而实质上不刻蚀其它元件,例如绝缘层816与绝缘层612等。一实施例中,回刻蚀可使用湿式刻蚀方法,可使用例如NH

请参照图3J,可在开孔1038的底部与凹口1046中形成半导体层510。半导体层510可包括硅,例如多晶硅或单晶硅等。半导体层510可利用沉积方式形成。一实施例中,可利用选择性外延方法,从露出凹口1046的源极层714的电极侧壁表面714S与半导体衬底102的上半导体表面102S成长出邻接在源极层714、半导体衬底102与存储元件306之间的半导体层510,且半导体层510与源极层714可具有接口CI,半导体层510与半导体衬底102之间亦可具有接口例如结晶接口。实施例中,半导体层510并不限于如图所示的轮廓,而可包含从电极侧壁表面714S与上半导体表面102S外延成长的任何可能轮廓。举例来说,半导体层510的上表面可能为平整的表面或非平整的表面。

一实施例中,相邻接的半导体层510与源极层714是以不同的掺杂状态形成。举例来说,半导体层510的形成材料包括未掺杂的半导体材料,或者以P型杂质掺杂的半导体材料,且邻接半导体层510的源极层714的形成材料包括N型杂质掺杂的半导体材料,例如重掺杂的N型半导体材料。此实施例中,半导体层510是在存储元件306之后形成,因此不会经历形成存储元件306使用的高温工艺,能限制源极层714的N型掺杂杂质扩散至半导体层510中。此外,半导体层510的第一半导体部分510A形成在凹口1046内的部分(亦即,延伸在绝缘层612的上绝缘表面612U与绝缘层816的下绝缘表面816B之间的部分,或者,延伸超过绝缘层816的绝缘侧壁表面816S与绝缘层612的绝缘侧壁表面612S的部分)亦可提供来自源极层714的N型杂质的可接受扩散范围,从而避免N型杂质的过度扩散(例如扩散至超过绝缘层816的绝缘侧壁表面816S/绝缘层612的绝缘侧壁表面612S)造成存储器装置操作效能降低的问题。

请参照图3K,可形成通道层420在存储元件306、半导体层510与叠层结构1042的上表面上。一实施例中,通道层420包括未掺杂的多晶硅材料。但本发明不限于此,通道层420亦可使用其它合适的材质。

请参照图3L,可形成介电膜922在开孔1038中。介电膜922可利用适合的沉积方式形成。介电膜922例如可为非共形的材料膜,并具有空气间隙(air gap)923于其中。一实施例中,介电膜922可包括氧化物例如氧化硅,但不限于此,亦可使用其它合适的介电材料。可利用化学机械研磨方法移除在叠层结构1042的上表面上的介电膜922。化学机械研磨工艺可停止在通道层420上。然后,可对介电膜922与通道层420进行回刻蚀步骤以形成凹口。可形成垫元件924在凹口中。一实施例中,垫元件924可包括导电材料或半导体材料,例如N型半导体材料,例如重掺杂的N型半导体材料。垫元件924可利用沉积方式形成,并可利用化学机械研磨方法移除沉积在叠层结构1042的上表面上的沉积材料。化学机械研磨步骤可停止在叠层结构1042中最顶的绝缘膜918(用作硬掩模)上。一实施例中,垫元件924将可提供上方的元线接触(bit line contact)的着陆区,并电性连接至位线。

请参照图3M,可形成介电层926。介电层926可用作盖层,用以保护垫元件924。一实施例中,介电层926可包括绝缘材料,包括氧化物例如氧化硅,或使用其它合适的材质。可利用黄光光刻刻蚀工艺,形成凹槽1048穿过介电层926、绝缘膜918、材料层1036与绝缘层816,并露出源极层714。一实施例中,刻蚀步骤可利用源极层714作为刻蚀停止层。然后,可对露出凹槽1048的源极层714进行氧化步骤以形成氧化层1050在源极层714的上电极表面上。

请参照图3N,可进行刻蚀步骤移除如图3M所示的凹槽1048露出的材料层1036以形成狭缝1052。狭缝1052可露出绝缘膜918的上绝缘表面/下绝缘表面、绝缘层816的上绝缘表面及存储元件306的存储侧壁表面。一实施例中,可利用湿式刻蚀法,将如图3M所示的结构浸泡在对材料层1036具有刻蚀选择性的刻蚀溶液(例如包含磷酸(H

请参照图3O,可形成栅电极层SSL、栅电极层GSL与栅电极层WL填充狭缝1052。一实施例中,在栅电极层SSL、栅电极层GSL与栅电极层WL形成之前,可形成介电薄膜(未显示)在狭缝1052露出的元件表面上,然后形成栅电极层SSL、栅电极层GSL与栅电极层WL在介电薄膜上并填满狭缝1052。介电薄膜可例如包括高介电系数(high-k)材料,或其它适当的介电材料。一实施例中,可利用合适的刻蚀方式移除形成在凹槽1048中的栅电极材料/介电材料,及氧化层1050。

可往回参照图1,可形成介电元件930在凹槽1048露出的元件侧壁表面上。一实施例中,介电元件930的形成方法可包括利用沉积工艺形成介电薄膜在凹槽1048中与介电层926的上表面上,然后,可利用非等向刻蚀工艺移除介电薄膜位于凹槽1048的底部与介电层926的上表面上的部分,刻蚀工艺留下的介电薄膜形成介电元件930。一实施例中,介电元件930可包括氧化物例如氧化硅,但本发明不限于此。然后,可形成导电源极元件928填充凹槽1048并电性连接源极层714。一实施例中,导电源极元件928的形成方法可包括利用合适的沉积方式形成导电材料在凹槽1048中与介电层926的上表面上,然后,可利用化学机械研磨方法移除在介电层926的上表面上的导电材料。导电材料可包括合金或金属,例如氮化钛(TiN)或钨(W)等。

另一实施例中,如图2所示的存储器装置可利用如图4A至图4E所示的步骤流程制造。举例来说,可在进行参照图3A至图3B所述的制造流程之后,进行如图4A所示的步骤。

请参照图4A,可对源极层714进行回刻蚀步骤以形成与开孔1038连通的凹口1046,并使源极层714的电极侧壁表面,从实质上可对准绝缘层816的绝缘侧壁表面816S与绝缘层612的绝缘侧壁表面612S的位置,向源极层714的内部横向转移成为电极侧壁表面714S。

请参照图4B,可在开孔1038的底部与凹口1046中形成半导体层510。半导体层510可包括硅,例如多晶硅、单晶硅等。半导体层510可利用沉积方式形成。一实施例中,可利用选择性外延方法,从露出凹口1046的源极层714的电极侧壁表面714S与半导体衬底102的上半导体表面102S成长出邻接在源极层714与半导体衬底102之间的半导体层510。实施例中,半导体层510并不限于如图所示的轮廓,而可包含从电极侧壁表面714S与上半导体表面102S外延成长的任何可能轮廓。举例来说,半导体层510的上表面可能为平整的表面或非平整的表面。一实施例中,可进行热退火步骤以例如消除材料中的空隙(void)。

请参照图4C,可形成存储元件306在开孔1038中及叠层结构1042的上表面上。然后,可形成通道层432在存储元件306上。通道层432可例如包括利用沉积工艺形成的未掺杂的多晶硅,但本发明不限于此。

请参照图4D,可利用非等向刻蚀方式,移除通道层432在开孔1038中的底部分与在叠层结构1042的上表面上的部分,留下通道层432位于开孔1038的侧壁上的部分。然后,可利用合适的刻蚀方式,移除存储元件306未被通道层432遮盖的部分,从而露出半导体层510。

请参照图4E,可形成通道层434在开孔1038中与叠层结构1042的上表面上。通道层434可例如包括利用沉积工艺形成的未掺杂的多晶硅,但本发明不限于此。

然后,可进行类似参照如图3L至图3O与图1所述制造概念形成介电膜922、垫元件924、介电层926、栅电极层SSL、栅电极层GSL、栅电极层WL、介电元件930、导电源极元件928,从而形成如图2所示的存储器装置。

本发明的存储器装置并不限如上所述的制造方法,并可适当调变。一实施例中,举例来说,可在参照图3D所述形成存储元件306之后,利用非等向刻蚀方式移除存储元件306在开孔1038底部的部分与叠层结构1042的上表面上的部分,并可省略参照图3E与图3F说明的材料层1044的形成/移除步骤,然后进行参照图3G及之后相关的制造步骤,亦可形成类似如图1所示的存储器装置。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 存储器装置、存储器装置构造、构造、存储器装置形成方法、电流传导装置及存储器单元编程方法

- 存储器装置、主机装置、存储器系统、存储器装置控制方法、主机装置控制方法以及存储器系统控制方法