一种CMOS数字集成电路总剂量效应建模方法及系统

文献发布时间:2023-06-19 12:27:31

技术领域

本发明属于数字器件辐照效应模型的建模技术领域,尤其涉及一种CMOS数字集成电路总剂量效应建模方法及系统。

背景技术

目前,随着半导体技术的飞速发展,各种模拟、数字集成电路被广泛应用于航空航天、核工业及粒子物理等领域,它们处在各种电磁、高能粒子的辐射环境中,受到总剂量辐射、单粒子辐射及瞬时效应等多种辐射效应的影响,其工作可靠性及寿命周期受到了严峻的考验。其中,总剂量辐射效应更是受到了广泛的关注与研究。

近年来,随着计算机仿真技术的发展,电子系统辐射效应仿真为系统抗辐射设计、理论研究提供了有力支持,既缩短了研发周期又减少了开发费用。目前,对数字集成电路的总剂量效应建模研究主要有基于底层物理的晶体管级模型(SPICE模型)研究与基于功能的行为模型(IBIS模型)研究两类。晶体管级模型仿真精度高,适用范围广,但其计算开销大,仿真的电路规模受限,且由于物理模型涉及知识产权信息,半导体厂商往往不愿提供相应模型或对模型加密,难以用于总剂量效应的建模工作。行为级模型不涉及底层物理,模型简单,通用性好且仿真效率高,但IBIS模型描述的工作点固定,不同供电电压对应不同的IBIS模型,因此不能准确描述芯片供电电压不为设定值时的特性。其次,在对器件总剂量效应建模时,一个IBIS模型仅能描述特定总剂量点时的电特性,无法准确表征中间剂量点时的情况。

综上所述,现有的数字集成电路总剂量效应建模方法只能表征器件端口的行为特性,无法准确、连续地表征不同条件下器件的电特性。

通过上述分析,现有技术存在的问题及缺陷为:

(1)目前对数字集成电路的总剂量效应建模研究中,晶体管级模型SPICE计算开销大,仿真的电路规模受限,且由于物理模型涉及知识产权信息,半导体厂商往往不愿提供相应模型或对模型加密,难以用于总剂量效应的建模工作。

(2)行为级模型IBIS描述的工作点固定,不同供电电压对应不同的IBIS模型,因此不能准确描述芯片供电电压不为设定值时的特性。

(3)在对器件总剂量效应建模时,一个IBIS模型仅能描述特定总剂量点时的电特性,无法准确表征中间剂量点时的情况。

(4)现有的数字集成电路总剂量效应建模方法只能表征数字器件端口的行为特性,无法准确、连续地表征不同条件下器件的电特性问题。

解决以上问题及缺陷的难度为:

如何建立器件的总剂量效应模型,使得其既能反应器件的行为特性,又能表征器件端口的物理特性,并能根据总剂量效应对器件端口开关管的影响造成的器件功能退化,通过器件端口的物理模型参数变化体现。

解决以上问题及缺陷的意义为:

解决了物理模型获取困难、仿真复杂度高以及行为模型环境适用性不好的问题,为数字集成电路的抗辐照设计与研究提供了途径与参考。

发明内容

针对现有技术存在的问题,本发明提供了一种CMOS数字集成电路总剂量效应建模方法及系统,旨在解决现有的数字集成电路总剂量效应建模方法只能表征数字器件端口的行为特性,无法准确、连续地表征不同条件下器件的电特性问题。

本发明是这样实现的,一种CMOS数字集成电路总剂量效应建模方法,所述CMOS数字集成电路总剂量效应建模方法包括以下步骤:

步骤一,选择或设计一种数字器件作为原始器件;

步骤二,对原始数字器件用仪器测量或者在元器件官网下载获得原始器件的IBIS模型数据;

步骤三,基于IBIS模型数据提取输入端口的钳位管特性曲线和输出端口的晶体管特性曲线;

步骤四,根据钳位管特性曲线提取二极管模型参数;

步骤五,根据晶体管特性曲线提取MOS管模型参数;

步骤六,根据提取的模型参数建立CMOS数字IC行为-物理混合模型;

步骤七,根据总剂量效应引起的时序变化建立CMOS数字IC时序退化模型;

步骤八,根据总剂量效应造成的器件电特性退化,建立CMOS数字IC输出端口总剂量效应模型。

其中,步骤一和步骤二在本方案中起到的积极作用是获取某一确定器件的基础模型数据,为后面的建模工作做准备;

步骤三在本方案中起到的积极作用是提取器件特征曲线,为提取模型参数做准备;

步骤四在本方案中起到的积极作用是为构建具有物理特性的输入端口模型做准备;

步骤五在本方案中起到的积极作用是为构建具有物理特性的输出端口模型做准备;

步骤六在本方案中起到的积极作用是建立器件的常态模型,便于在此基础上添加总剂量效应;

步骤七在本方案中起到的积极作用是能更准确的体现数字IC行为-物理混合模型的时序特征;

步骤八在本方案中起到的积极作用是在步骤六建立的常态模型和步骤七建立的时序退化模型基础上,考虑总剂量效应对输出端口的电特性影响,最终建立CMOS数字IC输出端口总剂量效应模型。

进一步,步骤二中,所述原始电子器件的IBIS模型的构建,包括:

采用SPICE仿真方法或者真实器件直接测量的方法,测得原始电子器件的IV数据和VT数据;其中,所述IV数据表示电流电压关系,包括上拉下拉I/V数据Pullup、Pulldown以及电源和GND钳位数据Power_Clamp、Gnd_Clamp;所述VT数据表示电压时间关系,包括上升波形的VT数据和下降波形的VT数据;将数据录入IBIS文件,完成IBIS模型的创建。

进一步,步骤三中,所述基于IBIS模型数据提取输入端口的钳位管特性曲线和输出端口的晶体管特性曲线,包括:

基于IBIS模型数据,提取原始器件输入端口电源钳位管和地钳位管的特性曲线,提取原始器件输出端口PMOS管与地钳位管特性曲线和NMOS管与电源钳位管特性曲线。

其中,基于IBIS模型提取输入端口钳位管特性曲线时,Power_Clamp数据描述当输入电压高于器件供电电压VCC时该输入端口的电压、电流关系,端口地钳位管反向截止,电源钳位管正向导通,该组数据即为电源钳位管的V/I特性曲线;由于IBIS模型规定Power_Clamp数据表中的电压V

基于IBIS模型提取输入端口钳位管特性曲线时,GND_Clamp描述当输入电压低于GND时输入引脚的电压、电流特性;电源钳位管反向截止,地钳位管正向导通,故GND_Clamp数据即为地钳位管V/I特性曲线;根据IBIS模型规定,GND_Clamp数据表中的电压V

基于IBIS模型提取输出端口PMOS管和地钳位管特性曲线时,提取输出引脚电压-VCC~VCC范围间的V-I数据,即对应Pullup曲线2VCC~0V区间的数据;推挽输出端口,Pullup曲线融合上拉管与钳位管的电特性;当输出引脚电压处于0V~VCC之间时,上拉管PMOS导通,此时的V-I曲线即为PMOS管输出特性曲线;当输出端口电压小于0V时,PMOS管与地钳位管二极管均导通,Pullup电流数据I

基于IBIS模型提取输出端口NMOS管和电源钳位管特性曲线时,输出端口电压V

进一步,步骤四中,所述根据钳位管特性曲线提取二极管模型参数,包括:

基于钳位管特性曲线,选择合适的二极管模型方程,在钳位管特性曲线上选择若干参考点,带入模型方程,利用非线性对消二乘优化技术对模型方程与特性曲线进行拟合,得到模型方程中二极管的参数:

(1)选择二极管模型方程:

其中,I

(2)在二极管正向区电压-电流特性曲线中选取三个参考点(V

当选取的参考点电压远大于热电压V

解所述方程组(3)可得寄生电阻R和发射系数n的值;

(3)在二极管正向区电压-电流特性曲线中选取一点(V

进一步,步骤五中,所述根据晶体管特性曲线提取MOS管模型参数,包括:

基于晶体管特性曲线,选择合适的MOS管模型方程,在晶体管特性曲线上选择参考点,带入模型方程,利用非线性对消二乘优化技术对模型方程与特性曲线进行拟合,得到模型方程中MOS管的参数:

(1)利用线性外推法原理提取MOS管的阈值电压;当漏电压V

(2)根据MOS管在线性区漏极电压V

从MOS管输出特性曲线线性区选取两点,代入关系式,计算得MOS管饱和电压

(3)获得饱和电压V

(4)根据公式(4)得到电导系数

(5)根据MOS管在饱和区,饱和电压V

从MOS管特性曲线的饱和区任选两点(V

进一步,步骤六中,所述根据提取的模型参数建立CMOS数字IC行为-物理混合模型,包括:

根据原始器件的数据手册真值表,建立原始器件功能区VHDL模型;根据得到的二极管参数,建立原始器件输入端口的VHDL-AMS模型;根据得到的MOS管参数,建立原始器件输出端口的VHDL-AMS模型,由此建立的模型为CMOS数字IC行为-物理混合模型;

其中,根据辐照试验数据,确定原始器件输入端口到输出端口的传播时延,对所述功能区VHDL模型进行重构。

进一步,步骤六中,所述根据提取的模型参数建立CMOS数字IC行为-物理混合模型,还包括:

(1)构建CMOS数字IC功能区模型,根据器件手册中的真值表,用VHDL语言描述器件的功能;

(2)构建CMOS数字IC输入端口模型,根据器件数据手册中元件的模型参数和提取的二极管模型参数,用VHDL-AMS语言建立输入端口模型;

(3)构建CMOS数字IC输出端口模型,根据器件数据手册中元件的模型参数和提取的二极管模型参数及MOS管模型参数,用VHDL-AMS语言建立输入端口模型;

(4)根据所述数字IC功能区模型、输入端口模型和输出端口模型共同构成CMOS数字IC行为-物理混合模型。

进一步,所述器件数据手册中元件的模型参数,包括封装电容C_comp、引脚寄生电阻R_pkg、引脚寄生电感L_pkg和引脚寄生电容C_pkg;所述二极管模型参数,包括电源/地钳位二极管反向饱和电流I

进一步,步骤八中,所述根据总剂量效应造成的器件电特性退化,建立CMOS数字IC输出端口总剂量效应模型,包括:

对原始器件输出端口开关晶体管的阈值电压、载流子迁移率建立总剂量效应模型,即为CMOS数字IC输出端口总剂量效应模型:

(1)根据总剂量效应造成的阈值电压漂移ΔV

其中,q为电子电荷量,N

在CMOS数字IC总剂量效应模型文件中引入总剂量参数D,在仿真时根据传入模型的总剂量D计算出该总剂量D下实际的阈值电压V

(2)根据总剂量效应引起的器件沟道载流子迁移率退化,根据辐射诱导界面态电荷ΔQ

其中,μ

在CMOS数字IC总剂量效应模型文件中引入总剂量参数D,在仿真时根据传入模型的总剂量D计算出该总剂量D下实际的载流子迁移率μ。

至此,CMOS数字集成电路总剂量效应建模完毕。

本发明的另一目的在于提供一种应用所述的CMOS数字集成电路总剂量效应建模方法的CMOS数字集成电路总剂量效应建模系统,所述CMOS数字集成电路总剂量效应建模系统包括:

原始器件获取模块,用于通过选择或设计一种数字器件作为原始器件;

IBIS模型数据获取模块,用于对原始数字器件用仪器测量或者在元器件官网下载获得原始器件的IBIS模型数据;

特性曲线提取模块,用于基于IBIS模型数据提取输入端口的钳位管特性曲线和输出端口的晶体管特性曲线;

模型参数提取模块,用于根据钳位管特性曲线提取二极管模型参数,同时根据晶体管特性曲线提取MOS管模型参数;

混合模型构建模块,用于根据提取的模型参数建立CMOS数字IC行为-物理混合模型;

时序退化模型构建模块,用于根据总剂量效应引起的时序变化建立CMOS数字IC时序退化模型;

总剂量效应模型构建模块,用于根据总剂量效应造成的器件电特性退化,建立CMOS数字IC输出端口总剂量效应模型。

结合上述的所有技术方案,本发明所具备的优点及积极效果为:本发明提供的CMOS数字集成电路总剂量效应建模方法,是对辐照条件下的集成电路进行输入输出缓冲区电特性建模的方法,所建立的IBIS辐照模型可直接用于辐照条件下电子系统的仿真分析。本发明改进了基于IBIS模型的行为级建模方法,用该方法建立的模型既能反映CMOS数字器件的逻辑功能,又能体现端口的模拟特性,为在辐照条件下进行系统仿真提供模型支持。

附图说明

为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例中所需要使用的附图做简单的介绍,显而易见地,下面所描述的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下还可以根据这些附图获得其他的附图。

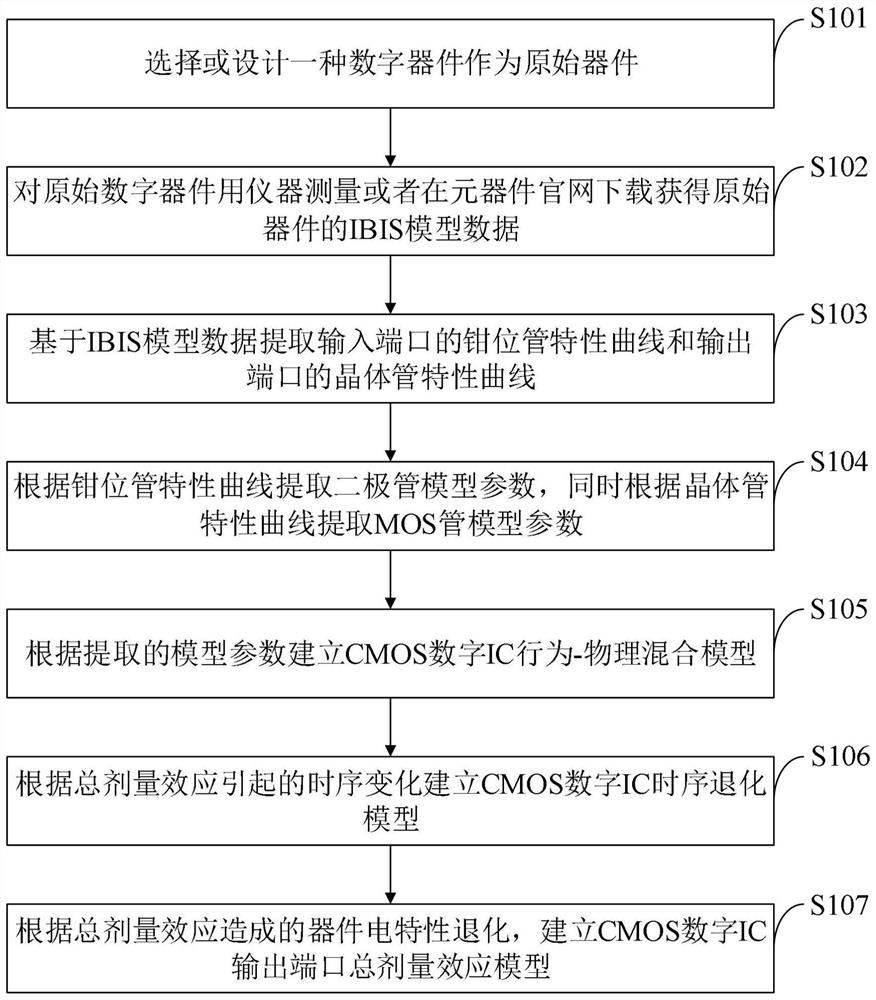

图1是本发明实施例提供的CMOS数字集成电路总剂量效应建模方法流程图。

图2是本发明实施例提供的CMOS数字集成电路总剂量效应建模系统结构框图;

图中:1、原始器件获取模块;2、IBIS模型数据获取模块;3、特性曲线提取模块;4、模型参数提取模块;5、混合模型构建模块;6、时序退化模型构建模块;7、总剂量效应模型构建模块。

图3是本发明实施例提供的IBIS模型一般结构图。

图4是本发明实施例提供的输入端口Power_Clamp示意图。

图5是本发明实施例提供的输入端口GND_Clamp示意图。

图6是本发明实施例提供的输出端口Pullup示意图。

图7是本发明实施例提供的输出端口Pulldown示意图。

图8是本发明实施例提供的提取二极管模型参数流程图。

图9是本发明实施例提供的提取MOS管模型参数流程图。

图10是本发明实施例提供的建立CMOS数字IC行为-物理混合模型流程图。

图11是本发明实施例提供的CMOS数字IC输出端口总剂量效应建模流程示意图。

图12是本发明实施例提供的总剂量试验环境图。

图中:1、NC7SZ157测试电路;2、钴源;3、总剂量试验台架。

图13是本发明实施例提供的总剂量辐照试验条件图。

图14是本发明实施例提供的NC7SZ157不同总剂量下上升沿波形图。

图15是本发明实施例提供的NC7SZ157不同总剂量下下降沿波形图。

图16是本发明实施例提供的NC7SZ157总剂量为0K时仿真结果与测试结果对比图。

图17是本发明实施例提供的NC7SZ157总剂量为50K时仿真结果与测试结果对比图。

图18是本发明实施例提供的NC7SZ157总剂量为150K时仿真结果与测试结果对比图。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

针对现有技术存在的问题,本发明提供了一种CMOS数字集成电路总剂量效应建模方法及系统,下面结合附图对本发明作详细的描述。

如图1所示,本发明实施例提供的CMOS数字集成电路总剂量效应建模方法包括以下步骤:

S101,选择或设计一种数字器件作为原始器件;

S102,对原始数字器件用仪器测量或者在元器件官网下载获得原始器件的IBIS模型数据;

S103,基于IBIS模型数据提取输入端口的钳位管特性曲线和输出端口的晶体管特性曲线;

S104,根据钳位管特性曲线提取二极管模型参数,同时根据晶体管特性曲线提取MOS管模型参数;

S105,根据提取的模型参数建立CMOS数字IC行为-物理混合模型;

S106,根据总剂量效应引起的时序变化建立CMOS数字IC时序退化模型;

S107,根据总剂量效应造成的器件电特性退化,建立CMOS数字IC输出端口总剂量效应模型。

如图2所示,本发明实施例提供的CMOS数字集成电路总剂量效应建模系统包括:

原始器件获取模块1,用于通过选择或设计一种数字器件作为原始器件;

IBIS模型数据获取模块2,用于对原始数字器件用仪器测量或者在元器件官网下载获得原始器件的IBIS模型数据;

特性曲线提取模块3,用于基于IBIS模型数据提取输入端口的钳位管特性曲线和输出端口的晶体管特性曲线;

模型参数提取模块4,用于根据钳位管特性曲线提取二极管模型参数,同时根据晶体管特性曲线提取MOS管模型参数;

混合模型构建模块5,用于根据提取的模型参数建立CMOS数字IC行为-物理混合模型;

时序退化模型构建模块6,用于根据总剂量效应引起的时序变化建立CMOS数字IC时序退化模型;

总剂量效应模型构建模块7,用于根据总剂量效应造成的器件电特性退化,建立CMOS数字IC输出端口总剂量效应模型。

下面结合实施例对本发明的技术方案作进一步描述。

实施例1

本发明是这样实现的,一种CMOS数字集成电路总剂量效应建模方法,所述一种CMOS数字集成电路总剂量效应建模方法是对原始数字器件用仪器测量或者在元器件厂商官网下载获得器件的IBIS模型数据;基于IBIS模型提取输入端口钳位管特性曲线和输出端口晶体管特性曲线;根据钳位管特性曲线提取二极管模型参数;根据晶体管特性曲线提取MOS管模型参数;根据提取的模型参数建立CMOS数字IC行为-物理混合模型;根据总剂量效应引起的时序变化,建立时序退化模型;根据总剂量效应造成的器件电特性退化,最终建立输出端口总剂量效应模型。

本发明通过对原始数字器件用测试仪器测量或者在元器件厂商官网下载获得数字器件的IBIS模型数据。

本发明基于IBIS模型数据,提取器件输入端口电源钳位管和地钳位管的特性曲线,提取器件输出端口PMOS管与地钳位管特性曲线和NMOS管与电源钳位管特性曲线。

本发明基于钳位管特性曲线,选择合适的二极管模型方程,在钳位管特性曲线上选择若干参考点,带入模型方程,得到模型方程中二极管的参数。

本发明基于晶体管特性曲线,选择合适的MOS管模型方程,在晶体管特性曲线上选择参考点,带入模型方程,得到模型方程中MOS管的参数。

本发明根据器件的数据手册真值表,建立器件功能区VHDL模型;根据得到的二极管参数,建立器件输入端口的VHDL-AMS模型;根据得到的MOS管参数,建立器件输出端口的VHDL-AMS模型,由此建立的模型为CMOS数字IC行为-物理混合模型。

本发明根据辐照试验数据,确定器件输入端口到输出端口的传播时延,功能区VHDL模型重构。

本发明对器件输出端口开关晶体管的阈值电压、载流子迁移率建立总剂量效应模型,即为CMOS数字IC输出端口总剂量效应模型。

本发明的另一目的在于提供一种利用所述CMOS数字集成电路总剂量效应建模方法构建的数字器件总剂量效应模型以及一种普适的辐照条件下数字器件输入输出缓冲区电特性建模的方法。

本发明提供的CMOS数字集成电路总剂量效应建模方法,是对辐照条件下的集成电路进行输入输出缓冲区电特性建模的方法,所建立的IBIS辐照模型可直接用于辐照条件下电子系统的仿真分析。

实施例2

首先为了进行建模,需要选取原始电子器件,原始器件可以是选择市面上已有的器件,也可以自己设计制造一种电子器件。获取原始电子器件的IBIS模型,可以采用SPICE仿真方法或者真实器件直接测量的方法,测得其IV数据、VT数据(IV数据表示电流电压关系,包括上拉下拉I/V数据Pullup、Pulldown以及电源和GND钳位数据Power_Clamp、Gnd_Clamp;VT数据表示电压时间关系,包括上升波形的VT数据和下降波形的VT数据,如图3所示)等,将数据录入IBIS文件,完成模型的创建(对于市面上买到的器件,还可以直接从厂家那里获取原始器件的IBIS模型)。

基于IBIS模型提取输入端口钳位管特性曲线时,Power_Clamp数据描述当输入电压高于器件供电电压VCC时该输入端口的电压、电流关系,此时,端口地钳位管反向截止,电源钳位管正向导通(如图4所示),由于二极管反向电流远小于正向导通电流且输入Buffer反相器栅极泄露电流很小,通常可忽略,因此可认为该组数据即为电源钳位管的V/I特性曲线。由于IBIS模型规定Power_Clamp数据表中的电压V

基于IBIS模型提取输入端口钳位管特性曲线时,GND_Clamp描述当输入电压低于GND时输入引脚的电压、电流特性。此时,电源钳位管反向截止,地钳位管正向导通(如图5所示),因此,GND_Clamp数据即为地钳位管V/I特性曲线。根据IBIS模型规定,GND_Clamp数据表中的电压V

基于IBIS模型提取输出端口PMOS管和地钳位管特性曲线时,为获得PMOS的输出特性,应提取输出引脚电压-VCC~VCC范围间的V-I数据,即对应Pullup曲线2VCC~0V区间的数据,此时输出端口的电流情况如图6所示。对于推挽输出端口,Pullup曲线融合了上拉管与钳位管的电特性。当输出引脚电压处于0V~VCC之间时,上拉管PMOS导通,此时的V-I曲线即为PMOS管输出特性曲线。如图6所示,当输出端口电压小于0V时,PMOS管与地钳位管二极管均导通,Pullup电流数据I

基于IBIS模型提取输出端口NMOS管和电源钳位管特性曲线时,输出端口电压V

有了钳位二极管特性曲线后,提取二极管参数时,选择合适的器件模型,利用非线性对消二乘优化技术对模型方程与特性曲线进行拟合,得到模型方程中的参数,如图8所示,具体的有:

(1)选择二极管模型方程:

其特征为,I

(2)在二极管正向区电压-电流特性曲线中选取三个参考点(V

当选取的参考点电压远大于热电压V

解上述方程组(3)可得寄生电阻R和发射系数n的值;

(3)在二极管正向区电压-电流特性曲线中选取一点(V

有了晶体管特性曲线后,提取MOS管参数时,选择合适的器件模型,利用非线性对消二乘优化技术对模型方程与特性曲线进行拟合,得到模型方程中的参数,如图9所示,具体的有:

(1)利用线性外推法原理提取MOS管的阈值电压。当漏电压V

(2)根据MOS管在线性区漏极电压V

从MOS管输出特性曲线线性区选取两点,代入关系式,计算得MOS管饱和电压

(3)获得饱和电压V

(4)根据式(4),令k

(5)根据MOS管在饱和区,饱和电压V

从MOS管特性曲线的饱和区任选两点(V

有了提取到的二极管模型参数和MOS管模型参数,建立CMOS数字IC行为-物理混合模型(如图10所示),具体的有:

(1)构建CMOS数字IC功能区模型,根据器件手册中的真值表,用VHDL语言描述器件的功能;

(2)构建CMOS数字IC输入端口模型,根据器件数据手册中元件的模型参数(封装电容C_comp、引脚寄生电阻R_pkg、引脚寄生电感L_pkg和引脚寄生电容C_pkg)和上述提取的二极管模型参数(电源/地钳位二极管反向饱和电流I

(3)构建CMOS数字IC输出端口模型,根据器件数据手册中元件的模型参数(封装电容C_comp、引脚寄生电阻R_pkg、引脚寄生电感L_pkg和引脚寄生电容C_pkg)和上述提取的二极管模型参数及MOS管模型参数(电源/地钳位二极管反向饱和电流I

(4)所述数字IC功能区模型、输入端口模型和输出端口模型共同构成CMOS数字IC行为-物理混合模型。

由于总剂量效应会引起数字组合逻辑及时序逻辑的时序退化。时序退化引起电路传播延迟发生变化,严重时会导致时序逻辑功能发生紊乱。为了对传播延迟进行建模,需对以行为-物理混合模型的功能区进行重构,引入引脚至引脚的信号传播延时。其中,辐照前的传播延时可通过查看器件数据手册得到,辐照后传播延时可根据辐照试验数据得到。由于本发明所建立的模型为CMOS数字集成电路总剂量效应模型,因此传播延时从辐照试验数据中得到。

由于CMOS数字集成电路输出端口开关管(NMOS与PMOS)易受总剂量辐射效应的影响而发生电特性退化,如阈值电压漂移、载流子迁移率下降等,且输出端口在受到总剂量辐照后,其电平转换时间变长,另外MOS器件迁移率的衰减对跨导及电流驱动能力影响很大,在分析MOS器件总剂量效应时必须将这种影响考虑在内。因此输出端口总剂量效应建模工作可在上述时序退化模型基础上通过对端口MOS管的阈值电压、载流子迁移率的总剂量效应建模两方面进行,如图11所示,具体的有:

(1)根据总剂量效应造成的阈值电压漂移ΔV

(2)根据总剂量效应引起的器件沟道载流子迁移率退化,根据辐射诱导界面态电荷ΔQ

至此,CMOS数字集成电路总剂量效应建模完毕。

下面结合具体实施例说明本发明的创造性。

为验证本发明建立的CMOS数字集成电路总剂量效应模型,选择NC7SZ157二路复用器搭建测试电路并在新疆理化技术研究所进行辐照试验。试验电路板与总剂量辐照试验如图12所示。本试验的试验条件如图13所示。

测试时,电源设置为直流3.3V,信号发生器设置为40KHz,幅值为3V,偏置1.5V,上升沿10ns,下降沿10ns。为防止器件发生退火导致结果不准确,务必在15分钟内完成所有辐照测试。

经过辐照试验和测试后,得到NC7SZ157总剂量辐照试验输出端口电平转换曲线,如图14和图15所示。由图14和图15可知,随着总剂量的增大,上升沿与下降沿转换速率均有所下降。不同总剂量下的高电平幅值依次为:3.2646V(0Krad)、3.2622V(50Krad)、3.2617V(150Krad),可以看出、随着总剂量的增大,高电平幅值有所下降,说明了总剂量辐照引起了上拉PMOS管导通电阻增大。接着将本发明所述步骤建立的数字器件行为-物理模型进行仿真结果与试验数据对比,如图16,图17和图18所示。总剂量分别为0K,50K,150K下的仿真相对误差分别为:0.2%(0Krad),0.6%(50krad),1.4%(150Krad)。由仿真与试验结果可以看出,该混合模型能较好地反映CMOS数字器件总剂量效应。

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,都应涵盖在本发明的保护范围之内。

- 一种CMOS数字集成电路总剂量效应建模方法及系统

- 考虑辐照偏置电压动态变化的CMOS电路总剂量效应仿真方法