一种垂直增强型MOSFET器件及其制备方法

文献发布时间:2023-06-19 18:29:06

技术领域

本发明涉及半导体器件技术领域,尤其涉及一种垂直增强型MOSFET器件及其制备方法。

背景技术

随着半导体技术的发展,超宽禁带半导体氧化镓(Ga

由于目前p型Ga

因此,现有技术还有待于改进和发展。

发明内容

鉴于上述现有技术的不足,本发明的目的在于提供一种垂直增强型MOSFET器件及其制备方法,旨在解决现有技术中制备得到的垂直型Ga

本发明的技术方案如下:

本发明的第一方面,提供一种垂直增强型MOSFET器件,其中,包括:

依次层叠设置的漏极、n型Ga

所述n型半导体层表面设置有向所述n型Ga

所述垂直增强型MOSFET器件还包括设置在所述凹槽中和所述n型半导体层上的绝缘栅介质层、设置在所述绝缘栅介质层上的栅极以及设置在所述n型半导体层上并与所述栅极间隔设置的源极。

可选地,所述漏极的材料选自钛、金、铝、镍、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种;所述源极的材料选自钛、金、铝、镍、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种;所述栅极的材料选自镍、金、钛、铝、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种。

可选地,所述p型半导体层中的p型半导体选自p型GaN、p型NiO、p型InO中的至少一种。

可选地,所述n型半导体层中的n型半导体选自n型GaN、n型Ga

可选地,所述绝缘栅介质层的材料选自Al

本发明的第二方面,提供一种本发明如上所述的垂直增强型MOSFET器件的制备方法,其中,包括步骤:

提供n型Ga

在所述Ga

在所述p型半导体层上形成n型半导体层,并在所述n型半导体层上形成向所述n型Ga

在所述凹槽中和所述n型半导体层上形成绝缘栅介质层;

在所述绝缘栅介质层上形成栅极;

在所述n型半导体层上形成与所述栅极间隔设置的源极;

在所述n型Ga

可选地,通过外延生长法在所述n型Ga

可选地,通过外延生长法在所述Ga

通过外延生长法在所述p型半导体层上形成n型半导体层。

可选地,通过刻蚀法在所述n型半导体层上形成向所述n型Ga

通过原子层沉积法在所述凹槽中和所述n型半导体层上形成绝缘栅介质层。

可选地,在所述绝缘栅介质层上沉积第一金属材料,形成栅极;

在所述n型半导体层上沉积第二金属材料,形成与所述栅极间隔设置的源极;

在所述n型Ga

有益效果:本发明在Ga

附图说明

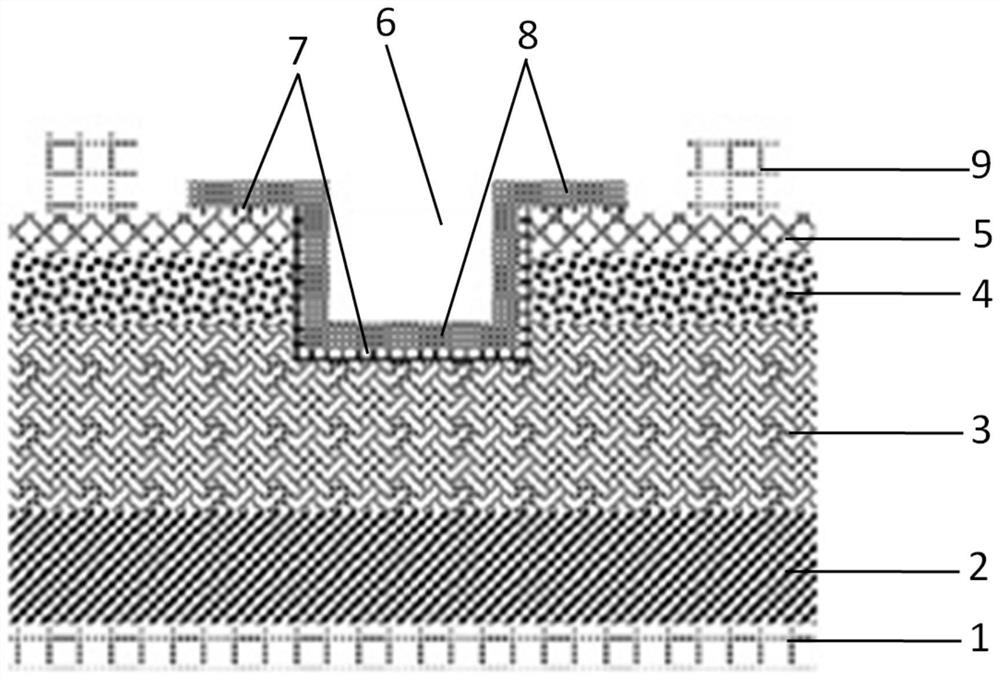

图1为本发明实施例中垂直增强型MOSFET器件的结构示意图。

图2为本发明实施例中垂直增强型MOSFET器件的制备流程示意图,其中(a)为在n型Ga

图3为现有技术中鳍型栅垂直型Ga

图4为现有技术中平面栅垂直型Ga

具体实施方式

本发明提供一种垂直增强型MOSFET器件及其制备方法,为使本发明的目的、技术方案及效果更加清楚、明确,以下对本发明进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

除非另有定义,本文所使用的所有的技术术语和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施方式的目的,不是旨在于限制本发明。

本发明实施例提供一种垂直增强型MOSFET器件,如图1所示,其中,包括:

依次层叠设置的漏极1、n型Ga

所述n型半导体层5表面设置有向所述n型Ga

所述垂直增强型MOSFET器件还包括设置在所述凹槽6中和所述n型半导体层5上的绝缘栅介质层7、设置在所述绝缘栅介质层7上的栅极8以及设置在所述n型半导体层5上并与所述栅极8间隔设置的源极9。

本发明实施例通过在Ga

具体地,p型半导体层与n型半导体层形成pn结,当栅极不施加电压时,由于源极下方存在因pn结而产生的耗尽区,源漏极间电流通道处于阻断状态,即使在漏极施加电压,也无法在源漏极间产生电流,器件仍处于截止状态;而在栅极施加足够大的电压后,沿凹槽两侧的pn结耗尽区宽度减小,从而出现由源极沿凹型槽两侧到漏极的电流沟道,此时在源漏极施加电压,即可产生电流,故本实施例提供的器件为垂直增强型MOSFET器件。

本实施例中,如图1所示,绝缘栅介质层7可以理解为包括两部分,一分部设置在凹槽底部和侧壁,一部分设置在n型半导体层5上,设置在n型半导体层5上的那一部分不完全覆盖n型半导体层,以实现源极9可以设置在n型半导体层5上且可以与栅极8间隔设置。

在一些实施方式中,所述漏极的厚度为50~200nm。例如,所述漏极的厚度可为50nm、80nm、100nm、120nm、150nm、180nm或200nm等。

在一些实施方式中,所述漏极的材料选自钛、金、铝、镍、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种,但不限于此。作为举例,当所述漏极的材料选自钛和金,所述漏极由层叠的钛层和金层构成(可记作Ti/Au),其中,钛层的厚度可为50nm,金层的厚度可为150nm,钛层贴合n型Ga

在一些实施方式中,所述n型Ga

在一些实施方式中,所述n型Ga

在进一步的一些实施方式中,所述n型β-Ga

在一些实施方式中,所述Ga

在一些实施方式中,所述Ga

在一些实施方式中,所述p型半导体层的厚度为100~1000nm。例如,所述p型半导体层的厚度可为100nm、200nm、300nm、400nm、500nm、600nm、700nm、800nm、900nm或1000nm等。

在一些实施方式中,所述p型半导体层中的p型半导体选自p型GaN、p型NiO、p型InO中的至少一种。进一步地,所述p型半导体为Mg或Zn的掺杂p型半导体,掺杂后所述p型半导体层中空穴浓度为5×10

在一些实施方式中,所述n型半导体层的厚度为100~700nm。例如,所述n型半导体层的厚度可为100nm、200nm、300nm、400nm、500nm、600nm或700nm等。

在一些实施方式中,所述n型半导体层中的n型半导体选自n型GaN、n型Ga

在一些实施方式中,所述绝缘栅介质层的厚度为10~70nm。例如,所述绝缘栅介质层的厚度可为10nm、20nm、30nm、40nm、50nm、60nm或70nm等。

在一些实施方式中,所述绝缘栅介质层的材料选自Al

在一些实施方式中,所述栅极的厚度为50~200nm。例如,所述栅极的厚度可为50nm、80nm、100nm、120nm、150nm、180nm或200nm等。

在一些实施方式中,所述栅极的材料选自镍、金、钛、铝、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种,但不限于此。作为举例,当所述栅极的材料选自镍和金时,所述栅极由层叠的镍层和金层构成(可记作Ni/Au),其中镍层的厚度可为50nm,金层的厚度可为150nm,镍层贴合所述绝缘栅介质层。

在一些实施方式中,所述源极的厚度为50~200nm。例如,所述源极的厚度为50nm、80nm、100nm、120nm、150nm、180nm或200nm等。

在一些实施方式中,所述源极的材料选自钛、金、铝、镍、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种,但不限于此。作为举例,当所述源极的材料选自钛和金时,所述源极由层叠的钛层和金层构成(可记作Ti/Au),其中源层的厚度可为50nm,金层的厚度可为150nm,钛层贴合n型半导体层。

MOSFET可制作成鳍型栅结构(如图3所示)或平面栅结构(如图4所示),而现有技术中鳍型栅结构会导致沟槽角部栅氧化物场应力加剧影响器件的可靠性,降低器件的耐压能力。另外,鳍型结构是通过ICP刻蚀得到的,干法刻蚀会给沟槽侧壁带来损伤,无法得到高质量的MOS界面。鳍型栅工艺复杂,损伤很大,而且无法制备增强型的MOSFET器件。平面栅工艺简单,避免了干法刻蚀带来的损伤,可以得到高质量的金属氧化物半导体(MOS)界面。但是需要高剂量和高能量的Mg或者N离子才能实现高阻层,且会损伤晶格。另外,此种方法也无法实现增强型MOSFET器件。基于此,本发明实施例还提供一种本发明实施例如上所述的垂直增强型MOSFET器件的制备方法,图2所示,其中,包括步骤:

S1、如图2中(a)所示,提供n型Ga

S2、如图2中(b)所示,在所述Ga

S3、如图2中(d)-(e)所示,在所述p型半导体层4上形成n型半导体层5,并在所述n型半导体层5上形成向所述n型Ga

S4、如图2中(f)所示,在所述凹槽6中和所述n型半导体层5上形成绝缘栅介质层7;

S5、如图2中(g)所示,在所述绝缘栅介质层7上形成栅极8;

S6、如图2中(h)所示,在所述n型半导体层5上形成与所述栅极8间隔设置的源极9;

S7、如图2中(i)所示,在所述n型Ga

本实施例提供的制备方法简单,不需要进行离子注入,工艺成本低,可以避免现有技术中鳍型栅结构的制备所存在的问题(如鳍型栅结构会导致沟槽角部栅氧化物场应力加剧影响器件的可靠性,降低器件的耐压能力),同时也可避免现有技术中平面栅结构的制备所存在的问题(如需要高剂量和高能量的Mg或者N离子才能实现高阻层,且会损伤晶格)。

本实施方式中,漏极可在提供n型Ga

步骤S1中,在一些实施方式中,通过外延生长法在所述n型Ga

在一些实施方式中,所述外延生长法包括但不限于金属有机化合物化学气相沉积(MOCVD)、分子束外延(MBE)、氢化物气相外延(HVPE)中的一种。

步骤S1中,在所述n型Ga

步骤S2中,如图2中(c)所示,在一些实施方式中,通过外延生长法在所述Ga

在一些实施方式中,所述外延生长法包括但不限于金属有机化合物化学气相沉积(MOCVD)、分子束外延(MBE)、氢化物气相外延(HVPE)中的一种。

在一些实施方式中,所述p型半导体层中的p型半导体选自p型GaN、p型NiO、p型InO中的至少一种。当通过MOCVD法在所述Ga

在一些实施方式中,所述退火的温度为700~1000℃,所述退火的时间为5~30min。

步骤S3中,在一些实施方式中,通过外延生长法在所述p型半导体层上形成n型半导体层。

在一些实施方式中,所述外延生长法包括但不限于金属有机化合物化学气相沉积(MOCVD)、分子束外延(MBE)、氢化物气相外延(HVPE)中的一种。

在一些实施方式中,所述n型半导体层中的n型半导体为n型GaN、n型Ga

在一些实施方式中,通过刻蚀法在所述n型半导体层上形成向所述n型Ga

在一些具体的实施方式中,当n型半导体层中的n型半导体选自n型GaN、n型Ga

4Ga(s)+Ga

通过控制Ga流量的大小与腐蚀时间,改善刻蚀后表面粗糙的形貌,修复刻蚀损伤。

步骤S4中,在一些实施方式中,通过包括但不限于原子层沉积(ALD)法在所述凹槽中和所述n型半导体层上形成绝缘栅介质层。

在一些实施方式中,所述绝缘栅介质层可为Al

在一些具体的实施方式中,所述绝缘栅介质层为Al

步骤S5中,在一些实施方式中,在所述绝缘栅介质层上沉积第一金属材料,形成栅极。

具体地,可采用包括但不限于电子束蒸发法或溅射方法在所述绝缘栅介质层上沉积第一金属材料,形成栅极。栅极的厚度参见上文。

在一些实施方式中,所述第一金属材料可选自镍、金、钛、铝、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种,但不限于此。

在一些具体的实施方式中,采用电子束蒸发法在所述绝缘栅介质层上沉积Ni/Au(50/150nm),Ni层贴合所述绝缘栅介质层设置,并利用揭开-剥离(Lift-Off)工艺进行金属剥离,形成栅极。

步骤S6中,在一些实施方式中,在所述n型半导体层上沉积第二金属材料,形成与所述栅极间隔设置的源极。源极的厚度参见上文。

具体地,可采用包括但不限于电子束蒸发法或溅射方法在所述n型半导体层上沉积第二金属材料,形成与所述栅极间隔设置的源极。其中,所述第二金属材料选自钛、金、铝、镍、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种,但不限于此。

在一些具体的实施方式中,采用电子束蒸发法在所述n型半导体层上沉积Ti/Au金属(50/150nm),Ti层贴合n型半导体层,并利用揭开-剥离(Lift-Off)工艺进行金属剥离,形成源极。

步骤S7中,在一些实施方式中,在所述n型Ga

在一些实施方式中,所述第三金属材料选自钛、金、铝、镍、铂、铱、钼、钽、铌、钴、锆、钨中的一种或多种,但不限于此。

在一些具体的实施方式中,采用电子束蒸发法在所述n型Ga

在一些实施方式中,所述垂直增强型MOSFET器件的制备方法还包括步骤:

S8、对制备得到的器件进行快速退火。目的是实现欧姆接触。

具体地,可将制备的器件放置在快速热处理(RTP)炉中进行快速退火。

下面通过具体的实施例进行详细说明。

实施例1

如图2所示,垂直增强型MOSFET器件的制备方法包括步骤:

(1)如图2中(a)所示,取氧化镓同质外延片,然后依次用丙酮、异丙醇各超声清洗5min,再用大量去离子水冲洗,之后用氮气吹干,吹干后的氧化镓同质外延片即为含有n型β-Ga

(2)如图2中(b)所示,分别以三甲基镓(TMGa)、氨气(NH

(3)如图2中(c)所示,然后在N

(4)如图2中(d)所示,分别以TMGa、NH

(5)如图2中(e)所示,在n

(6)如图2中(f)所示,分别以三甲基铝(TMA)和水蒸汽(H

(7)如图2中(g)所示,在绝缘栅介质层上进行光刻形成栅极区域,通过电子束蒸发(E-Beam)系统在栅极区域先后淀积Ni和Au,得到厚度为20nm/30nm的Ni/Au层,然后放入剥离液中进行剥离后,形成栅极。

(8)如图2中(h)-(i)所示,进行光刻形成源极及漏极区域,通过E-Beam系统分别在源极区域、漏极区域先后沉积Ti和Au,在源极区域、漏极区域分别得到厚度为20nm/30nm的Ti/Au层,然后放入剥离液中进行剥离后,形成源极和漏极。

(9)将上述制备的器件放置在快速热处理炉内,在N

实施例2

如图2所示,垂直增强型MOSFET器件的制备方法包括步骤:

(1)如图2中(a)所示,取氧化镓同质外延片,然后依次用丙酮、异丙醇各超声清洗10min,再用大量去离子水冲洗,之后用氮气吹干,吹干后的氧化镓同质外延片即为含有n型β-Ga

(2)如图2中(b)所示,分别以TMGa、NH

(3)如图2中(c)所示,然后在N

(4)如图2中(d)所示,分别以TMGa、NH

(5)如图2中(e)所示,在n

(6)如图2中(f)所示,分别以TMA和水蒸汽(H

(7)如图2中(g)所示,在绝缘栅介质层上进行光刻形成栅极区域,通过E-Beam系统在栅极区域先后淀积Ni和Au,得到厚度为50nm/150nm的Ni/Au层,然后放入剥离液中进行剥离后,形成栅极。

(8)如图2中(h)-(i)所示,进行光刻形成源极及漏极区域,通过E-Beam系统分别在源极区域、漏极区域先后沉积Ti和Au,在源极区域、漏极区域分别得到厚度为50nm/150nm的Ti/Au层,然后放入剥离液中进行剥离后,形成源极和漏极。

(9)将上述制备的器件放置在快速热处理炉内,在N

实施例3

如图2所示,垂直增强型MOSFET器件的制备方法包括步骤:

(1)如图2中(a)所示,取氧化镓同质外延片,然后依次用丙酮、异丙醇各超声清洗10min,再用大量去离子水冲洗,之后用氮气吹干,吹干后的氧化镓同质外延片即为含有n型β-Ga

(2)如图2中(b)所示,分别以TMGa、NH

(3)如图2中(c)所示,然后在N

(4)如图2中(d)所示,分别以TMGa、氧气(O

(5)如图2中(e)所示,在n

(6)如图2中(f)所示,分别以TMA和水蒸汽(H

(7)如图2中(g)所示,在绝缘栅介质层上进行光刻形成栅极区域,通过E-Beam系统在栅极区域先后淀积Ni和Au,得到厚度为30nm/90nm的Ni/Au层,然后放入剥离液中进行剥离后,形成栅极。

(8)如图2中(h)-(i)所示进行光刻形成源极及漏极区域,通过E-Beam系统分别在源极区域、漏极区域先后沉积Ti和Au,在源极区域、漏极区域分别得到厚度为30nm/90nm的Ti/Au层,然后放入剥离液中进行剥离后,形成源极和漏极。

(9)将上述制备的器件放置在快速热处理炉内,在N

应当理解的是,本发明的应用不限于上述的举例,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,所有这些改进和变换都应属于本发明所附权利要求的保护范围。

- 一种碳化硅MOSFET器件及其制备方法

- 一种横向沟槽型MOSFET器件及其制备方法

- 碳化硅MOSFET器件及其制备方法

- 一种环形热电器件的制备装置及其制备环形热电器件的方法

- 槽栅结构的AlGaN/GaN增强型MOSFET器件及制备方法

- 带有MOSFET和低正向电压的等效二极管增强型JFET的半导体器件及其制备方法