一种快速比较器

文献发布时间:2023-06-19 19:23:34

技术领域

本发明属于电子电路技术领域,特别涉及一种快速比较器。

背景技术

通常来说,比较器包含依次连接的差分输入级、中间负载级和数字逻辑输出级三部分,使用差分输入结构能够提高比较器的数据传输速率,降低噪声,然而在比较器工作过程中,当出现差分电压时,中间负载级中的NMOS进入深线性区,此时数字逻辑输出级的输出为低电平,而当中间负载级中的PMOS进入深线性区,此时数字逻辑输出级的输出为高电平。当高低电平进行转换时,由于相关MOS管在深线性区和饱和区之间进行相互转换,需要花费较长的转换时间,从而导致比较器传输延时较长。

以图1为例,是一种通用推挽输出比较器结构图,其中,差分输入级包括由两个NMOS管NM1、NM2构成的输入对管以及电流源(尾电流)IB,中间负载级包括两组负载管,其中一组由PMOS管PM3、PM4、PM5、PM6构成,另一组负载管由NMOS管NM3、NM4、NM5、NM6构成,中间负载级整体构成一个折叠共源共栅放大器,可对差分输入级的信号进行较大倍数的放大;该电路结构还包括有一个共源放大级,由NMOS管NM9和PMOS管PM8对输入的小差模信号进一步放大;所述共源放大级的输出连接至数字缓冲器,由PMOS管PM9、PM10和NMOS管NM10、NM11输出比较结果;具体的电路连接关系详见图1,不再赘述。

工作时,如图1,输入对管电流I1+I2等于尾电流IB,当VIP大于VIN时,I2增大,I1减小,即I2>I1;同时I3=I5-I1,I4=I6-I2。由于PM5/PM6尺寸相同且栅源电压相同,NM3/NM4尺寸相同且栅源电压相同,所以,若PM5/PM6处于饱和区,则I5=I6,I3=I4。那么由于I1不等于I2,则说明PM5/PM6,NM3/NM4有器件进入线性区。通过设置合理的偏置电压V1/V2/V5,可保证PM3/PM5/NM5/NM3工作在饱和区。通常I6小于等于I5,I4小于等于I3,现在I2大于I1,那么必定有I4小于I3,那么可推断出NM4进入线性区,即A点为一个相对比较低的电压。此时NM9处于关断或弱开启的状态,NM9漏极输出电压为高电位,经过数字缓冲器之后VOUT输出逻辑高电平。

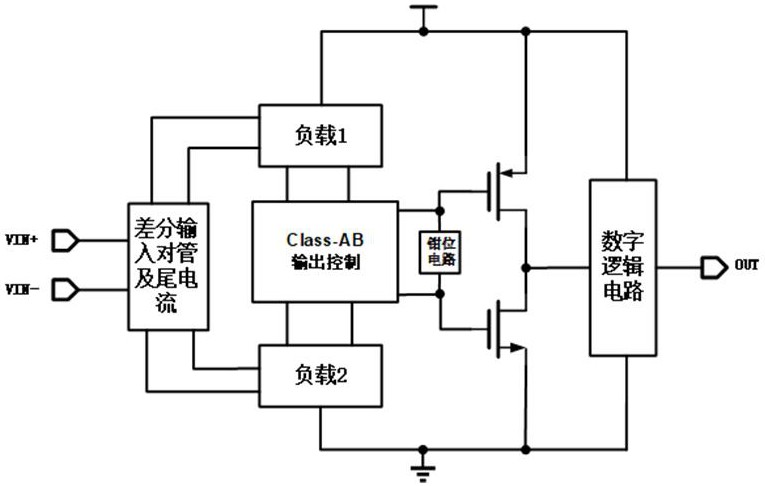

同理,输入对管电流I1+I2等于尾电流IB,当VIP小于VIN时,I2减小,I1增大,即I2 从以上的工作原理中可以看出,当输入差模电压足够大时,能够使输出进行相应的逻辑反转,那么折叠共源共栅放大器的负载管在比较器工作过程中会在线性区和饱和区之间进行切换,即节点A在进行大幅度的变化,可参照图2,这一切换通常需要花费较长时间,所以导致比较器传输延时较长。 发明内容 本发明的目的,在于提供一种快速比较器,能够缩短比较器的传输延时,提升比较器性能。 为了达成上述目的,本发明的解决方案是: 一种快速比较器,包括差分输入对管及尾电流、负载电路、共源放大电路和数字逻辑电路,其中,差分输入对管及尾电流、负载电路顺序连接,共源放大电路、数字逻辑电路顺序连接,差分输入对管及尾电流包括相连接的差分输入对管和电流源;还包括Class-AB输出控制电路和钳位电路,其中,Class-AB输出控制电路的输入端连接负载电路,Class-AB输出控制电路的输出端与钳位电路的一端相连接,钳位电路的另一端连接共源放大电路的输入端。 上述差分输入对管采用由NMOS管构成的NMOS输入对管、由PMOS管构成的PMOS输入对管,或者采用由NMOS管和PMOS管构成的输入对管。 上述负载电路包括第一负载和第二负载,其中,第一负载连接至电源端,第二负载连接至接地端。 上述第一负载采用PMOS管、PNP三极管、电阻或前述三者中任意两种或三种的组合,第二负载采用NMOS管、NPN三极管、电阻或前述三者中任意两种或三种的组合。 上述差分输入对管包括第一NMOS管和第二NMOS管,第一NMOS管的漏极与第二NMOS管的漏极分别连接至第一负载,第一NMOS管的源极与第二NMOS管的源极共同接地,第一NMOS管的栅极作为快速比较器的负输入端,第二NMOS管的栅极作为快速比较器的正输入端。 上述Class-AB输出控制电路包括第一PMOS管、第七NMOS管和第二PMOS管,其中,第一PMOS管的栅极连接第二PMOS管的栅极,第一PMOS管的源极和漏极分别作为Class-AB输出控制电路的输入端,第七NMOS管的漏极连接第二PMOS管的源极,第七NMOS管的源极连接第二PMOS管的漏极,第七NMOS管的栅极连接偏置电压;钳位电路包括第七PMOS管和第八NMOS管,第七PMOS管的漏极连接第八NMOS管的漏极,并共同连接至共源放大电路;第七PMOS管的源极和栅极并接,并共同连接第七NMOS管的漏极、第二PMOS管的源极;第八NMOS管的源极和栅极并接,并共同连接第七NMOS管的源极、第二PMOS管的漏极。 上述共源放大电路包括第八PMOS管和第九NMOS管,其中,第八PMOS管的源极连接电源,第九NMOS管的源极接地,第八PMOS管的漏极与第九NMOS管的漏极连接,并共同连接至第七PMOS管的漏极、第八NMOS管的漏极;第八PMOS管的栅极连接至第七NMOS管的漏极、第二PMOS管的源极、第七PMOS管的源极、第七PMOS管的栅极,第九NMOS管的栅极连接至第七NMOS管的源极、第二PMOS管的漏极、第八NMOS管的源极、第八NMOS管的栅极并接。 上述负载电路包括第三PMOS管、第四PMOS管、第五PMOS管、第六PMOS管、第三NMOS管、第四NMOS管、第五NMOS管和第六NMOS管; 第五PMOS管的栅极与第六PMOS管的栅极相连,第五PMOS管的源极与第六PMOS管的源极均连接至电源,第五PMOS管的漏极连接第三PMOS管的源极,并连接至差分输入对管及尾电流的第一输出端;第六PMOS管的漏极连接第四PMOS管的源极,并连接至差分输入对管及尾电流的第二输出端;第三PMOS管的栅极与第四PMOS管的栅极相连,第三PMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的源极,第四PMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的漏极、第二PMOS管的源极; 第五NMOS管的栅极与第六NMOS管的栅极相连,第五NMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的漏极,第六NMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极;第五NMOS管的源极连接第三NMOS管的漏极,第六NMOS管的源极连接第四NMOS管的漏极;第三NMOS管的源极与第四NMOS管的源极均接地,第三NMOS管的栅极与第四NMOS管的栅极连接,并连接至Class-AB输出控制电路中第一PMOS管的漏极。 上述负载电路包括第五PNP三极管、第六PNP三极管、第三PMOS管、第四PMOS管、第五NMOS管、第六NMOS管、第三NPN三极管和第四NPN三极管; 第五PNP三极管的基极与第六PNP三极管的基极相连,第五PNP三极管的发射极与第六PNP三极管的发射极均连接至电源,第五PNP三极管的集电极连接第三PMOS管的源极,并连接至差分输入对管及尾电流的第一输出端;第六PNP三极管的集电极连接第四PMOS管的源极,并连接至差分输入对管及尾电流的第二输出端;第三PMOS管的栅极与第四PMOS管的栅极相连,第三PMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的漏极,第四PMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极; 第五NMOS管的栅极与第六NMOS管的栅极相连,第五NMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的漏极,第六NMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极;第五NMOS管的源极连接第三NPN三极管的集电极,第六NMOS管的源极连接第四NPN三极管的集电极;第三NPN三极管的发射极与第四NPN三极管的发射极均接地,第三NPN三极管的基极与第四NPN三极管的基极连接,并连接至Class-AB输出控制电路中第一PMOS管的漏极。 上述负载电路包括第一电阻、第二电阻、第三PMOS管、第四PMOS管、第三NMOS管、第四NMOS管、第五NMOS管和第六NMOS管; 第一电阻的一端连接电源,第一电阻的另一端连接第三PMOS管的源极,并连接至差分输入对管及尾电流的第一输出端;第二电阻的一端连接电源,第二电阻的另一端连接第四PMOS管的源极,并连接至差分输入对管及尾电流的第二输出端;第三PMOS管的栅极连接至Class-AB输出控制电路中第一PMOS管的漏极,第四PMOS管的栅极相连,第三PMOS管的漏极与第四PMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极; 第五NMOS管的栅极与第六NMOS管的栅极相连,第五NMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的漏极,第六NMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极;第五NMOS管的源极连接第三NMOS管的漏极,第六NMOS管的源极连接第四NMOS管的漏极;第三NMOS管的源极与第四NMOS管的源极均接地,第三NMOS管的栅极与第四NMOS管的栅极连接,并连接至Class-AB输出控制电路中第一PMOS管的漏极。 上述负载电路包括第三PMOS管、第四PMOS管、第五PMOS管、第六PMOS管、第一电阻、第二电阻、第三电阻、第四电阻、第三NMOS管、第四NMOS管、第五NMOS管和第六NMOS管; 第一电阻的一端连接电源,第一电阻的另一端连接第五PMOS管的源极;第二电阻的一端连接电源,第二电阻的另一端连接第六PMOS管的源极;第五PMOS管的栅极与第六PMOS管的栅极相连,第五PMOS管的漏极连接第三PMOS管的源极,并连接至差分输入对管及尾电流的第一输入端;第六PMOS管的漏极连接第四PMOS管的源极,并连接至差分输入对管及尾电流的第二输入端;第三PMOS管的栅极与第四PMOS管的栅极相连,第三PMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的漏极,第四PMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极; 第五NMOS管的栅极与第六NMOS管的栅极相连,第五NMOS管的漏极连接至Class-AB输出控制电路中第一PMOS管的漏极,第六NMOS管的漏极分别连接至Class-AB输出控制电路中第七NMOS管的源极、第二PMOS管的漏极;第五NMOS管的源极连接第三NMOS管的漏极,第六NMOS管的源极连接第四NMOS管的漏极;第三NMOS管的栅极与第四NMOS管的栅极连接,并连接至Class-AB输出控制电路中第一PMOS管的漏极;第三NMOS管的源极连接第三电阻的一端,第三电阻的另一端接地;第四NMOS管的源极连接第四电阻的一端,第四电阻的另一端接地。 采用上述方案后,本发明通过增加Class-AB输出控制电路和钳位电路,能够避免电路中的相关MOS管进入深线性区,保证关键节点不发生较大的电压波动,实现比较器传输延时较小的特性,提升比较器性能。 附图说明 图1是现有通用推挽输出比较器结构图; 图2是图1所示通用推挽输出比较器的工作特性图; 图3是本发明快速比较器的整体结构图; 图4是本发明第一实施例的电路结构图; 图5是图4所示电路的工作特性图; 图6是本发明第二实施例的电路结构图; 图7是本发明第三实施例的电路结构图; 图8是本发明第四实施例的电路结构图。 具体实施方式 以下将结合附图,对本发明的技术方案及有益效果进行详细说明。 本发明提供一种快速比较器,包括依次连接的差分输入对管、负载电路,以及依次连接的共源放大电路、数字逻辑电路,可配合图3所示,还包括Class-AB输出控制电路和钳位电路,其中,Class-AB输出控制电路的输入端连接负载电路,Class-AB输出控制电路的输出端与钳位电路的一端相连接,钳位电路的另一端连接共源放大电路的输入端。 作为本发明的一个较佳实施例,所述差分输入对管可以采用仅包含NMOS管的NMOS输入对管、仅包含PMOS管的PMOS输入对管,也可以采用NMOS管和PMOS管共同连接组成的输入对管。 作为本发明的一个较佳实施例,所述负载电路包含第一负载和第二负载,其中,第一负载连接至电源端,第二负载连接至接地端;所述第一负载可以采用PMOS管、PNP三极管、电阻或前述三者中任意两种或三种的组合,第二负载可以采用NMOS管、NPN三极管、电阻或前述三者中任意两种或三种的组合。 如图4所示,是本发明提供的一种快速比较器的第一个较佳实施电路结构,其中,差分输入对管采用由两个NMOS管NM1、NM2构成的输入对管,第一负载采用全PMOS管的组合,第二负载采用全NMOS管的组合;共源放大电路包含NMOS管NM9和PMOS管PM8,该共源放大电路还同时作为Class-AB输出控制电路的输出管;数字逻辑电路采用数字缓冲器的结构,前述连接结构与现有结构类似,不再赘述。 本发明提供的较佳实施电路结构中,Class-AB输出控制电路连接在第一负载和第二负载之间,具体包含PMOS管PM1、NMOS管NM7和PMOS管PM2,其中,PM1的栅极连接PM2的栅极,NM7的漏极连接PM2的源极,NM7的源极则连接PM2的漏极;钳位电路包括PMOS管PM7和NMOS管NM8,PM7的漏极连接NM8的漏极并定义为Q点,该Q点还连接至共源放大电路;PM7的源极和栅极并接并定义为P点,该P点还连接NM7的漏极、PM2的源极;NM8的源极和栅极并接并定义为N点,该N点还连接NM7的源极、PM2的漏极;利用Class-AB输出控制电路将Class-AB输出管PM8、NM9的控制电位进行分离,并利用钳位晶体管PM7/NM8限制P和N点的摆幅,使得折叠共源共栅放大器负载管不在线性区和饱和区之间来回切换,从而降低传播延时。 工作时,当VIP大于VIN时,NM4进入线性区,P点、N点处于一个较低电位,Q点为高电平,实际上,当Q点处于高电平时,PM7导通,钳位P点电位低于Q点一个阈值电压,此时存在由Q点流经PM7、NM7、NM6至NM4的电流通路,通过合理设计NM7的尺寸可保证NM4不进入线性区。 同样的道理,当VIP小于VIN时,PM6会进入线性区,P点、N点处于一个较高电位,Q点为低电平,实际上,当Q点处于低电平时,NM8导通,钳位N点电位高于Q点一个阈值电压,此时存在由电源流经PM6、PM4、PM2至NM8的电流通路,通过合理设计PM2的尺寸可保证PM6不进入线性区。 P点、N点的工作特性可参考图5所示。 如图6所示,是本发明第二实施例的电路结构图,其与第一实施例的区别在于负载电路的结构,在本实施例中,第一负载采用PMOS管与PNP三极管的组合结构,具体包括PNP三极管PM5、PM6和PMOS管PM3、PM4,其中,PM5、PM6共基极连接,PM5的发射极和PM6的发射极均连接至电源VDD,PM5的集电极连接PM3的源极,PM6的集电极连接PM4的源极;PM3、PM4共栅极连接,PM3的漏极连接至Class-AB输出控制电路中PM1的源极,PM4的漏极连接至P点;所述第二负载采用NMOS管与NPN三极管的组合结构,具体包括NMOS管NM5、NM6和NPN三极管NM3、NM4,其中,NM5、NM6共栅极连接,NM5的漏极连接至Class-AB输出控制电路中PM1的漏极,NM5的源极连接NM3的集电极,NM6的漏极连接至N点,NM6的源极连接NM4的集电极;NM3、NM4共基极连接,NM3的发射极和NM4的发射极均接地GND。 如图7所示,是本发明的第三实施例的电路结构图,其与第一实施例的区别在于负载电路的结构,在本实施例中,第一负载采用PMOS管与电阻的组合结构,具体包括电阻R1、R2和PMOS管PM3、PM4,其中,R1、R2的一端均连接电源VDD,R1的另一端连接PM3的源极,R2的另一端连接PM4的源极;PM3、PM4共栅极连接,PM3的漏极连接至Class-AB输出控制电路中PM1的源极,PM4的漏极连接至P点;所述第二负载与第一实施例的结构相同,采用全NMOS管的组合,在此不再赘述。 如图8所示,是本发明的第四实施例的电路结构图,其与第一实施例的区别在于负载电路的结构,在本实施例中,第一负载采用PMOS管与电阻的组合结构,具体包括PMOS管PM3、PM4、PM5、PM6和电阻R1、R2,其中,R1、R2的一端均连接电源VDD,R1的另一端连接PM5的源极,R2的另一端连接PM6的源极;PM5、PM6共栅极连接,PM5的漏极连接PM3的源极,PM6的漏极连接PM4的源极;PM3、PM4共栅极连接,PM3的漏极连接至Class-AB输出控制电路中PM1的源极,PM4的漏极连接至P点;所述第二负载采用NMOS管与电阻的组合结构,具体包括NMOS管NM3、NM4、NM5、NM6和电阻R3、R4,其中,NM5、NM6共栅极连接,NM5的漏极连接至Class-AB输出控制电路中PM1的漏极,NM5的源极连接NM3的漏极,NM6的漏极连接至N点,NM6的源极连接NM4的漏极;NM3、NM4共栅极连接,NM3的源极连接R3的一端,NM4的源极连接R4的一端,R3的另一端、R4的另一端均接地GND。 以上实施例仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明保护范围之内。

- 一种快速恢复电路及连接于该快速恢复电路的误差放大器和比较器

- 一种快速响应动态锁存比较器