半导体器件及其制备方法

文献发布时间:2023-06-19 19:37:02

技术领域

本公开涉及半导体领域,尤其涉及一种半导体器件及其制备方法。

背景技术

随着集成电路制造技术的发展,集成电路的工艺节点不断减小,半导体技术特征尺寸不断减小,传统的平面式晶体管已经无法满足需求,鳍式晶体管因运而生,并得到广泛应用。

目前DRAM在阵列区一般是鳍式晶体管,字线(world line,简称WL)埋入硅衬底的内部,可以减少单位晶体管的面积,位线(bit line,简称BL)与节点连接结构(nodecontact,简称NC)位于硅衬底的表面,并且位于同一平面上。然而,随着尺寸的微缩,位线的尺寸与节点连接结构的尺寸一直在互相取舍。并且现有技术中晶体管是一条字线控制一个晶体管的开关,需要提供足够高的电压。

因此,如何改进晶体管布线结构并优化晶体管开关电路成为当下需要解决的问题。

公开内容

本公开所要解决的技术问题是如何改进晶体管布线结构并优化晶体管开关电路,提供一种半导体器件及其制备方法。

为了解决上述问题,本公开提供了一种半导体器件,包括:衬底;位线结构,设置于所述衬底表面,沿第一方向延伸,多条所述位线结构沿第二方向排布,所述第一方向垂直于所述第二方向;半导体柱,设置于所述位线结构表面且阵列排布;字线结构,设置于所述位线结构表面,且与所述位线结构绝缘,所述字线结构位于所述半导体柱之间,且沿所述第二方向延伸,多条所述字线结构与所述半导体柱沿所述第一方向间隔排布,在所述第一方向上相邻的两个所述半导体柱共用同一所述字线结构,且每一所述半导体柱由在所述第一方向上位于其两侧的两条所述字线结构共同控制。

在一些实施例中,在所述第一方向上位于所述半导体柱两侧的两条所述字线结构用于加载电性相反的电压。

在一些实施例中,所述位线结构进一步包括:位线,设置于所述衬底表面,沿所述第一方向延伸,多条所述位线沿第二方向排布;位线连接结构,设置于所述位线表面,沿所述第一方向延伸,多条所述位线连接结构沿所述第二方向排布。

在一些实施例中,所述半导体器件还包括第一绝缘层,所述第一绝缘层设置于多条所述位线结构之间。

在一些实施例中,所述字线结构进一步包括:字线,设置于所述位线结构表面,且与所述位线结构绝缘,所述字线沿第二方向延伸,且多条所述字线沿所述第一方向间隔排布;栅极介质层,设置于所述字线与所述半导体柱之间。

在一些实施例中,所述半导体器件还包括:第二绝缘层,设置于所述字线结构与所述位线结构之间,以及在第二方向上相邻的所述半导体柱之间;第三绝缘层,设置于所述字线结构表面,且至少位于所述半导体柱之间。

在一些实施例中,所述半导体器件还包括节点连接结构,所述节点连接结构设置于所述半导体柱背离所述位线结构的一端且阵列排布。

在一些实施例中,所述半导体器件还包括:第四绝缘层,设置于所述第三绝缘层表面,至少位于所述节点连接结构之间。

在一些实施例中,所述半导体器件还包括电荷存储结构,所述电荷存储结构阵列排布于所述节点连接结构表面。

为了解决上述问题,本公开提供了一种半导体器件的制备方法,包括如下步骤:提供一衬底;在所述衬底表面形成位线结构,所述位线结构沿第一方向延伸,多条所述位线结构沿第二方向排布,所述第一方向垂直于所述第二方向;在所述位线结构表面形成阵列排布的半导体柱;在所述位线结构表面形成字线结构,所述字线结构与所述位线结构绝缘,且位于所述半导体柱之间,沿所述第二方向延伸,多条所述字线结构与所述半导体柱沿所述第一方向间隔排布,在所述第一方向上相邻的两个所述半导体柱共用同一所述字线结构,且每一所述半导体柱由在所述第一方向上位于其两侧的两条所述字线结构共同控制。

在一些实施例中,在所述衬底表面形成位线结构的步骤进一步包括:在所述衬底表面形成第一导电层;刻蚀所述第一导电层形成第一沟槽,所述第一沟槽沿所述第一方向延伸;在所述第一沟槽内形成第一绝缘层,保留的所述第一导电层作为所述位线结构。

在一些实施例中,在所述位线结构表面形成阵列排布的半导体柱的步骤进一步包括:在所述位线结构表面形成半导体层;刻蚀所述半导体层形成第二沟槽,所述第二沟槽沿第一方向延伸;在所述第二沟槽内形成第一隔离层;刻蚀所述半导体层和所述第一隔离层形成第三沟槽,所述第三沟槽沿第二方向延伸,刻蚀后的所述半导体层作为所述半导体柱。

在一些实施例中,在所述位线结构表面形成字线结构的步骤进一步包括:在所述第三沟槽内形成第二隔离层;形成栅极介质层,所述栅极介质层覆盖所述半导体柱沿所述第一方向的两侧;在所述第二隔离层表面及所述栅介质层侧面沉积导电材料,作为字线,所述栅极介质层以及所述字线共同构成所述字线结构;在所述栅极介质层以及所述字线表面形成第三绝缘层。

在一些实施例中,在所述位线结构表面形成字线结构的步骤之后包括:在所述半导体柱表面形成阵列排布的节点连接结构;在所述节点连接结构表面形成阵列排布的电荷存储结构。

在一些实施例中,在所述半导体柱表面形成阵列排布的节点连接结构的步骤进一步包括:沉积第二导电层;刻蚀所述第二导电层形成阵列排布的所述节点连接结构。

在一些实施例中,在所述节点连接结构表面形成阵列排布的电荷存储结构的步骤之前包括:在所述节点连接结构之间的间隙形成第四绝缘层。

上述技术方案,在两列半导体柱之间设置一字线结构,使用一字线结构控制两列半导体柱,减少了隔离层的设置,优化了布局空间;同时,优化晶体管开关电路,使用两字线结构控制一列半导体柱,实现对晶体管开关的精准控制,同时可以减小施加在每个字线结构上的电压,减小高电压对芯片带来的损害,提高芯片的使用寿命。此外,将位线与节点连接结构分布于不同的平面,释放更充分的布线空间,使位线与节点连接结构的尺寸不受其他结构约束,提高位线布线的宽度和密度。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

附图说明

为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简要介绍。显而易见地,下面描述中的附图仅是本公开的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

附图1所示为一种半导体器件的结构示意图。

附图2所示为本公开所述半导体器件的一实施例的结构示意图。

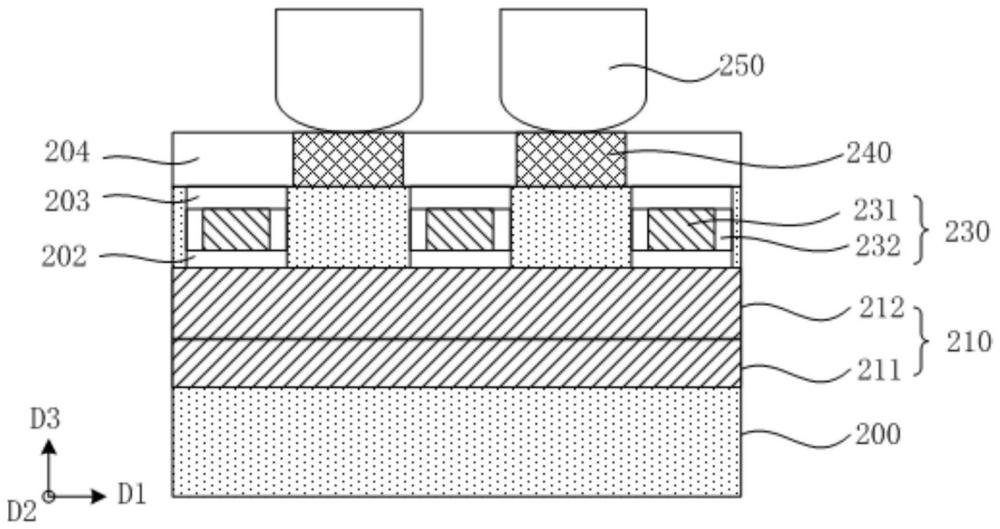

附图3A为附图2沿AA’方向的剖视图。

附图3B为附图2沿BB’方向的剖视图。

附图3C为附图2沿CC’方向的剖视图。

附图4所示为本公开所述半导体器件的制备方法的一实施例的步骤流程图。

附图5A~5O所示为本公开所述半导体器件的制备方法的一实施例的工艺流程图。

具体实施方式

下面结合附图对本公开提供的半导体器件及其制备方法的具体实施方式做详细说明。在详述本公开实施例时,为便于说明,示意图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本申请的保护范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。

附图1所示为一种半导体器件的结构示意图。所述半导体器件包括:衬底10、位线111、位线连接结构112、字线121、栅极介质层122、绝缘层13、节点连接结构14、以及电荷存储结构15。所述字线121与栅极介质层122组成字线结构,所述字线结构位于所述衬底10内部。所述位线111与所述节点连接结构14位于所述衬底10表面且位于同一平面。所述位线连接结构112位于所述衬底10内部且位于所述位线111沿第三方向D3的表面。所述位线连接结构112与所述位线111组成位线结构,并通过绝缘层13与所述字线结构绝缘。所述电荷存储结构15位于所述节点连接结构14表面。

本实施例以一条字线控制一个晶体管的开关,需要提供足够高的电压。因此,本公开提供一种半导体器件及其制备方法,以改进晶体管布线结构并优化晶体管开关电路。

附图2所示为本公开所述半导体器件的一实施例的结构示意图,其中,在表面不可见的内部结构用虚线绘制。附图3A为附图2沿AA’方向的剖视图。附图3B为附图2沿BB’方向的剖视图。附图3C为附图2沿CC’方向的剖视图。结合参考附图2~附图3C,所述半导体器件包括:衬底200;位线结构210,设置于所述衬底200表面,沿第一方向D1延伸,多条所述位线结构210沿第二方向D2排布,所述第一方向D1垂直于所述第二方向D2;半导体柱220,设置于所述位线结构210表面且阵列排布;字线结构230,设置于所述位线结构210表面,且与所述位线结构210绝缘,所述字线结构230位于所述半导体柱220之间,且沿所述第二方向D2延伸,多条所述字线结构230与所述半导体柱220沿所述第一方向D1间隔排布,在所述第一方向D1上相邻的两个所述半导体柱220共用同一所述字线结构230,且每一所述半导体柱220由在所述第一方向D1上位于其两侧的两条所述字线结构230共同控制。

在一些半导体器件中,在相邻两列半导体柱之间设置两条字线结构,则需要在两条字线结构之间设置隔离层,以避免两条字线结构导通。而在本实施例中,在相邻两列半导体柱220之间设置一字线结构230,使用同一字线结构230控制两列半导体柱220,减少了隔离层的设置,优化了布局空间;同时,优化晶体管开关电路,使用设置在同一列半导体柱两侧的两字线结构230控制该列半导体柱220,实现对晶体管开关的精准控制,同时可以减小施加在每条字线231的电压,减小高电压对芯片带来的损害,提高芯片的使用寿命。

所述衬底200的材料可以为单晶硅(Si)、单晶锗(Ge)、或硅锗(GeSi)、碳化硅(SiC);也可以是绝缘体上硅(SOI),绝缘体上锗(GOI);或者还可以为其它的材料,例如砷化镓等Ⅲ-Ⅴ族化合物。本实施例中,所述衬底200的材料为单晶硅(Si)。

所述半导体柱220包括但不限于单晶硅、多晶硅、IGZO等氧化物半导体材料、InGaAs及GaN等化合物半导体材料。本实施例中,所述半导体柱220的材料为单晶硅(Si)。

作为一实施例,在所述第一方向D1上位于所述半导体柱220两侧的两条所述字线结构230用于加载电性相反的电压。在所述半导体柱220一侧的字线结构230通正电压,另一侧的字线结构通负电压,在电压较小的情况下实现较大的电压差,起到降低导通所需的阈值电压、节约能耗的作用。

在本公开实施例中,所述位线结构210进一步包括:位线211,设置于所述衬底200表面,沿所述第一方向D1延伸,多条所述位线211沿第二方向D2排布;位线连接结构212,用于连接所述位线211与所述半导体柱220,设置于所述位线211表面,沿所述第一方向D1延伸,多条所述位线连接结构212沿所述第二方向D2排布。在本实施例中,所述位线211的材料为金属钨。在其他实施例中,所述位线211的材料还可以为氮化钛、金属硅化物、铜、以及铜钨合金。所述位线连接结构212的材料为多晶硅。

作为一实施例,所述半导体器件还包括第一绝缘层201,所述第一绝缘层201设置于多条所述位线结构210之间。所述第一绝缘层201可为氮化硅层、碳氧化硅层、以及氧化硅层,用于绝缘各所述位线结构210。

在本公开实施例中,所述字线结构230进一步包括:字线231,设置于所述位线结构210表面,且与所述位线结构210绝缘,所述字线231沿第二方向D2延伸,且多条所述字线231沿所述第一方向D1间隔排布;栅极介质层232,设置于所述字线231与所述半导体柱220之间。两列所述半导体柱220共用同一字线231,所述字线231与所述字线231两侧的半导体柱220之间设置有栅极介质层232。在本实施例中,所述字线231的材料为金属钨。在其他实施例中,所述字线231的材料还可以为氮化钛、金属硅化物、铜、以及铜钨合金。所述栅极介质层232为氧化硅层或高K介质层,用于绝缘所述字线231与所述半导体柱220。

作为一实施例,所述半导体器件还包括:第二绝缘层202,设置于所述字线结构230与所述位线结构210之间,以及在第二方向D2上相邻的所述半导体柱220之间;第三绝缘层203,设置于所述字线结构230表面,且至少位于所述半导体柱220之间。所述第二绝缘层202可为氮化硅层、碳氧化硅层、以及氧化硅层,用于绝缘各所述字线结构230、在第二方向D2上绝缘各半导体柱220、以及绝缘所述字线结构230与所述位线结构210。所述第三绝缘层203为氮化硅层、碳氧化硅层、以及氧化硅层,用于绝缘所述字线结构230与后续膜层以及绝缘各所述半导体柱220。

在本公开实施例中,所述半导体器件还包括节点连接结构240,所述节点连接结构240设置于所述半导体柱220背离所述位线结构210的一端且阵列排布。作为一实施例,所述节点连接结构240由多晶硅层和位于多晶硅层表面的金属层组成。所述金属层的材料可以为钨、氮化钛、金属硅化物、铜、以及铜钨合金。所述节点连接结构240与所述位线结构210沿第三方向D3分布于所述半导体柱220两端。附图1的实施例中,所述半导体器件中位线与节点连接结构位于字线同一侧的平面。然而,随着芯片的继续微缩,所述位于字线同一侧的平面结构已经不能满足布线需求。因此,在附图2~附图3C所示的实施例中,通过改变所述节点连接结构240与所述位线结构210的相对位置,设置于不同的平面,使所述节点连接结构240与所述位线结构210的位置关系从设置在字线结构同一侧的平面位置关系变成设置在字线结构两侧的立体位置关系,释放更充分的布线空间,使位线211与节点连接结构240的尺寸不受其他结构约束,提高位线布线的宽度和密度。

在本公开实施例中,所述半导体器件还包括:第四绝缘层204,设置于所述第二绝缘层202和所述第三绝缘层203表面,至少位于所述节点连接结构240之间。所述第四绝缘层204为氮化硅层、碳氧化硅层、以及氧化硅层,用于绝缘各所述节点连接结构240。

在本公开实施例中,所述半导体器件还包括电荷存储结构250,所述电荷存储结构250阵列排布于所述节点连接结构240表面。所述节点连接结构240用于连接所述半导体柱220与所述电荷存储结构250。所述电荷存储结构包括但不限于电容器。

上述技术方案,在两列半导体柱220之间设置一条字线231,使用一字线231控制两列半导体柱220,减少了隔离层的设置,优化了布局空间;同时,优化晶体管开关电路,使用两条字线231控制一列半导体柱220,实现对晶体管开关的精准控制,同时可以减小施加在每条字线231的电压,减小高电压对芯片带来的损害,提高芯片的使用寿命。此外,将位线211与节点连接结构240分布于不同的平面,释放更充分的布线空间,使位线211与节点连接结构240的尺寸不受其他结构约束,提高位线布线的宽度和密度。

本公开实施例还提供一种上述半导体器件的制备方法,附图4所示为本公开所述半导体存储结构的制备方法的一实施例的步骤示意图,包括如下步骤:步骤S41,提供一衬底;步骤S42,在所述衬底表面形成位线结构,所述位线结构沿第一方向延伸,多条所述位线结构沿第二方向排布,所述第一方向垂直于所述第二方向;步骤S43,在所述位线结构表面形成阵列排布的半导体柱;步骤S44,在所述位线结构表面形成字线结构,所述字线结构与所述位线结构绝缘,且位于所述半导体柱之间,沿所述第二方向延伸,多条所述字线结构与所述半导体柱沿所述第一方向间隔排布,在所述第一方向上相邻的两个所述半导体柱共用同一所述字线结构,且每一所述半导体柱由在所述第一方向上位于其两侧的两条所述字线结构共同控制。

附图5A~5O所示为本公开所述半导体器件的制备方法的一实施例的工艺流程图。附图5A~附图5G所示为附图2沿BB’方向的剖视图的后续工艺图,附图5H~附图5O所示为附图2沿AA’方向的剖视图的后续工艺图。

参考步骤S41以及附图5A,提供一衬底200。衬底200的材料可以为单晶硅(Si)、单晶锗(Ge)、或硅锗(GeSi)、碳化硅(SiC);也可以是绝缘体上硅(SOI),绝缘体上锗(GOI);或者还可以为其它的材料,例如砷化镓等Ⅲ-Ⅴ族化合物。本实施例中,所述衬底200的材料为单晶硅(Si)。

参考步骤S42以及附图5D,在所述衬底200表面形成位线结构210,所述位线结构210沿第一方向D1延伸,多条所述位线结构210沿第二方向D2排布,所述第一方向D1垂直于所述第二方向D2。

作为一实施例,如附图5B~附图5D所示,本公开提供了一种在所述衬底200表面形成位线结构210的方法,进一步包括如下步骤:

如附图5B所示,在所述衬底200表面形成第一导电层501。所述第一导电层501进一步包括第一金属层521以及第一多晶硅层531。在一些实施例中,可采用化学气相沉积、原子层沉积等工艺在所述衬底200表面沉积金属材料,形成所述第一金属层521。所述金属材料包括但不限于金属钨、氮化钛、金属硅化物、铜、以及铜钨合金。可采用化学气相沉积、原子层沉积等工艺在所述第一金属层521表面沉积多晶硅,形成所述第一多晶硅层531。

如附图5C所示,刻蚀所述第一导电层501形成第一沟槽511,所述第一沟槽沿511所述第一方向D1延伸。

如附图5D所示,在所述第一沟槽511内形成第一绝缘层201,保留的所述第一导电层501(绘示于图5C)作为所述位线结构210。所述第一绝缘层201可为氮化硅层、碳氧化硅层、以及氧化硅层。在一些实施例中,形成第一绝缘层201的方法包括但不限于热氧化、化学气相沉积、等离子体化学气相沉积及原子层沉积。在形成第一绝缘层201之后,还进一步包括平坦化所述第一绝缘层201以及所述位线结构210的步骤。作为一具体实施例,所述第一金属层521(绘示于图5C)作为位线211,所述第一多晶硅层531(绘示于图5C)作为位线连接结构212。

完成上述步骤,即可得到附图5D所示的位线结构210。

参考步骤S43以及附图5H,在所述位线结构210表面形成阵列排布的半导体柱220。

作为一实施例,如附图5E~附图5H所示,本公开提供了一种在所述位线结构210表面形成阵列排布的半导体柱220的方法,进一步包括如下步骤:

如附图5E所示,在所述位线结构210表面形成半导体层541。所述半导体层541包括但不限于单晶硅、多晶硅、IGZO等氧化物半导体材料、InGaAs及GaN等化合物半导体材料。本实施例中,所述半导体层541的材料为单晶硅(Si)。形成半导体层541的方法包括但不限于单晶硅自生长或吸附对接另一片薄的晶圆。

如附图5F所示,刻蚀所述半导体层541形成第二沟槽512,所述第二沟槽512沿第一方向D1延伸。

如附图5G所示,在所述第二沟槽512(绘示于图5F)内形成第一隔离层551。所述第一隔离层551可为氮化硅层、碳氧化硅层、以及氧化硅层。在一些实施例中,形成第一隔离层551的方法包括但不限于热氧化、化学气相沉积、等离子体化学气相沉积及原子层沉积。在形成第一隔离层551之后,还进一步包括平坦化所述第一隔离层551以及所述半导体层541的步骤。

值得注意的是,本实施例附图5H~附图5O的工艺图是沿附图2中AA’方向的剖视图示意。如附图5H所示,刻蚀所述半导体层541(绘示于图5G)和所述第一隔离层551形成第三沟槽513,所述第三沟槽513沿第二方向D2延伸,刻蚀后的所述半导体层541(绘示于图5G)作为所述半导体柱220。

完成上述步骤,即可得到附图5H所示的半导体柱220。

参考步骤S44以及附图5L,在所述位线结构210表面形成字线结构230,所述字线结构230与所述位线结构210绝缘,且位于所述半导体柱220之间,沿所述第二方向D2延伸,多条所述字线结构230与所述半导体柱220沿所述第一方向D1间隔排布,在所述第一方向D1上相邻的两个所述半导体柱220共用同一所述字线结构230,且每一所述半导体柱220由在所述第一方向D1上位于其两侧的两条所述字线结构230共同控制。

作为一实施例,如附图5I~附图5L所示,本公开提供了一种在所述位线结构210表面形成字线结构230的方法,进一步包括如下步骤:

如附图5I所示,在所述第三沟槽513内形成第二隔离层552,所述第一隔离层551与所述第二隔离层552作为第二绝缘层202(绘示于图5L)。在所述第三沟槽513内沉积绝缘材料并部分刻蚀形成所述第二隔离层552,所述第二隔离层552可为氮化硅层、碳氧化硅层、以及氧化硅层。在一些实施例中,形成第二隔离层552的方法包括但不限于热氧化、化学气相沉积、等离子体化学气相沉积及原子层沉积。

如附图5J所示,形成栅极介质层232,所述栅极介质层232覆盖所述半导体柱220沿所述第一方向D1的两侧。在本实施例中,形成栅极介质层进一步包括在所述第二隔离层552表面沉积栅介质材料并自对准刻蚀形成所述栅极介质层232。所述栅极介质层232的表面在第三方向D3上低于所述半导体柱220的表面。所述栅介质材料可以为氧化硅或高K介质层。沉积栅介质材料的方法包括但不限于热氧化、化学气相沉积、等离子体化学气相沉积及原子层沉积。

如附图5K所示,在所述第二隔离层552表面及所述栅介质层232侧面沉积导电材料,作为字线231,所述栅极介质层232以及所述字线231共同构成所述字线结构230。在一些实施例中,可采用化学气相沉积、原子层沉积等工艺在所述第二隔离层552表面及所述栅介质层232侧面沉积金属材料,形成所述字线231。所述金属材料包括但不限于金属钨、氮化钛、金属硅化物、铜、以及铜钨合金。

如附图5L所示,在所述栅极介质层232以及所述字线231表面形成第三绝缘层203。所述第三绝缘层203可为氮化硅层、碳氧化硅层、以及氧化硅层。在一些实施例中,形成第三绝缘层203的方法包括但不限于热氧化、化学气相沉积、等离子体化学气相沉积及原子层沉积。在形成第三绝缘层203之后,还进一步包括平坦化所述第三绝缘层203的步骤。

完成上述步骤,即可得到附图5L所示的字线结构230。在两列半导体柱220之间设置一条字线结构230,使用一字线结构230控制两列半导体柱220,减少了隔离层的设置,优化了布局空间;同时,优化晶体管开关电路,使用两字线结构230控制一列半导体柱220,实现对晶体管开关的精准控制,同时可以减小施加在每个字线结构230的电压,减小高电压对芯片带来的损害,提高芯片的使用寿命。

继续参考附图2,在所述位线结构210表面形成字线结构230的步骤之后包括:在所述半导体柱220表面形成阵列排布的节点连接结构240;在所述节点连接结构240表面形成阵列排布的电荷存储结构250。

作为一实施例,如附图5M~附图5N所示,本公开提供了一种在所述半导体柱220表面形成阵列排布的节点连接结构240的方法,进一步包括如下步骤:

如附图5M所示,沉积第二导电层502。所述第二导电层502进一步包括第二多晶硅层532以及第二金属层522。在一些实施例中,可采用化学气相沉积、原子层沉积等工艺在所述半导体柱220、第二绝缘层202、以及第三绝缘层203表面沉积多晶硅,形成所述第二多晶硅层532。可采用化学气相沉积、原子层沉积等工艺在所述第二多晶硅层532表面沉积金属材料,形成所述第二金属层522。所述金属材料包括但不限于金属钨、氮化钛、金属硅化物、铜、以及铜钨合金。

如附图5N所示,刻蚀所述第二导电层502形成阵列排布的所述节点连接结构240。

完成上述步骤,即可得到附图5N所示的节点连接结构240。将位线结构210与节点连接结构240分布于不同的平面,释放更充分的布线空间,使位线结构210与节点连接结构240的尺寸不受其他结构约束,提高位线布线的宽度和密度。

作为一实施例,如附图5O所示,在所述节点连接结构240表面形成阵列排布的电荷存储结构250的步骤之前包括:在所述节点连接结构240之间的间隙形成第四绝缘层204。所述第四绝缘层204可为氮化硅层、碳氧化硅层、以及氧化硅层。在一些实施例中,形成第四绝缘层204的方法包括但不限于热氧化、化学气相沉积、等离子体化学气相沉积及原子层沉积。在形成第四绝缘层204之后,还进一步包括平坦化所述第四绝缘层204的步骤。

作为一实施例,如附图2所示,在所述节点连接结构240表面形成阵列排布的电荷存储结构250。所述节点连接结构240用于连接所述半导体柱220与所述电荷存储结构250,上述单元共同组成本公开所述的半导体器件,如附图2~附图3C所示。

上述技术方案,在两列半导体柱之间设置一条字线结构,使用同一字线结构控制两列半导体柱,减少了隔离层的设置,优化了布局空间;同时,优化晶体管开关电路,使用两字线结构控制一列半导体柱,实现对晶体管开关的精准控制,同时可以减小施加在每个字线结构的电压,减小高电压对芯片带来的损害,提高芯片的使用寿命。此外,将位线与节点连接结构分布于不同的平面,释放更充分的布线空间,使位线与节点连接结构的尺寸不受其他结构约束,提高位线布线的宽度和密度。

应注意到,在说明书中对“一实施例”、“实施例”、“示例性实施例”、“一些实施例”等的引用指示所描述的实施例可以包括特定的特征、结构或特性,但是每个实施例可能不一定包括该特定的特征、结构或特性。而且,这样的短语不一定指代相同的实施例。此外,当结合实施例描述特定的特征、结构或特性时,无论是否明确描述,结合其它实施例来实现这样的特征、结构或特性都在相关领域的技术人员的知识范围内。

通常,可以至少部分地从上下文中的用法理解术语。例如,如在本文中所使用的术语“一个或多个”至少部分取决于上下文,可以用于以单数意义描述任何特征、结构或特性,或可以用于以复数意义描述特征、结构或特征的组合。类似地,至少部分取决于上下文,诸如“一”、“某一”或“该”的术语同样可以被理解为表达单数用法或表达复数用法。另外,术语“基于”可以被理解为不一定旨在表达一组排他性的因素,而是可以替代地,同样至少部分地取决于上下文,允许存在不一定明确描述的其它因素。在本说明书中也应当注意的是,“连接/耦接”不仅指一个部件与另一个部件直接耦接,也指一个部件通过中间部件与另一个部件间接地耦接。

需要说明的是,本公开的文件中涉及的术语“包括”和“具有”以及它们的变形,意图在于覆盖不排他的包含。术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序,除非上下文有明确指示,应该理解这样使用的数据在适当情况下可以互换。另外,在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互组合。此外,在以上说明中,省略了对公知组件和技术的描述,以避免不必要地混淆本公开的概念。上述各个实施例中,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同/相似的部分互相参见即可。

以上所述仅是本公开的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本公开原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本公开的保护范围。

- 半导体器件、半导体封装及制造半导体器件的方法

- 半导体器件及其制作方法、半导体器件测试方法

- 提高氮化硅耐腐蚀性的方法和半导体器件的制备方法

- 半导体器件和用于构造半导体器件的方法

- 制造半导体器件的方法和半导体器件

- 半导体器件中孔、半导体器件的制备方法及半导体器件

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置