神经元电路

文献发布时间:2023-06-19 09:26:02

技术领域

本发明涉及电路领域,且特别是有关于一种神经元电路(neural circuit)。

背景技术

在现今的生活中,人工智能(Artificial Intelligence,AI)广泛地应用于不同的技术领域中,以达到辨识、警示、操作协助等应用。但由于AI发展快速、各种新型网络提出,且硬件效能需求也不断被拉高。为了因应人工智能发展的需求,高效人工智能的运算硬件亦成为主要的发展目标。

进一步,实现人工智能的运算硬件主要可通过冯纽曼(Von Neumann)结构来实现,其主要是通过存储器储存权重值,以及通过处理单元处理输入信号并存取存储器权重值产生运算结果来进行神经元运算。但由于处理单元进行运算都需由存储器中所存取权重信息,会大幅消耗功率且造成运算延迟,冯纽曼结构会面临到冯纽曼瓶颈(Von NeumannBottleneck),进而限制神经元硬件的功耗与运算速率表现。

发明内容

为了解决上述技术问题,本发明目的在于提供一种神经元电路,其可改善神经元电路在功耗与运算速率上的表现。

本发明的神经元电路包括神经元阵列。神经元阵列包括多个半导体元件,其中每一个半导体元件分别储存有权重值以产生相对应的输出电流或对应的等效电阻值,神经元阵列分别接收多个输入信号,以控制神经元阵列中半导体元件并分别产生的输出电流或改变等效电阻,由于半导体元件之间相互耦接,使得神经元阵列的输出可产生与输入信号及权重状态相关的总电流或总等效电阻值,以达到高能效的运算结果。

因此,本发明提供的神经元电路,因不需要额外至储存装置储存权重值的情况下,可通过本发明提出的神经元电路中的各半导体元件来储存相对应的权重值,进一步改善先前技术中存取权重值时所导致的运算功率及运算延迟的缺点,且有效降低制造成本。

附图说明

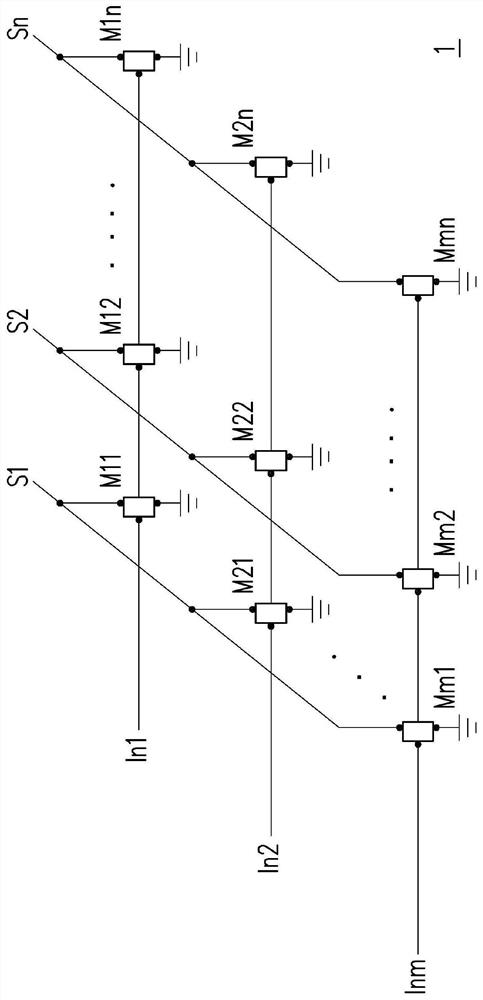

图1为本发明实施例一神经元阵列的示意图;

图2为本发明实施例另一神经元阵列的示意图;

图3为本发明实施例另一神经元阵列的示意图;

图4为本发明实施例另一神经元阵列的示意图;

图5为本发明实施例另一神经元阵列的示意图;

图6为本发明实施例另一神经元阵列的示意图;

图7为本发明实施例另一神经元阵列的示意图;

图8为本发明实施例另一神经元阵列的部分布局图;

图9A为本发明实施例另一神经元阵列的示意图;

图9B、9C、9D绘示了图9A的虚线圈示处的不同金属层连接实施例;

图10为本发明实施例另一神经元阵列的示意图;

图11为本发明实施例一神经元阵列产生运算结果的等效示意图;

图12为本发明实施例一神经元阵列输出信号处理的概念示意图;

图13为本发明实施例一神经元阵列输出信号处理的概念示意图;

图14为本发明实施例一神经元阵列输出信号处理的概念示意图。

符号说明:

1、2、3、4、5、6、7、8、9、10、11、12、13、14:神经元阵列

110、120、130、140:运算电路

141:电流传感器

CL:电容

Gnd:接地电压

In1~Inm:输入信号

L1、L2、L3、L4:金属层

M11~Mmn、MS1:半导体元件

R12、R13:电阻

S1~Sn:输出端

Wt1~Wtm:权重调整信号

VD11~VDmn、VG11~VGmn:介层窗插(contact plug)

Vdd:操作电压

Vout:输出电压

Vref3:参考电压

D11~Dmn:扩散层

具体实施方式

为让本发明的上述特征和效果能阐述的更明确易懂,下文特举实施例,并配合说明书附图作详细说明如下。

请参考图1,图1为本发明实施例一神经元阵列1的示意图。神经元阵列1包含有多个半导体元件M11~Mmn,其中每个半导体元件存有相对应的权重值以于使能或开启时产生相对应的输出电流或等效阻值。在本实施例中,半导体元件M11~Mmn可被分为n行与m列,而每一行的半导体元件(例如半导体元件M11、M21~Mm1、M12、M22~Mm2…等)可被分为相同的神经元子群组(下方说明书的说明将M11、M21~Mm1称为第一神经子群组、M12、M22~Mm2称为第二神经子群组…等,依此类推),且共同耦接至一输出端(例如输出端S1~Sn),而每一列的半导体元件(例如半导体元件M11~1n、M21~M2n…等)会共同接收一输入信号(例如输入信号In1~Inm)来控制该列半导体元件的电流大小或等效阻值。因此,神经元阵列1中的每个半导体元件M11~Mmn可被设计为神经元胞,用来储存相对应的权重值使每个半导体元件M11~Mmn产生相对应的电流或等效电阻,每个输出端S1~Sn上会流过每个神经元子群组中所有半导体元件的电流,通过判断输出端上的电流或电压可产生相对应于每个神经元子群组的运算结果。其中,神经元阵列1的行数与列数可依据不同的设计需求进行调整,并不受限于本实施例所记载的内容。依据不同的设计概念及使用者需求,半导体元件可具有不同的实施方式。在一实施例中,半导体元件可为金氧半场效晶体管(Metal OxideSemiconductor Field-Effect-Transistor、MOSFET)。在一实施例中,半导体元件可为双极性晶体管(Bipolar Junction Transistor,BJT)。在一实施例中,半导体元件可为真空管(Vacuum Tube)。在一实施例中,半导体元件可为量子闸。以下说明内容以示例性的方式,针对以半导体元件为金氧半场效晶体管的实施方式进行说明,但本发明所属领域具通常知识者当可明白本发明的范畴不以此为限。

进一步,神经元子群组中的每个半导体元件具有第一端、第二端及控制端。半导体元件依据不同的设置关系以及接收信号会储存有相对应的权重值。在一实施例中,每个半导体元件中的栅极宽度长度比会依据每个半导体元件相对应的权重值被调整。举例而言,半导体元件中的栅极宽度长度比可依据设计所需的权重值被加大或降低,进而调整每个半导体元件的输出电流或等效阻值。换言之,每个半导体元件可依据被设置的栅极的宽度长度比来储存相对应的权重值,以产生相对应的输出电流或等效阻值。在一实施例中,每个半导体元件的阈值电压会依据其相对应的权重值被设置。举例而言,半导体元件的阈值电压可依据设计的权重值被加大或降低,在输入信号的电压相同的情况下,每个半导体元件的控制端与第二端(例如栅极与源极)之间电压差虽然不变,但每个半导体元件的阈值电压产生可依据相对应权重值使每个半导体元件产生相对应的输出电流或等效阻值。换言之,每个半导体元件可依据被设置的阈值电压来储存相对应的权重值。在一实施例中,半导体元件M11~Mmn可以通过低阈值电压(Low Threshold Voltage、LVT)或超低阈值电压(UltraLow Threshold Voltage、ULVT)等不同制造方法制成,故半导体元件的控制端与第二端(例如栅极与源极)之间的电压差可产生不同的输出电流或等效阻值。因此,神经元阵列1可依据半导体元件被设置的不同的阈值电压调整半导体元件的权重值。

因此,每个半导体元件可于控制端(例如栅极)接收相对应的输入信号In1~Inm来控制每个半导体元件所产生的电流值或等效阻值。而每个神经元子群组的每个半导体元件的第一端(例如漏极)会共同耦接于一输出端(输出端S1~Sn的其中之一),且每个半导体元件的第二端(例如源极)会耦接于一第一参考电压(例如一接地电压Gnd)。因此,每个神经元子群组可依据输入信号In1~Inm进行操作且于输出端产生运算结果(例如第一神经子群组于输出端S1产生运算结果、第二神经子群组于输出端S2产生运算结果…等),进而实现神经元电路的乘加运算。针对每个半导体元件如何储存权重值(例如依据栅极的宽度长度比、栅极源极电压差以及阈值电压等)来产生相对应的输出电流或等效阻值的细节,其应为本领域技术人员所熟知,故于此不多赘述。

简言之,在不需要额外的储存装置储存权重值的情况下,神经元阵列1即可通过每个半导体元件来储存相对应的权重值,进一步改善先前技术中存取权重值时所导致的运算功率及运算延迟的缺点,且有效降低制造成本。

请参考图2,图2为本发明实施例另一神经元阵列2的示意图。神经元阵列2相似于图1所绘示的神经元阵列1,故相同元件以相同符号进行标示。神经元阵列2与神经元阵列1的差别在于,神经元阵列2接收多个权重调整信号Wt1~Wtm,分别传送至每列的半导体元件的第二端(例如源极)。因此,神经元阵列2中每个神经元子群组的所有半导体元件的第一端(例如漏极)耦接于相同的输出端,每个神经元子群组的每个半导体元件的控制端(例如栅极)分别接收输入信号,每个神经元子群组的每个半导体元件的第二端(例如源极)分别接收权重调整信号,换言之,每个半导体元件除了依据栅极宽度长度比及阈值电压调整输出电流或等效阻值之外,还依据每个半导体元件所接收的输入信号以及权重调整信号的一差值调整所产生的输出电流或等效阻值。而每个神经元子群组会接收输入信号In1~Inm及权重调整信号Wt1~Wtm,并据此于相对应的输出端产生运算结果。

请参考图3,图3为本发明实施例另一神经元阵列3的示意图。神经元阵列3中每个神经元子群组的每个半导体元件的第一端(例如漏极)分别接收相对应的输入信号,每个神经元子群组的每个半导体元件的栅极分别接收相对应的权重调整信号,每个神经元子群组的所有半导体元件的第二端(例如源极)会共同耦接至相同的输出端(输出端S1~Sn的其中之一)。因此,神经元阵列3可依据权重调整信号Wt1~Wtm控制每个半导体元件的开启或关闭,且依据输入信号In1~Inm调整每个半导体元件产生的输出电流或等效阻值,使每个神经元子群组分别于相对应的输出端上产生相对应的运算结果。

请参考图4,图4为本发明实施例另一神经元阵列4的示意图。神经元阵列4中每个神经元子群组的所有半导体元件的第一端(例如漏极)会共同耦接至相同的输出端(输出端S1~Sn的其中之一),每个神经元子群组的每个半导体元件的控制端(例如栅极)分别接收相对应的输入信号,每个神经元子群组的所有半导体元件的第二端(例如源极)接收相同的权重调整信号(例如第一神经子群组接收权重调整信号Wt1、第二神经子群组接收权重调整信号Wt2…等)。因此,神经元阵列4可依据输入信号In1~Inm分别控制每个半导体元件的开启或关闭,且依据权重调整信号Wt1~Wtn分别调整每个神经元子群组的输出电流或等效阻值,使每个神经元子群组于相对应的输出端上产生相对应的运算结果。

请参考图5,图5为本发明实施例另一神经元阵列5的示意图。神经元阵列5中每个神经元子群组的所有半导体元件的第一端(例如漏极)会共同接收相同的权重调整信号(权重调整信号Wt1~Wtn的其中之一),每个神经元子群组的每个半导体元件的控制端(例如栅极)分别接收相对应的输入信号,每个神经元子群组的所有半导体元件的第二端(例如源极)共同耦接至相同的输出端(输出端S1~Sn的其中之一)。因此,神经元阵列5可依据输入信号In1~Inm分别控制每个半导体元件的开启或关闭,且依据权重调整信号Wt1~Wtn分别调整相对应的神经元子群组的输出电流或等效阻值,使每个神经元子群组分别于相对应的输出端上产生运算结果。

请参考图6,图6为本发明实施例另一神经元阵列6的示意图。神经元阵列6相似于图1所绘示的神经元阵列1,故相同元件以相同符号进行标示。在神经元阵列6中,部分的半导体元件的第一端(例如漏极)会分别通过介层窗插连接至或断开于金属层上的导线(举例而言,半导体元件M11、M1n、M21、M2n、Mm2、Mmn的漏极分别通过介层窗插VD11、VD1n、VD21、VD2n、VDm2、VDmn连接至导线)。当半导体元件的第一端(例如漏极)上没有设置介层窗插时,半导体元件即无法将所产生的输出电流或等效电阻反映于输出端(举例而言,半导体元件M12、M22、Mm1的漏极没有设置介层窗插)。换言之,神经元阵列6中每个半导体元件会通过第一端(例如漏极)上的介层窗插调整半导体元件相对应的权重值。举例而言,如图6所示,半导体元件M12的第一端(例如漏极)上虚线圈示处未具有介层窗插,故半导体元件M12的权重值可视为被调整为零,进一步调整每个半导体元件的权重值。

请参考图7,图7为本发明实施例另一神经元阵列7的示意图。神经元阵列7相似于图1所绘示的神经元阵列1,故相同元件以相同符号进行标示。在神经元阵列7中,每个半导体元件的控制端(例如栅极)会分别通过介层窗插VG11~VGmn接收输入信号或第一参考电压(例如接地电压Gnd)。举例而言,半导体元件M11、M1n、M21、M22、Mm1、Mm2、Mmn的控制端(例如栅极)可分别通过介层窗插VG11、VG1n、VG21、VG22、VGm1、VGm2、VGmn接收相对应的输入信号,使半导体元件可据此产生输出电流或等效阻值。举例而言,半导体元件M12、M2n的控制端(例如栅极)可通过介层窗插VG12、VG2n接收第一参考电压(例如接地电压Gnd),半导体元件可依据介层窗插的设置而产生相对应的输出电流或等效阻值,故半导体元件的权重值可视为被调整为零。换言之,神经元阵列7可通过每个半导体元件的控制端(例如栅极)上的介层窗插调整半导体元件相对应的权重值。

请参考图8,图8为本发明实施例另一神经元阵列8的部分布局图。为了方便阅读,神经元阵列8的部分元件结构并未进行绘示(例如每个神经元群组中每个半导体元件的漏极以及源极的耦接关系,金属层走线等)。在神经元阵列8中,每个半导体元件会分别通过扩散层来调整每个半导体元件的权重值。举例而言,半导体元件M11、M1n、M21、M22、M2n、Mm1分别包含有扩散层D11、D1n、D21、D22、D2n、Dm1,故该些半导体元件可据此产生相对应的输出电流或等效阻值来进行运算。举例而言,半导体元件M12、Mm2、Mmn不包含有扩散层,故该些半导体元件不会产生相对应的输出电流或等效阻值来进行运算,该些半导体元件的权重值可视为被调整为零。换言之,神经元阵列8可通过每个半导体元件是否具有扩散层来调整每个半导体元件的权重值。

请参考图9A,图9A为本发明实施例另一神经元阵列9的示意图。神经元阵列9相似于图7所绘示的神经元阵列7,故相同元件以相同符号进行标示。针对神经元阵列的每个神经元群组,所有半导体元件的第一端(例如漏极)会共同通过一层或多层的金属层连接至输出端(输出端S1~Sn的其中之一)。举例而言,图9B、9C、9D绘示了图9A的虚线圈示处(输出端Sn)的不同金属层连接实施例。一般而言,较高层的金属层具有较大的厚度,因而具有较大的寄生电容与较小的寄生电阻。通过连接的金属层不同的设置方式,可适应性地调整每个神经元子群组的权重值。举例而言,如图9B所示,半导体元件M1n~Mmn于输出端Sn会通过金属层L1、L2连接。如图9C所示,半导体元件M1n~Mmn于输出端Sn会通过金属层L1、L3连接。如图9D所示,半导体元件M1n~Mmn于输出端Sn会通过金属层L1~L4连接。在一实施例中,改变输出端上金属层的连接方式可调整神经元子群组整体权重值的5%~30%。换言之,通过图9B~9D所绘示的不同金属层于输出端Sn上连接半导体元件M1n~Mmn,可适应性的依据不同设计需求调整神经元子群组的整体权重值,由此调整神经元群组中半导体元件的权重值。

请参考图10,图10为本发明实施例另一神经元阵列10的示意图。神经元阵列10相似于图7所绘示的神经元阵列7,故相同元件以相同符号进行标示。神经元阵列10与神经元阵列7的差异在于,神经元阵列10中的半导体元件包含一个或以上的并联子半导体元件。举例而言,半导体元件M11包含有四个并联子半导体元件,故半导体元件M11可依据其并联数调整所产生的输出电流或等效阻值。因此,神经元阵列10可依据每个半导体元件所包含的并联子半导体元件的数量调整权重值。

请参考图11,图11为本发明实施例一神经元阵列11产生运算结果的等效示意图。在本实施例中,神经元阵列11中的第一神经元子群组是通过运算电路110来判断输出端S1上的电压来产生运算结果。虽然图11中仅绘示第一神经元子群组产生运算结果的电路结构,但本领域具通常知识者应可依据第一神经元子群组类推其他神经元子群组的运算电路。详细而言,在本实施例中,第一神经元子群组会依据输入信号以及权重值产生相对应的输出电流或等效阻值,对输出端S1上的电容CL进行充放电而产生相对应的运算结果。为了获得输出端S1上相对应的运算结果,输出端S1耦接于电容CL的一端,且电容CL的另一端耦接于第一参考电压(例如接地电压Gnd)。输出端S1可先进行预充电至一特定电压,当输入信号In1~Inm输入至第一神经元子群组中的半导体元件M11~Mm1时,半导体元件M11~Mm1会产生相对应的输出电流或等效阻值,对电容CL的跨压进行充放电以产生相对应的输出电压。故神经元阵列11可依据量测输出电压Vout的变化来判断神经元子群组中的权重值,进而产生神经元子群组的运算结果。

请参考图12,图12为本发明实施例一神经元阵列12产生输出信号处理的概念示意图。在本实施例中,神经元阵列12的运算电路120是利用电阻分压来控制半导体元件以产生第一神经元子群组的运算结果。详细而言,输出端S1耦接于电阻R12的一端,且电阻R12的另一端接收第二参考电压(例如操作电压Vdd),且输出端S1耦接于半导体元件MS1的控制端(例如栅极)。因此,电阻R12的电阻值,以及神经元子群组中半导体元件M11~Mm1并联的等效电阻值,两者的电阻值比例可对输出端S1的电压进行偏压,且据此控制半导体元件MS1的输出电流或等效阻值。因此,当输出端S1上的电压大于或等于预设电压时(在本实施例中,输出端S1的电压与第三参考电压Vref3的差值大于或等于半导体元件MS1的阈值电压),会控制半导体元件MS1以将第三参考电压Vref3输出为输出电压Vout。当输出端S1上的电压小于预设电压时,半导体元件MS1会产生相对应的输出电流或等效阻值(例如,半导体元件MS1产生的输出电流可接近于零或等效阻值接近无限大)。故通过量测神经元阵列12中运算电路120的输出电压Vout,可判断第一神经元子群组的运算结果。

请参考图13,图13为本发明实施例一神经元阵列13产生输出信号的概念示意图。神经元阵列13相似于神经元阵列12,故相同元件以相同的符号进行标示。神经元阵列13与神经元阵列12的差别在于,运算电路130中的半导体元件MS1的一端耦接于一电容CL,且半导体元件MS1的另一端接收第一参考电压(例如接地电压Gnd)。而电容CL的另一端则接收第一参考电压(例如接地电压Gnd)。相似于神经元阵列12,神经元阵列13同样是利用输出端上的电阻分压来控制半导体元件MS1,通过半导体元件MS1的输出电流或等效阻值来对经预充电的电容CL放电,故神经元阵列13可依据量测输出电压Vout的电压变化来产生神经元子群组的运算结果。

在一实施例中,半导体元件MS1的栅极宽度长度比可适应性地变化,以调整相对应神经元子群组的权重值。举例而言,当半导体元件MS1的栅极宽度长度比增加时,则会加强驱动电容CL放电的能力,可视为增加整体神经元子群组半导体元件M11~Mm1的权重值。

请参考图14,图14为本发明实施例一神经元阵列14产生输出信号的概念示意图。神经元阵列14相似于神经元阵列13,故相同元件以相同的符号进行标示。神经元阵列14与神经元阵列13的差别在于,运算电路140中另外包括一电流传感器141串联于半导体元件MS1及电容CL之间,依据半导体元件MS1所产生的驱动电流的大小产生相对应的输出。在一实施例中,电流传感器141可依据输出电流产生类比或数位的输出信号,以作为运算结果。在一实施例中,电流传感器141产生的输出信号可驱动一计数器,依据计数器被电流传感器141驱动的次数作为运算结果。

综上所述,神经元电路可通过半导体元件的栅极宽度长度比以及阈值电压达成存储器内运算(Computing in Memory,CIM),且通过不同实施方式进一步调整其所储存的权重值,可有效克服先前技术中神经元电路的功耗及运算速率的缺点。

- 基于CMOS的神经元激活函数电路及神经元电路

- 神经元突触电路及神经元电路