一种晶圆的失效分析方法

文献发布时间:2023-06-19 09:26:02

技术领域

本申请实施例涉及半导体技术领域,涉及但不限于一种晶圆的失效分析方法。

背景技术

对于三维闪存结构的测试区域(Test Key,TSK),在物理失效分析(PhysicalFailure Analysis,PFA)时,需要采用感应耦合等离子体刻蚀(Inductively CoupledPlasma,ICP)技术去除样品中的硅来进行制样。当ICP的刻蚀时间超过10分钟时,位于贯穿阵列触点和贯穿硅触点(Through Array Contact&Through Silicon Contact,TAC&TSC)下方的金属层会受到损伤。

相关技术中为了避免金属层的损伤,多采用全手工抛光(Manual polish)的方式打磨样品中的硅,但是,全手工抛光的方式会增加时间成本以及制样难度,从而影响制样的效率。

发明内容

有鉴于此,本申请实施例提供一种晶圆的失效分析方法,通过对晶圆的测试区域中贯穿触点的表面进行保护,能够有效地阻止制样过程使用ICP技术时对样品造成损坏,且能够节省制样时间,提高制样效率。

本申请实施例的技术方案是这样实现的:

本申请实施例提供一种晶圆的失效分析方法,所述方法包括:

在所述晶圆的切割通道中,确定出目标测试区域,所述晶圆包括叠设的驱动晶圆层和阵列晶圆层,所述阵列晶圆层包括位于所述驱动晶圆层之上的堆叠层和位于所述堆叠层背离所述驱动晶圆层一侧的衬底,所述目标测试区域包括贯穿所述阵列晶圆层的贯穿触点以及形成于所述驱动晶圆层内且位于所述贯穿触点下方的测试结构;

对所述贯穿触点的表面进行保护处理,得到保护处理后的晶圆;

对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆;

对所述刻蚀处理后的晶圆进行失效分析。

在其他实施例中,所述贯穿触点包括与所述测试结构接触的测试贯穿触点和未与所述测试结构接触的非测试贯穿触点。

在其他实施例中,对所述贯穿触点的表面进行保护处理,包括:

根据所述目标测试区域中所述非测试贯穿触点的个数对所述贯穿触点的表面进行保护处理;

当所述目标测试区域中所述非测试贯穿触点的个数大于阈值时,通过形成覆盖所述目标测试区域的第一保护层对所述贯穿触点的表面进行所述保护处理;

当所述目标测试区域中所述非测试贯穿触点的个数小于或等于所述阈值时,通过在各个所述贯穿触点的表面形成第二保护层以对各所述贯穿触点的表面进行所述保护处理。

在其他实施例中,所述第一保护层包括聚酰亚胺保护膜。

在其他实施例中,所述在各个所述贯穿触点的表面形成第二保护层,包括:

通过沉积工艺在各个所述贯穿触点的表面形成所述第二保护层。

在其他实施例中,所述沉积工艺包括聚焦离子束工艺。

在其他实施例中,所述第二保护层包括金属层。

在其他实施例中,各所述贯穿触点包括贯穿所述衬底的贯穿硅触点和贯穿所述堆叠层并与所述驱动晶圆层和所述贯穿硅触点接触的贯穿阵列触点。

在其他实施例中,各所述贯穿触点的表面覆盖有铝垫,在所述通过形成覆盖所述目标测试区域的第一保护层对所述贯穿触点的表面进行所述保护处理之前,所述方法还包括:去除所述铝垫。

在其他实施例中,在所述对所述贯穿触点的表面进行保护处理之前,所述方法还包括:

通过所述测试贯穿触点向所述测试结构接入电信号并进行电性能分析,以得到电性能分析结果;

根据所述电性能分析结果对刻蚀处理前的刻蚀处理后的晶圆进行失效分析,当所述电性能分析结果表明所述测试贯穿触点和所述测试结构的电性能不满足预设条件时,对位于所述阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆。

在其他实施例中,所述对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀,包括:

采用等离子刻蚀工艺,对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀。

本申请实施例提供一种晶圆的失效分析方法,首先,在晶圆的切割通道中,确定出目标测试区域;其次,对目标测试区域中的贯穿触点的表面进行保护处理,得到保护处理后的晶圆;最后,对保护处理后的晶圆中位于阵列晶圆层中的衬底进行刻蚀,得到刻蚀处理后的晶圆,如此,可以实现对刻蚀处理后的晶圆进行失效分析,这样,在对晶圆进行刻蚀之前,首先对目标测试区域中的贯穿触点的表面进行保护处理,可以避免在刻蚀过程中对目标测试区域内部的其它结构产生损伤,且节省了制样时间,提高了制样效率。

附图说明

在附图(其不一定是按比例绘制的)中,相似的附图标记可在不同的视图中描述相似的部件。具有不同字母后缀的相似附图标记可表示相似部件的不同示例。附图以示例而非限制的方式大体示出了本文中所讨论的各个实施例。

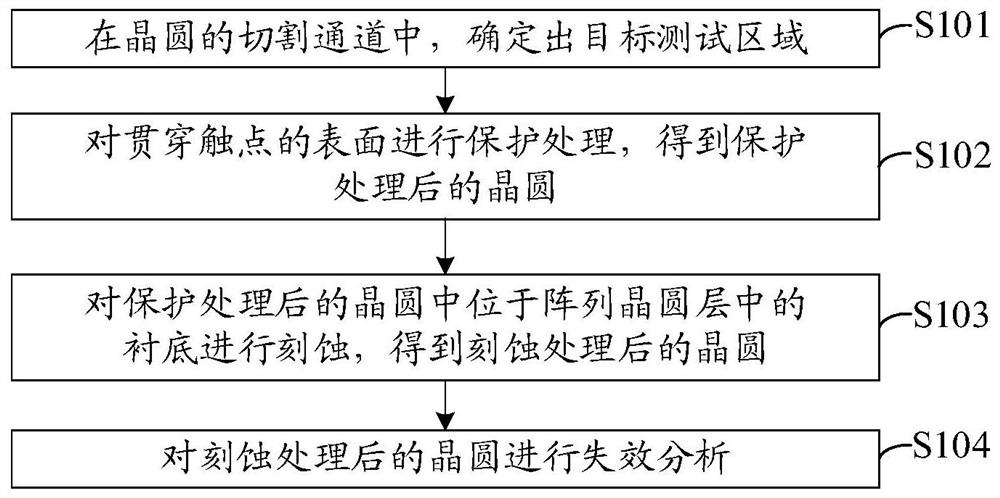

图1为本申请实施例提供的晶圆的失效分析方法的实现流程示意图;

图2A为本申请实施例提供的晶圆的结构示意图;

图2B为本申请实施例提供的目标测试区域的剖面结构示意图;

图2C为本申请实施例提供的经过保护处理后的晶圆的结构示意图;

图2D为本申请实施例提供的经过刻蚀处理后的晶圆的结构示意图;

图2E为本申请实施例提供的未经保护处理的部分晶圆的结构放大图(放大倍数1万倍);

图2F为本申请实施例提供的缺陷区域15的结构放大图(放大倍数4万倍);

图2G为本申请实施例提供的经过保护处理的部分晶圆的结构放大图(放大倍数1000倍);

图2H为本申请实施例提供的经过保护处理的部分晶圆的结构放大图(放大倍数1万倍);

图3A为本申请实施例提供的晶圆的失效分析方法的实现流程示意图;

图3B为本申请实施例提供的通过形成覆盖目标测试区域的第一保护层的方式进行保护处理的示意图;

图3C为本申请实施例通过在贯穿触点的表面进行形成第二保护层的方式,进行保护处理的示意图;

图4为本申请实施例提供的晶圆的失效分析方法的实现流程示意图;

图5A为本申请实施例提供的目标测试区域的剖面结构示意图;

图5B为本申请实施例提供的去除覆盖层后的目标测试区域的剖面结构示意图;

图5C为本申请实施例提供的去除铝垫后的目标测试区域的剖面结构示意图;

图5D为本申请实施例提供的通过形成聚酰亚胺保护膜的方式,进行保护处理后的目标测试区域的剖面结构示意图;

图6为本申请实施例提供的晶圆的失效分析方法的实现流程示意图;

图7A为本申请实施例提供的目标测试区域的剖面结构示意图;

图7B为本申请实施例提供的去除覆盖层后的目标测试区域的剖面结构示意图;

图7C为本申请实施例提供的形成金属层后的目标测试区域的剖面结构示意图;

图7D为本申请实施例提供的刻蚀衬底后的目标测试区域的剖面结构示意图;

图8为本申请实施例提供的晶圆的失效分析方法的实现流程示意图;

图9为本申请实施例提供的目标测试区域的剖面结构示意图。

具体实施方式

为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对发明的具体技术方案做进一步详细描述。以下实施例用于说明本申请,但不用来限制本申请的范围。

如本申请和权利要求书中所示,除非上下文明确提示例外情形,“一”、“一个”、“一种”和/或“该”等词并非特指单数,也可包括复数。一般来说,术语“包括”与“包含”仅提示包括已明确标识的步骤和元素,而这些步骤和元素不构成一个排他性的罗列,方法或者装置也可能包含其他的步骤或元素。

空间关系术语例如“在……上”、“在……下面”、“下面的”、“在……之下”、“在……之上”、“上面的”等,在这里可为了方便描述而被使用,从而描述图中所示的一个元件或特征与其他元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。当元件或层被称为“在……上”、“与……相邻”或“连接到”其他元件或层时,其可以直接地在其他元件或层上、与之相邻或连接到其他元件或层,或者可以存在居间的元件或层。

在详述本申请实施例时,为便于说明,表示器件结构的剖面图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本申请保护的范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。

图1为本申请实施例提供的晶圆的失效分析方法的实现流程示意图,如图1所示,所述方法包括以下步骤:

步骤S101、在所述晶圆的切割通道中,确定出目标测试区域。

这里,所述晶圆包括叠设的驱动晶圆层和阵列晶圆层,所述阵列晶圆层包括位于所述驱动晶圆层之上的堆叠层和位于所述堆叠层背离所述驱动晶圆层一侧的衬底,所述目标测试区域包括贯穿所述阵列晶圆层的贯穿触点以及形成于所述驱动晶圆层内且位于所述贯穿触点下方的测试结构,其中,测试结构和贯穿触点具有重叠的正投影区域。

如图2A所示,为本申请实施例提供的晶圆的结构示意图,可以看出,所述晶圆10中包括多个芯片11和切割通道12。这里,切割通道是晶圆上的多个芯片之间的间隙,所述切割通道12一方面用于分离芯片,另一方面用于设置不同的测试区域,以对所述芯片11的制备过程进行工艺监测。

本申请实施例中,根据需要测试的测试项目,在所述晶圆10的切割通道12中确定出目标测试区域12-1。例如,当需要测试互补金属氧化物半导体晶圆(ComplementaryMetal Oxide Semiconductor,CMOS)与阵列晶圆(Array Wafer)之间的结合能力时,需要设置蛇形结构的测试区域。

步骤S102、对所述贯穿触点的表面进行保护处理,得到保护处理后的晶圆。

如图2B所示,为本申请实施例提供的目标测试区域的剖面结构示意图,可以看出,目标测区域12-1由阵列晶圆层20和驱动晶圆层21组成,所述目标测试区域12-1包括贯穿所述阵列晶圆层20的贯穿触点201以及形成于所述驱动晶圆层21内且位于所述贯穿触点201下方的测试结构210。所述阵列晶圆层20由衬底205和堆叠层206组成。在本申请实施例中,所述阵列晶圆层20中包括贯穿触点201、202、203和204。所述贯穿触点包括贯穿硅触点和位于所述贯穿硅触点之下且与所述贯穿硅触点对应的贯穿阵列触点,其中,贯穿硅触点穿透衬底205,贯穿阵列触点穿透堆叠层206,例如,所述贯穿触点201包括:贯穿硅触点2011、和位于所述贯穿硅触点2011之下且与所述贯穿硅触点2011对应的贯穿阵列触点2012。

在一实施例中,所述贯穿触点包括与所述测试结构210接触的测试贯穿触点和未与所述测试结构210接触的非测试贯穿触点,其中,测试贯穿触点与测试结构210的两端接触,用于向测试结构210输入测试信号;非测试贯穿触点位于两测试贯穿触点之间的区域。如图2B中的贯穿触点201和204为测试贯穿触点,贯穿触点202和203即为非测试贯穿触点。

在一些实施例中,可以根据所述目标测试区域中所述非测试贯穿触点的个数对所述贯穿触点的表面进行保护处理。

本申请实施中,对所述目标测试区域中贯穿触点的表面进行保护处理是为了避免所述目标测试区域内部位于贯穿触点下方的其它结构在后续失效分析过程中受到损伤。

如图2C所示,为本申请实施例提供的经过保护处理后的晶圆的结构示意图,可以看出,本申请实施例中,通过保护层13对所述目标测试区域中贯穿触点的表面进行保护处理,以防止在后续过程中损伤所述目标测试区域内部的其它结构,得到了保护处理后的晶圆10'。

本申请实施例中,可以采用化学气相沉积(Chemical Vapor Deposition,CVD)或者原子层沉积(Atomic Layer Deposition,ALD)或者其他的任意一种沉积方式在所述贯穿触点的表面沉积保护层13,在实际选择时,可以根据工艺需要和生产条件进行沉积方式的选择,本实施例不做限定。

步骤S103、对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆。

这里,阵列晶圆层20的衬底205中存在单晶硅,本申请实施例中,在对晶圆进行失效分析之前,首先需要刻蚀去除所述阵列晶圆中的所有单晶硅,即去除所述衬底205。

如图2D所示,为本申请实施例提供的经过刻蚀处理后的晶圆的结构示意图,图中编号14对应的区域即为去除衬底之后的除目标测试区域12-1以外的区域,经过刻蚀处理后得到晶圆10”。

需要说明的是,这里的刻蚀方法可以是等离子刻蚀,也可以是其它刻蚀方法。

步骤S104、对所述刻蚀处理后的晶圆进行失效分析。

这里,经过刻蚀处理后的晶圆10”中,保留了一些核心的结构和叠层,通过这些核心的结构和叠层,对晶圆10”进行失效分析。

举例来说,在对某一片晶圆进行失效分析过程中,当不对晶圆进行保护处理时,晶圆的结构如图2E所示,图2E为未经保护处理的部分晶圆的结构放大图(放大倍数1万倍),可以看出,未经过保护处理的晶圆在失效分析过程中存在缺陷区域15(图中虚线框所示)。图2F为本申请实施例提供的缺陷区域15的结构放大图(放大倍数4万倍),从图2F中可以更加清楚地看到缺陷结构。当对晶圆进行保护处理时,晶圆的结构如图2G所示,图2G为经过保护处理的部分晶圆的结构放大图(放大倍数1000倍),可以看出,经过保护处理的晶圆在失效分析过程中不存在缺陷区域,整个晶圆样品的结构比较均匀和完整。图2H为经过保护处理的部分晶圆的结构放大图(放大倍数1万倍),从图2H中更加证明了这一结论。

本申请人经分析发现,在同等刻蚀条件下,贯穿触点区域的刻蚀速率大于硅衬底的刻蚀速率,当刻蚀时间较长时,贯穿阵列触点和贯穿硅触点会被刻穿,位于贯穿阵列触点和贯穿硅触点下方的测试结构会受到损伤。

本申请实施例提供的晶圆的失效分析方法,首先,在晶圆的切割通道中,确定出目标测试区域;其次,对目标测试区域中的贯穿触点表面进行保护处理,得到保护处理后的晶圆;最后,对保护处理后的晶圆中位于阵列晶圆层中的衬底进行刻蚀,得到刻蚀处理后的晶圆,如此,可以实现对刻蚀处理后的晶圆进行失效分析,这样,在对晶圆进行刻蚀之前,首先对目标测试区域中的贯穿触点的表面进行保护处理,可以避免在刻蚀过程中对目标测试区域内部位于贯穿触点下方的其它结构产生损伤,且节省了制样时间,提高了制样效率。

图3A为本申请实施例提供的晶圆的失效分析方法的实现流程示意图,如图3A所示,所述方法包括以下步骤:

步骤S301、在所述晶圆的切割通道中,确定出目标测试区域。

这里,所述晶圆包括叠设的驱动晶圆层和阵列晶圆层,所述阵列晶圆层包括位于所述驱动晶圆层之上的堆叠层和位于所述堆叠层背离所述驱动晶圆层一侧的衬底,所述目标测试区域包括贯穿所述阵列晶圆层的贯穿触点以及形成于所述驱动晶圆层内且位于所述贯穿触点下方的测试结构。所述贯穿触点包括与所述测试结构接触的测试贯穿触点和未与所述测试结构接触的非测试贯穿触点。

步骤S302、获取所述目标测试区域中非测试贯穿触点的个数。

步骤S303、判断所述非测试贯穿触点的个数是否大于阈值。

在一些实施例中,当所述非测试贯穿触点的个数大于阈值时,执行步骤S304;当所述非测试贯穿触点的个数小于或等于阈值时,执行步骤S305。

这里,所述阈值是预先设置的值,所述阈值可以是4个,也可以是6个。

步骤S304、通过形成覆盖所述目标测试区域的第一保护层对所述贯穿触点的表面进行所述保护处理,得到保护处理后的晶圆。

本申请实施例中,当所述非测试贯穿触点的个数大于所述阈值时,可以判断出所述目标测试区域较大,因此,采用第一保护层对整个目标测试区域进行覆盖,以实现对所述贯穿触点的表面进行保护处理,得到保护处理后的晶圆。

在一实施例中,所述第一保护层包括聚酰亚胺保护膜。

如图3B所示,为本申请实施例提供的通过形成覆盖目标测试区域的第一保护层的方式,进行保护处理的示意图,首先,在晶圆30中确定出目标测试区域301,通过形成覆盖所述目标测试区域301的第一保护层302对所述贯穿触点的表面进行所述保护处理,得到保护处理后的晶圆30'。

步骤S305、通过在各个所述贯穿触点的表面形成第二保护层以对所述贯穿触点的表面进行所述保护处理,得到保护处理后的晶圆。

本申请实施例中,当所述非测试贯穿触点的个数小于或等于所述阈值时,可以判断出所述目标测试区域较小,因此,采用第二保护层对每一贯穿触点的表面单独进行保护处理,得到保护处理后的晶圆。

在一些实施例中,在各个所述贯穿触点的表面形成第二保护层,包括:通过沉积工艺在各个所述贯穿触点的表面形成所述第二保护层。所述沉积工艺包括聚焦离子束工艺;所述第二保护层包括金属层,这里,所述第二保护层可以是金属钨层,或者金属铬层或者金属镍层。

在一些实施例中,每一所述贯穿触点的表面覆盖有铝垫,所述通过沉积工艺在各个所述贯穿触点的表面形成所述第二保护层,还包括:通过沉积工艺在各个所述贯穿触点的表面的铝垫上形成所述第二保护层。

如图3C所示,为本申请实施例提供的通过在贯穿触点的表面进行形成第二保护层的方式,进行保护处理的示意图,首先,在晶圆30-1中确定出位于目标测试区域的贯穿触点303,采用第二保护层304对所述贯穿触点303进行保护处理,得到保护处理后的晶圆30-1'。

步骤S306、采用等离子刻蚀工艺,对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆。

这里,所述等离子刻蚀工艺可以是:反应耦合等离子体刻蚀工艺。反应耦合等离子体刻蚀工艺是一种非常重要的半导体干法刻蚀技术,利用气压为10~1000帕的特定气体的辉光放电,产生能与所述衬底发生离子化学反应的分子或分子基团,生成可以挥发的产物,从而实现刻蚀过程。

本申请实施例中,通过等离子刻蚀工艺,可以对刻蚀的速率和刻蚀时间进行控制,以达到理想的刻蚀效果。

步骤S307、对所述刻蚀处理后的晶圆进行失效分析。

步骤S307的实现过程和实现的功能与上述实施例中步骤S104的实现过程和实现的功能相同,本申请实施例不再赘述。

本申请实施例提供的晶圆的失效分析方法,首先,根据目标测试区域中非测试贯穿触点的个数与阈值的相对大小关系,分别通过形成覆盖目标测试区域的第一保护层的方式或者在贯穿触点的表面形成第二保护层的方式对目标测试区域中贯穿触点的表面进行保护处理,得到保护处理后的晶圆;其次,采用等离子刻蚀技术,对保护处理后的晶圆中位于阵列晶圆层中的衬底进行刻蚀,得到刻蚀处理后的晶圆,如此,可以实现对刻蚀处理后的晶圆进行失效分析,这样,在对晶圆进行刻蚀之前,首先根据目标测试区域中非测试贯穿触点的个数对贯穿触点的表面进行保护处理,可以避免在刻蚀过程中对目标测试区域内部位于贯穿触点下方的其它结构产生损伤,且节省了制样时间,提高了制样效率。

图4为本申请实施例提供的晶圆的失效分析方法的实现流程示意图,如图4所示,所述方法包括以下步骤:

步骤S401、在所述晶圆的切割通道中,确定出目标测试区域。

这里,所述晶圆包括叠设的驱动晶圆层和阵列晶圆层,所述阵列晶圆层包括位于所述驱动晶圆层之上的堆叠层和位于所述堆叠层背离所述驱动晶圆层一侧的衬底,所述目标测试区域包括贯穿所述阵列晶圆层的贯穿触点以及形成于所述驱动晶圆层内且位于所述贯穿触点下方的测试结构。

在一些实施例中,所述阵列晶圆层还包括:位于所述衬底背离所述堆叠层一侧的覆盖层,且每一所述贯穿触点的表面覆盖有铝垫,这里,由于所述目标测试区域是属于晶圆的切割道中的结构,因此,所述目标测试区域的结构与所述晶圆的结构一致。

如图5A所示,为本申请实施例提供的目标测试区域的剖面结构示意图,可以看出,目标测试区域包括阵列晶圆层50和驱动晶圆层51,所述阵列晶圆层50由覆盖层501、铝垫502、衬底503和堆叠层504组成;所述衬底503中还包括:贯穿硅触点5031、5032、5033和5034;所述堆叠层504中还包括:贯穿阵列触点5041、5042、5043和5044,所述:贯穿硅触点5031、5032、5033和5034与所述贯穿阵列触点5041、5042、5043和5044一一对应。

本申请实施例中,所述覆盖层501包括:氮化硅层5011和氧化物层5012。所述铝垫502覆盖于每一所述贯穿硅触点5031、5032、5033和5034的表面,且位于所述覆盖层501中。

步骤S402、去除位于所述阵列晶圆层中的所述覆盖层。

如图5B所示,为本申请实施例提供的去除覆盖层后的目标测试区域的剖面结构示意图,本申请实施例中,在对所述目标测试区域中的贯穿触点进行保护之前,需要先去除位于衬底503上层的覆盖层501。

在一些实施例中,可以采用湿法刻蚀技术去除所述覆盖层501,也可以通过反应离子刻蚀技术(Reactive Ion Etching,RIE)去除所述覆盖层501。

步骤S403、去除铝垫。

如图5C所示,为本申请实施例提供的去除铝垫后的目标测试区域的剖面结构示意图;本申请实施例中,采用湿法刻蚀技术去除覆盖于所述每一贯穿硅触点表面的铝垫502,例如,可以采用浓盐酸、浓硫酸或者氢氟酸等刻蚀液进行湿法刻蚀。

步骤S404、通过形成覆盖所述目标测试区域的聚酰亚胺保护膜对所述贯穿触点的表面进行所述保护处理,得到保护处理后的晶圆。

在一些实施例中,在通过形成覆盖所述目标测试区域的聚酰亚胺保护膜对所述贯穿触点的表面进行所述保护处理之前,首先,采用刻蚀技术处理所述晶圆预设的时间,以除去所述贯穿硅触点表面的残留物。这里,预设的时间可以是10秒。

如图5D所示,为本申请实施例提供的通过形成聚酰亚胺保护膜的方式,进行保护处理后的目标测试区域的剖面结构示意图,即为保护处理后的晶圆的剖面结构示意图;本申请实施例中,所述聚酰亚胺保护膜52可以有效地阻滞电子的迁移,保护目标测试结构,使得目标测试结构具有较低的漏电流,并且所述聚酰亚胺保护膜52可以有效地防止保护膜下的目标测试区域中各层的化学腐蚀和潮气侵蚀。

步骤S405、对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆。

步骤S406、对所述刻蚀处理后的晶圆进行失效分析。

步骤S405和步骤S406的实现过程和实现的功能与上述实施例中步骤S103和步骤S104中的实现过程和实现的功能相同,本申请实施例不在赘述。

本申请实施例提供的晶圆的失效分析方法,在对目标测试区域中的贯穿触点进行保护之前,需要先去除位于阵列晶圆层中的覆膜层,并去除覆盖于贯穿硅触点表面的铝垫;其次,通过在目标测试区域表面形成聚酰亚胺保护膜,来对目标测试区域中的贯穿触点的表面进行保护处理,得到保护处理后的晶圆,最后,对保护处理后的晶圆中位于阵列晶圆层中的衬底进行刻蚀,并对刻蚀处理后的晶圆进行失效分析,这样,在对晶圆进行刻蚀之前,采用聚酰亚胺膜对目标测试区域进行保护处理,可以避免在刻蚀过程中对目标测试区域内部位于贯穿触点下方的其它结构产生损伤,且节省了制样时间,提高了制样效率。

图6为本申请实施例提供的晶圆的失效分析方法的实现流程示意图,如图6所示,所述方法包括以下步骤:

步骤S601、在所述晶圆的切割通道中,确定出目标测试区域。

这里,所述晶圆包括叠设的驱动晶圆层和阵列晶圆层,所述阵列晶圆层包括位于所述驱动晶圆层之上的堆叠层和位于所述堆叠层背离所述驱动晶圆层一侧的衬底,所述目标测试区域包括贯穿所述阵列晶圆层的贯穿触点以及形成于所述驱动晶圆层内且位于所述贯穿触点下方的测试结构。

在一些实施例中,所述阵列晶圆层还包括:位于所述衬底背离所述堆叠层一侧的覆盖层,且每一所述贯穿触点的表面覆盖有铝垫,这里,由于所述目标测试区域是属于晶圆的切割道中的结构,因此,所述目标测试区域的结构与所述晶圆的结构一致。

如图7A所示,为本申请实施例提供的目标测试区域的剖面结构示意图,所述目标测试区域包括:阵列晶圆层70和驱动晶圆层71,所述阵列晶圆层70由覆盖层701、铝垫702、衬底703和堆叠层704组成;所述覆盖层701包括:氮化硅层7011和氧化物层7012;所述衬底703中还包括:贯穿硅触点7031、7032、7033和7034;每一所述贯穿硅触点表面均覆盖有铝垫7021、7022、7023和7024。

所述堆叠层704中还包括:贯穿阵列触点7041、7042、7043和7044,所述贯穿硅触点7031、7032、7033和7034与所述贯穿阵列触点7041、7042、7043和7044一一对应。

步骤S602、去除位于所述阵列晶圆层中的所述覆盖层。

如图7B所示,为本申请实施例提供的去除覆盖层后的目标测试区域的剖面结构示意图。本申请实施例中,可以采用反应离子刻蚀的技术去除所述覆盖层701。

步骤S603、采用聚焦离子束工艺,在各个所述贯穿触点的表面形成金属层,以实现对所述贯穿触点的表面进行保护处理。

这里,所述聚焦离子束(Focused Ion beam,FIB)工艺是将离子源产生的离子束经过离子枪加速,聚焦后作用于样品表面的一种沉积工艺。这里,所述金属层可以是金属钨层。

如图7C所示,为本申请实施例提供的形成金属层后的目标测试区域的剖面结构示意图,所述每一贯穿硅触点7031、7032、7033和7034的表面覆盖有铝垫7021、7022、7023和7024,在每一铝垫的表面分别沉积金属层72。

步骤S604、采用等离子刻蚀工艺,对所述保护处理后的目标测试区域中位于阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆。

如图7D所示,为本申请实施例提供的刻蚀衬底后的目标测试区域的剖面结构示意图,即为刻蚀处理后的晶圆的剖面结构示意图,这里,可以采用等离子刻蚀工艺去除所述衬底。

步骤S605、对所述刻蚀处理后的晶圆进行失效分析。

步骤S604和步骤S605的实现过程和实现的功能与上述实施例中步骤S306和步骤S307的实现过程和实现的功能相同。

本申请实施例提供的晶圆的失效分析方法,在对目标测试区域进行保护之前,需要先去除位于阵列晶圆层中的覆膜层,其次,采用聚焦离子束的方式,在每一贯穿触点表面形成金属层,以进行保护处理,得到保护处理后的晶圆;最后,对保护处理后的晶圆中位于阵列晶圆层中的衬底进行刻蚀,并对刻蚀处理后的晶圆进行失效分析,这样,在对晶圆进行刻蚀之前,去除衬底上层的覆盖层,并通过形成金属层的方式对每一贯穿触点的表面进行保护处理,可以避免在刻蚀过程中对目标测试区域内部位于贯穿触点下方的其它结构产生损伤,且节省了制样时间,提高了制样效率。

图8为本申请实施例提供的晶圆的失效分析方法的实现流程示意图,如图8所示,所述方法包括以下步骤:

步骤S801、在所述晶圆的切割通道中,确定出目标测试区域。

这里,所述晶圆包括叠设的驱动晶圆层和阵列晶圆层,所述阵列晶圆层包括位于所述驱动晶圆层之上的堆叠层和位于所述堆叠层背离所述驱动晶圆层一侧的衬底,所述目标测试区域包括贯穿所述阵列晶圆层的贯穿触点以及形成于所述驱动晶圆层内且位于所述贯穿触点下方的测试结构。

步骤S802、通过所述测试贯穿触点向所述测试结构接入电信号并进行电性能分析,以得到电性能分析结果。

如图9所示,为本申请实施例提供的目标测试区域的剖面结构示意图,所述目标测试区域由阵列晶圆层90和驱动晶圆层91键合形成,其中,所述驱动晶圆层91中具有测试结构910,所述阵列晶圆层90中包含贯穿触点,所述贯穿触点包括与所述测试结构接触的测试贯穿触点901和904,所述贯穿触点还包括未与所述测试结构910接触的非测试贯穿触点902和903。所述测试贯穿触点901包括:测试贯穿硅触点9011和测试贯穿阵列触点9012;所述测试贯穿触点904包括:测试贯穿硅触点9041和测试贯穿阵列触点9042。这里,所述测试贯穿阵列触点9012和9042与所述测试结构910连接。

本申请实施例中,所述测试结构910中填充有用于进行电性能测试的金属,这里,所述金属可以是金属铜。

这里,所述电性能分析是对所述测试贯穿触点和所述测试结构进行扎针测试,以检测刻蚀处理前的晶圆的电性能。所述电性能的分析结果是对所述刻蚀处理前的晶圆的电性能的测试结果。

步骤S803、判断所述电性能分析结果表明所述测试贯穿触点和所述测试结构的电性能是否满足预设的条件。

在一些实施例中,所述预设的条件是预先设置的导电性能要求,例如,预设的电流值或电压值。当所述电性能分析结果表明所述测试贯穿触点和所述测试结构的电性能满足预设的条件时,执行步骤S804,当所述电性能分析结果表明所述测试贯穿触点和所述测试结构的电性能不满足预设的条件时,执行步骤S805。

步骤S804、不对刻蚀处理前的晶圆进行失效分析。

在一些实施例中,当所述电性能分析结果表明所述测试贯穿触点和所述测试结构的电性能满足预设的条件时,表明所述刻蚀处理前的晶圆的电性能满足要求,那么,就不需要对所述刻蚀处理前的晶圆进行失效分析。

步骤S805、对所述贯穿触点的表面进行保护处理,得到保护处理后的晶圆。

步骤S806、对所述保护处理后的晶圆中位于所述阵列晶圆层中的所述衬底进行刻蚀,得到刻蚀处理后的晶圆;

步骤S807、采用物理失效分析方法,对所述刻蚀处理后的晶圆进行失效分析。

本申请实施例中,所述物理失效分析方法是一种有损的失效分析方法,包括:化学及手工研磨剥层技术,聚焦离子束定点切割技术、栅氧异常排查技术和针对衬底位错的透射电镜样品制备及观察技术,本申请实施例中,通过物理失效分析方法,可以实现对刻蚀处理后的晶圆进行高效地失效分析。

本申请实施例提供的晶圆的失效分析方法,在对目标测试区域中的贯穿触点进行保护处理之前,对测试贯穿触点和所述测试结构进行扎针测试,判断晶圆的电性能,当电性能分析结果表明所述测试贯穿触点和所述测试结构的电性能不满足预设的条件时,对目标测试区域中的贯穿触点进行保护处理,如此,可以避免在刻蚀过程中对目标测试区域内部位于贯穿触点下方的其它结构产生损伤,且节省了制样时间,提高了制样效率。

本领域内的技术人员应明白,本申请实施例的半导体器件及其形成方法的其他构成以及作用,对于本领域的技术人员而言都是已知的,为了减少冗余,本申请实施例不做赘述。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”“具体示例”或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本申请的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

尽管已经示出和描述了本申请的实施例,本领域的普通技术人员可以理解:在不脱离本申请的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本申请的范围由权利要求及其等同限定。

- 晶圆研磨方法及晶圆失效分析方法

- 一种晶圆的失效分析方法