一种薄膜晶体管阵列基板及其制作方法

文献发布时间:2023-06-19 10:54:12

技术领域

本申请涉及电子设备技术领域,尤其涉及一种薄膜晶体管阵列基板及其制作方法。

背景技术

随着显示技术的发展,显示领域由中小型屏向大屏发展;由液晶显示行业往AMOLED,喷墨打印,MIC LED发展;由硬屏往柔性发展;且有高画质、省电、机身薄及应用范围广等优点,被广泛应用于手机、电视、个人数字助理、数字相机、笔记本电脑、台式计算机等各种消费性电子产品,成为显示装置中的主流。

通常液晶显示面板由彩膜基板、薄膜晶体管基板、夹于彩膜基板与薄膜晶体管基板之间的液晶及密封胶框组成。

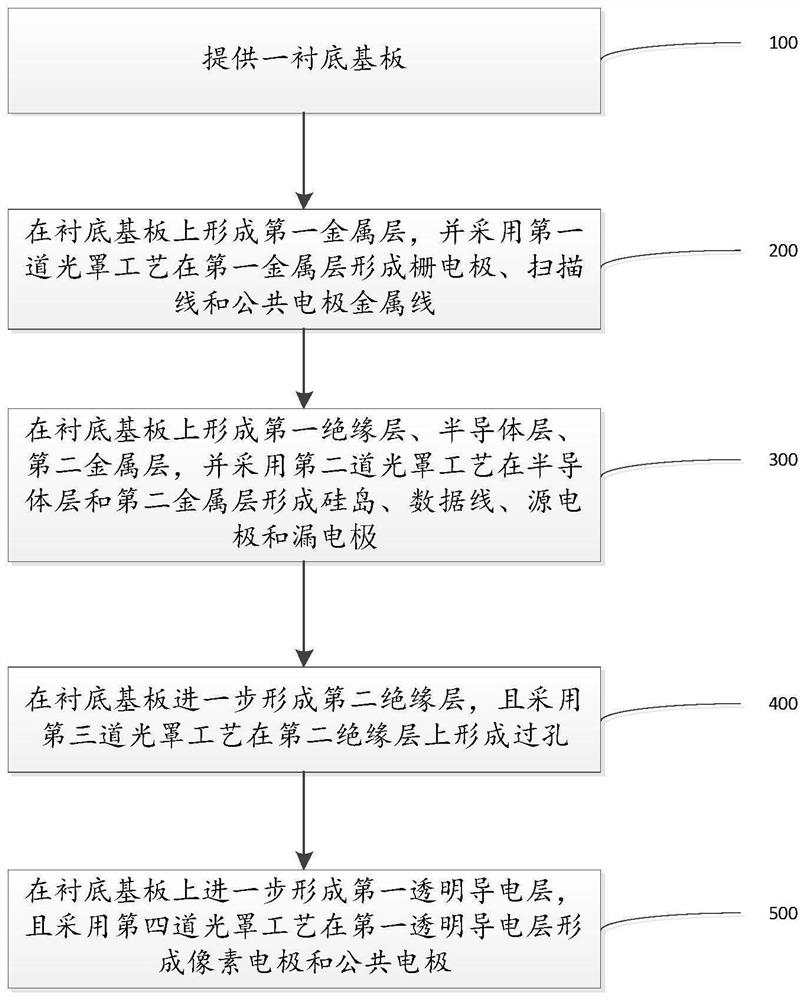

IPS是水平电场型TFT-LCD,需要在薄膜晶体管阵列基板上同时形成像素电极和公共电极。具有响应速度快、可视角度大及色彩真实等优点,广泛应用于液晶显示器领域。但是目前IPS型薄膜晶体管阵列基板的制作方法通常要采用至少6道或5道光罩工艺,参见图1,由于光罩制作成本较高且多道光罩工艺制程时间较长,因此目前IPS型薄膜晶体管阵列基本的制作成本较高。

申请内容

本申请实施例提供一种薄膜晶体管阵列基板的制作方法,所述方法包括:

提供一衬底基板;

在所述衬底基板上形成第一金属层,并采用第一道光罩工艺在所述第一金属层形成栅电极、扫描线和公共电极金属线;

在所述衬底基板上形成第一绝缘层、半导体层、第二金属层,并采用第二道光罩工艺在所述半导体层和第二金属层形成硅岛、数据线、源电极和漏电极,其中,所述硅岛设于所述栅电极上方,所述源电极、所述漏电极分别硅岛两端;

在所述衬底基板进一步形成第二绝缘层,且采用第三道光罩工艺在所述第二绝缘层上形成过孔;其中,所述过孔设置在所述漏电极上方;

在所述衬底基板上进一步形成透明导电层,且采用第四道光罩工艺在所述透明导电层形成像素电极和公共电极,其中,所述像素电极通过所述过孔与漏电极连接,所述公共电极与所述公共电极金属线连接。

可选地,所述采用第一道光罩工艺在所述第一金属层形成栅电极、扫描线和公共电极金属线,包括:

通过第一道光罩工艺的第一光罩,在所述第一金属层上依次进行曝光、显影、湿刻,形成栅电极、扫描线和公共电极金属线;

其中,所述扫描线与所述栅电极连接,所述扫描线不与所述公共电极金属连接。

可选地,所述采用第二道光罩工艺在所述半导体层和第二金属层形成硅岛、数据线、源电极和漏电极,包括:

在所述第二金属层上涂布光刻胶;

通过第二道光罩工艺的第二光罩,在所述第二金属层上依次进行一次曝光、两次蚀刻、灰化处理,两次干刻,形成硅岛、数据线、源电极和漏电极。

可选地,所述第二光罩为半灰阶光罩或半色调掩膜,所述第二光罩包括依次的第一全透区、第一不透区、第一半透区、第二不透区、第二全透区、第三不透区、第三全透区。

可选地,所述采用第四道光罩工艺在所述透明导电层形成像素电极和公共电极,包括:

通过第四道光罩工艺的第四光罩,在所述透明导电层上依次进行曝光、显影、湿刻,形成像素电极和公共电极;

其中,所述像素电极设于公共电极内侧,且所述像素电极不与公共电极连接;所述像素电极、公共电极的设置方式为单畴或多畴。

可选地,所述第一金属层、第二金属层、透明导电层通过物理气相沉积方法沉积形成。

可选地,所述第一金属层、第二金属层至少包括钼、铜、铝、钼铝、钼钛、钼铌中的一种或多种;所述透明导电层至少包括ITO、In2O3、SnO2、ZnO、CdO中一种或多种。

可选地,所述第一绝缘层、第二绝缘层、半导体层通过化学气相沉积方法沉积形成。

可选地,所述第一绝缘层、第二绝缘层为氮化硅或二氧化硅,半导体层为非晶硅。

此外,本申请还公开了一种薄膜晶体管阵列基板,所述薄膜晶体管阵列基板由上述的一种薄膜晶体管阵列基板的制作方法制成,包括:

衬底基板;

形成在所述衬底基板上的栅电极、扫描线、和公共电极金属线;

形成在所述栅电极、扫描线、和公共电极金属线上表面的第一绝缘层;

形成在所述第一绝缘层的源电极、漏电极、数据线;

形成在所述源电极、漏电极、数据线上表面的第二绝缘层;

形成在所述第二绝缘层上的像素电极、公共电极;

其中,所述源电极、漏电极设于所述栅电极上方两端形成三极管三极;所述栅电极与扫描线连接,所述公共电极金属线与所述公共电极连接,所述像素电极通过设于所述第二绝缘层的过孔与漏电极连接,所述源电极与所述数据线连接。

可选地,所述像素电极设于公共电极内侧,且所述像素电极不与公共电极连接。

本申请实施例公开了一种薄膜晶体管阵列基板及其制作方法。其有益效果在于:本申采用4道工艺可以制成IPS型薄膜晶体管阵列基板;通过减少光罩数,实现工艺流程缩短了,提高了生产效率。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是本申请现有技术的制作流程图。

图2是本申请实施例的制作流程图。

图3是本申请实施例衬底基板和第一金属层示意图。

图4是本申请实施例提供的第一道光罩制作的剖视图。

图5是本申请实施例提供的第一道光罩制作的平面图。

图6是本申请实施例提供的沉积第一绝缘层、半导体层、第二金属层的剖视图。

图7是本申请实施例提供第二道光罩曝光的示意图。

图8是本申请实施例提供第二道光罩制作的剖视图。

图9是本申请实施例提供第二道光罩制作的平面图。

图10是本申请实施例提供第三道光罩制作的剖面图。

图11是本申请实施例提供第三道光罩制作的平面图。

图12是本申请实施例提供第四道光罩制作的剖面图。

图13是本申请实施例提供第四道光罩制作的平面图。

具体实施方式

请参照图式,其中相同的组件符号代表相同的组件,本申请的原理是以实施在一适当的运算环境中来举例说明。以下的说明是基于所例示的本申请具体实施例,其不应被视为限制本申请未在此详述的其它具体实施例。

在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本申请的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

在如图2-13所示的实施例中,本申请实施例提供了一种薄膜晶体管阵列基板的制作方法,本方法包括:

100,提供一衬底基板1;在步骤100中,衬底基板1可以是玻璃基板、塑料基板或其他合适材质的基板,在本实施例中,衬底基板1为玻璃基板。

200,在衬底基板1上形成第一金属层2,并采用第一道光罩工艺在第一金属层2形成栅电极21、扫描线23和公共电极金属线22;在步骤200中,先衬底基板1上通过物理气相沉积方法沉积第一金属层2,然后在第一金属层2上,通过第一道光罩工艺的第一光罩,在第一金属层2上依次进行曝光、显影、湿刻,形成栅电极21、扫描线23和公共电极金属线22;其中,扫描线23与栅电极21连接,扫描线23不与公共电极金属连接。

300,在衬底基板1上形成第一绝缘层3、半导体层4、第二金属层5,并采用第二道光罩工艺在半导体层4和第二金属层5形成硅岛、数据线51、源电极53和漏电极52,其中,硅岛设于栅电极21上方,源电极、漏电极分别硅岛两端;在步骤300中,在步骤200后,在衬底基板1上依次通过化学气相沉积方法进一步形成第一绝缘层3、半导体层4、通过物理气相沉积方法沉积第二金属层5;然后在第二金属层5上涂布光刻胶;在半导体层4和第二金属层5上通过第二道光罩工艺的第二光罩7,在第二金属层5上依次进行一次曝光、两次蚀刻、灰化处理,两次干刻,形成硅岛、数据线51、源电极53和漏电极52。

400,在衬底基板1进一步形成第二绝缘层8,且采用第三道光罩工艺在第二绝缘层8上形成过孔;在步骤400中,在步骤300后,在衬底基板1上通过化学气相沉积方法进一步形成第二绝缘层8,通过第三道光罩工艺在第二绝缘层8形成过孔,其中,过孔设置在漏电极上方。第二绝缘层8可以采用氮化硅或二氧化硅。第三道光罩工艺采用的第三光罩可以是普通光罩,仅需在第二绝缘层,且在漏电极上方通过第三光罩的全透区进行曝光,形成连接漏电极和透明导电层的过孔即可。

500,在衬底基板1上进一步形成透明导电层,且采用第四道光罩工艺在透明导电层9形成像素电极91和公共电极92,其中,像素电极91通过过孔与漏电极连接,公共电极92与公共电极金属线22连接。在步骤500中,在步骤400后,在衬底基板1上通过物理气相沉积方法沉积透明导电层9,然后在所述透明导电层9上通过第四道光罩工艺的第四光罩,在透明导电层9上依次进行曝光、显影、湿刻,形成像素电极91和公共电极92;

本申采用4道工艺可以制成IPS型薄膜晶体管阵列基板;通过减少光罩数,实现工艺流程缩短了,提高了生产效率。本申请的薄膜晶体管阵列基板的公共电极92和像素电极91设置在同一层,即透明导电层9;相较于公共电极92和像素电极91分两透明导电层9设置的基板,本申请的排布方式,不仅简化了生产工艺,同时,通过减少透明导电层9,减少了基板的层数结构和厚度,不仅节省原材料且提升了基板的轻薄特性。且在本实施例中,本薄膜晶体管阵列基板电容由公共电极金属线22和三极管的漏极形成;进一步提升基板性能。

在一些实施例中,参见图3-5所示,图3为在衬底基板1上沉积第一金属层2,图4-5为采用第一道光罩工艺在第一金属层2形成栅电极21、扫描线23和公共电极金属线22,包括:通过第一道光罩工艺的第一光罩,在第一金属层2上依次进行曝光、显影、湿刻,形成栅电极21、扫描线23和公共电极金属线22;其中,扫描线23与栅电极21连接,扫描线23不与公共电极92金属连接。在本实施例中,第一金属层2通过物理气相沉积方法沉积形成,且第一金属层2至少包括钼、铜、铝、钼铝、钼钛、钼铌中的一种或多种,在本申请中,第一金属层2的材料不限,采用导电的单金属或金属合金运用本申请的方法解决减少光罩数的问题的技术方案均落入本申请的保护范围内。第一光罩为具有不透光区域和透光区域的常规光罩,以节省光罩成本。通过第一道光罩工艺在第一金属层2上依次进行曝光、显影、湿刻,形成栅电极21、扫描线23和公共电极金属线22的图案。其中,第一绝缘层3可以采用氮化硅或二氧化硅。

在一些实施例中,参见图6-9所示,图6为在衬底基板1上依次通过化学气相沉积方法进一步形成第一绝缘层3、半导体层4,通过物理气相沉积方法沉积第二金属层5,所得的结构,图7为采用第二光罩7进行曝光示意图,图8-9为采用第二道光罩工艺在半导体层4和第二金属层5形成硅岛、数据线51、源电极53和漏电极52,包括:在第二金属层5上涂布光刻胶;通过第二道光罩工艺的第二光罩7,在第二金属层5上依次进行一次曝光、两次蚀刻、灰化处理,两次干刻,形成硅岛、数据线51、源电极53和漏电极52。其中,第一绝缘层3可以采用氮化硅或二氧化硅。

在上述实施例的一种实施方式中,参见图7,第二光罩7为半灰阶光罩或半色调掩膜,第二光罩7包括依次的第一全透区71、第一不透区72、第一半透区73、第二不透区74、第二全透区75、第三不透区76、第三全透区77。其中,全透区透过率100%、不透区透过率0,半透区透过率0~100%。本申请通过第一全透区71、第一不透区72、第一半透区73、第二不透区74、第二全透区75、第三不透区76、第三全透区77依次形成硅岛、数据线51、源电极53和漏电极52的形状。

在一些实施例中,参见图12-13所示,采用第四道光罩工艺在透明导电层9形成像素电极91和公共电极92,包括:通过第四道光罩工艺的第四光罩,在透明导电层9上依次进行曝光、显影、湿刻,形成像素电极91和公共电极92;其中,像素电极91设于公共电极92内侧,且像素电极91不与公共电极92连接。在本实施例中,先在完成步骤400后的衬底基板1上,通过物理气相沉积法沉积透明导电层9;其中,透明导电层9可以是ITO层,透明导电层9通过过孔与漏电极连接。然后通过第四道光罩工艺在透明导电层9进行曝光、显影、湿刻;生成像素电极91和公共电极92,像素电极91设于公共电极92内侧,且像素电极91不与公共电极92连接;公共电极92与公共电极金属连接。其中,透明导电层9至少包括ITO、In2O3、SnO2、ZnO、CdO中一种或多种,在本实施例中,透明导电层9为ITO层。第四道光罩工艺的第四光罩可采用只具有全透区和半透区的普通光罩即可将透明导电层划分成像素电极和公共电极两个区域。在本申请中,像素电极、公共电极的设置方式可以是单畴、双畴、或多畴,本申请技术方案不限于像素电极、公共电极设置方式,像素电极、公共电极的单畴、双畴、或多畴采用本申请的技术方案,均落入本申请保护范围内。

在一些实施例中,本申请的通过第一道光罩工艺、第二道光罩工艺、第三道光罩工艺、第四道光罩工艺制成IPS型薄膜晶体管阵列基板;其中,第一光罩、第三光罩、第四光罩仅需具有全透区和不透区的普通光罩进行制作即可,不仅降低了光罩成本,且降低了制作难度,降低生产成本。其中,第二光罩为具有第一全透区71、第一不透区72、第一半透区73、第二不透区74、第二全透区75、第三不透区76、第三全透区77的半灰阶光罩或半色调掩膜;进一步实现在同一道光罩工艺中形成硅岛、数据线51、源电极53和漏电极52;实现用较少的光罩数量,缩短了生产工艺流程,缩短生产节拍,提高了生产效率,在一定的时间内,加大了产能。

此外,本申请还公开了一种薄膜晶体管阵列基板,薄膜晶体管阵列基板由上述的一种薄膜晶体管阵列基板的制作方法制成,包括:衬底基板1;形成在衬底基板1上的栅电极21、扫描线23、和公共电极金属线22;形成在栅电极21、扫描线23、和公共电极金属线22上表面的第一绝缘层3;形成在第一绝缘层3的源电极、漏电极、数据线51;形成在源电极、漏电极、数据线51上表面的第二绝缘层8;形成在第二绝缘层8上的像素电极91、公共电极;其中,源电极、漏电极设于栅电极21上方两端形成三极管三极;栅电极21与扫描线23连接,公共电极金属线22与公共电极连接,像素电极91通过设于第二绝缘层8的过孔与漏电极连接,源电极与数据线51连接;像素电极91设于公共电极内侧,且像素电极91不与公共电极连接。在本实施例中,本申请的一种薄膜晶体管阵列基板的公共电极和像素电极91设置在同一层,即透明导电层9;相较于公共电极和像素电极91分两透明导电层9设置的基板,本申请的排布方式,不仅简化了生产工艺,同时,通过减少透明导电层9,减少了基板的层数结构和厚度,不仅节省原材料且提升了基板的轻薄特性。且在本实施例中,本薄膜晶体管阵列基板电容由公共电极金属线22和三极管的漏极形成;进一步提升基板性能。

在描述本申请的概念的过程中使用了术语“一”和“”以及类似的词语(尤其是在所附的权利要求书中),应该将这些术语解释为既涵盖单数又涵盖复数。此外,除非本文中另有说明,否则在本文中叙述数值范围时仅仅是通过快捷方法来指代属于相关范围的每个独立的值,而每个独立的值都并入本说明书中,就像这些值在本文中单独进行了陈述一样。另外,除非本文中另有指明或上下文有明确的相反提示,否则本文中所述的所有方法的步骤都可以按任何适当次序加以执行。本申请的改变并不限于描述的步骤顺序。除非另外主张,否则使用本文中所提供的任何以及所有实例或示例性语言(例如,“例如”)都仅仅为了更好地说明本申请的概念,而并非对本申请的概念的范围加以限制。在不脱离精神和范围的情况下,所属领域的技术人员将易于明白多种修改和适应。

以上对本申请实施例所提供的电子设备控制方法、装置、存储介质及电子设备进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的方法及其核心思想;同时,对于本领域的技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

- 薄膜晶体管阵列基板的制作方法及薄膜晶体管阵列基板

- 薄膜晶体管阵列基板及薄膜晶体管阵列基板的制作方法