同步控制电路及具备同步控制电路的不间断电源装置

文献发布时间:2023-06-19 11:55:48

技术领域

本发明涉及同步控制电路及具备同步控制电路的不间断电源装置,特别涉及生成与三相交流信号同相位的相位信息的同步控制电路和具备同步控制电路的不间断电源装置。

背景技术

例如在日本特开平11-089217号公报(专利文献1)及日本特开2007-274766号公报(专利文献2)中公开了同步控制电路,具备:时钟产生部,生成可变频率的时钟信号;相位产生部,响应时钟信号的各脉冲,使相位信息各提前规定角度;坐标转换部,响应时钟信号的各脉冲,以相位信息为基准,将三相交流信号转换为旋转坐标上的向量;以及控制部,以使向量与旋转坐标的基准轴之间的相位差消失的方式控制时钟信号的频率。

现有技术文献

专利文献

专利文献1:日本特开平11-089217号公报

专利文献2:日本特开2007-274766号公报

发明内容

发明要解决的课题

但是,在专利文献1、2中,由于在向量成为提前相位的情况下使时钟信号的频率上升,在向量成为滞后相位的情况下使时钟信号的频率下降,所以时钟信号的频率上下变动,存在不能使相位信息迅速地与三相交流信号同步的问题。

所以,本发明的主要的目的是提供一种能够使相位信息迅速地与三相交流信号同步的同步控制电路和具备同步控制电路的不间断电源装置。

用来解决课题的手段

有关本发明的同步控制电路,是生成与三相交流信号同相位的相位信息的同步控制电路,具有时钟产生部、相位产生部、坐标转换部、运算部、相位校正部和控制部。时钟产生部生成可变频率的时钟信号。相位产生部响应时钟信号的各脉冲,使相位信息各提前预先设定的角度。坐标转换部响应时钟信号的各脉冲,以相位信息为基准,将三相交流信号转换为旋转坐标上的向量。运算部求出向量与旋转坐标的基准轴之间的第1相位差。相位校正部将第1相位差校正,生成第2相位差。控制部以使第2相位差消失的方式控制时钟信号的频率。相位校正部在第1相位差的大小比预先设定的值大的情况下,将第1相位差保持原状设为第2相位差,在第1相位差的大小比预先设定的值小的情况下,生成与第1相位差极性相反的上述第2相位差。

发明效果

有关本发明的同步控制电路,求出向量与旋转坐标的基准轴之间的第1相位差,在第1相位差的大小比规定值大的情况下,将第1相位差保持原状设为第2相位差,在第1相位差的大小比规定值小的情况下生成与第1相位差极性相反的第2相位差,以使第2相位差消失的方式控制时钟信号的频率。因而,能够防止时钟信号的频率上下变动,能够迅速地使相位信息与三相交流信号同步。

附图说明

图1是表示实施方式的不间断电源装置的结构的电路框图。

图2是表示图1所示的控制装置的主要部分的框图。

图3是表示图2所示的比率乘法器的输入输出特性的图。

图4是表示图2所示的时钟产生部的动作的时序图。

图5是表示由图2所示的时钟产生部等构成的同步控制电路的框图。

图6是用来说明图5所示的坐标转换部的动作的图。

图7是用来说明图5所示的判定部的动作的图。

图8是用来说明图5所示的相位校正部的动作的图。

图9是用来说明图5所示的相位校正部的动作的另一图。

图10是表示图5所示的相位校正部的动作的一部分的流程图。

图11是表示图5所示的相位校正部的动作的其他部分的流程图。

图12是表示图10所示的条件[1]的图。

图13是表示图11所示的条件[4]的图。

图14是表示图5所示的同步控制电路的动作的流程图。

图15是表示图2所示的控制装置中的与高速开关及双向转换器的控制相关联的部分的结构的框图。

具体实施方式

图1是表示本发明的一个实施方式的不间断电源装置的结构的电路框图。该不间断电源装置将从商用交流电源5或双向转换器3供给的三相交流电压向负载6供给,但为了附图及说明的简略化,在图1中仅表示了与一相相关联的部分。该不间断电源装置也称作瞬时电压补偿装置。

在图1中,该不间断电源装置具备输入端子T1、输出端子T2、电池端子T3、断路器B1~B4、高速开关(HSS;High Speed Switch)1、变压器2、双向转换器3及控制装置4。

输入端子T1接收从商用交流电源5供给的商用频率的交流电压VI。交流电压VI的瞬时值由控制装置4检测。输出端子T2与负载6连接。负载6通过从不间断电源装置供给的交流电压驱动。电池端子T3与电池7(电力贮存装置)连接。电池7积蓄直流电力。也可以代替电池7而连接电容器。电池7的端子间电压VB由控制装置4检测。

断路器B1连接在输入端子T1与输出端子T2之间。在使用不间断电源装置的情况下,断路器B1断开。在不间断电源装置的维护时,断路器B1接通,来自商用交流电源5的交流电压VI经由断路器B1向负载6供给。

断路器B2连接在输入端子T1与高速开关1的一个端子1a之间。断路器B3连接在高速开关1的另一个端子1b与输出端子T2之间。在使用不间断电源装置的情况下,断路器B2、B3接通。在不间断电源装置维护时,断路器B2、B3断开。

高速开关1例如由半导体开关元件构成,由控制装置4控制。在商用交流电源5正常工作时,高速开关1接通,来自商用交流电源5的交流电压VI经由断路器B2、高速开关1及断路器B3向负载6供给。在商用交流电源5停电时,高速开关1断开,商用交流电源5和负载6电气地切断。在高速开关1的另一个端子1b表现出的交流电压VO的瞬时值由控制装置4检测。

断路器B4连接在高速开关1的另一个端子1b与变压器2的一次绕组2a之间。在使用不间断电源装置的情况下,断路器B4接通。在不间断电源装置维护时,断路器B4断开。变压器2的二次绕组2b与双向转换器3的交流端子3a连接。变压器2在高速开关1的另一个端子1b与双向转换器3之间交换交流电力。

双向转换器3的直流端子3b与电池端子T3连接。双向转换器3由控制装置4控制。在商用交流电源5正常工作时,双向转换器3将从商用交流电源5经由断路器B2、高速开关1、断路器B4及变压器2供给的交流电力转换为直流电力,向电池7积蓄。在商用交流电源5停电时,双向转换器3将电池7的直流电力转换为商用频率的交流电力,经由变压器2及断路器B4、B3向负载6供给。

控制装置4基于交流电压VI、VO及电池电压VB,对高速开关1及双向转换器3进行控制。即,控制装置4在交流电压VI比下限值高的情况下,判定为商用交流电源5正常工作,在交流电压VI比下限值低的情况下,判定为商用交流电源5发生了停电。

此外,控制装置4在商用交流电源5正常工作时,使高速开关1接通,并且与交流电压VI同步地控制双向转换器3以使电池电压VB成为参照电压VBr。如果电池电压VB成为参照电压VBr,则控制装置4控制双向转换器3,使电池电压VB转换为商用频率的交流电压VAC。交流电压VAC是在双向转换器3的交流端子3a表现出的电压。

如果使双向转换器3的交流输出电压VAC的相位比来自商用交流电源5的交流电压VI的相位提前,则电力从电池7经由双向转换器3向负载6流动,电池电压VB下降。如果使交流输出电压VAC的相位比交流电压VI的相位滞后,则电流从商用交流电源5经由双向转换器3向电池7流动,电池电压VB上升。控制装置4控制双向转换器3而对交流电压VAC的相位进行调整,将电池电压VB维持为参照电压VBr。

此外,控制装置4在商用交流电源5停电时,使高速开关1断开,以使交流电压VO成为参照电压VOr的方式控制双向转换器3。在商用交流电源5已从停电状态恢复为正常工作状态的情况下,控制装置4控制双向转换器3使交流电压VO的相位及频率与交流电压VI的相位及频率一致后,使高速开关1接通。

接着,对该不间断电源装置的动作进行说明。在使用不间断电源装置的情况下,断路器B1断开,断路器B2~B4接通。在商用交流电源5正常工作时,高速开关1接通,来自商用交流电源5的交流电力经由高速开关1向负载6供给,使负载6运转。

此外,来自商用交流电源5的交流电力经由高速开关1及变压器2向双向转换器3供给,转换为直流电力而积蓄到电池7中。如果电池电压VB成为参照电压VBr,则双向转换器3的交流输出电压VAC的相位受到控制,电池电压VB维持为参照电压VBr,双向转换器3成为待机状态。

如果商用交流电源5发生停电,则高速开关1断开,从待机状态的双向转换器3经由变压器2向负载6供给交流电力。因而,只要在电池7中积蓄有直流电力,就能够继续负载6的运转。

在商用交流电源5已从停电状态恢复为正常工作状态的情况下,控制装置4在控制双向转换器3使交流电压VO的相位及频率与交流电压VI的相位及频率一致后,使高速开关1接通。由此,能够防止交流电压VO变动而负载6的动作变得不稳定。

此外,在进行不间断电源装置的维护的情况下,断路器B1接通,断路器B2~B4断开,从商用交流电源5经由断路器B1向负载6供给交流电力,使负载6运转。能够将高速开关1等从商用交流电源5电气地切断,一边使负载6运转一边进行高速开关1等的维护。

图2是表示图1所示的控制装置4的主要部分的框图。在图2中,控制装置4包括电压检测器11~13、A/D(Analog-to-Digital)转换器14~16、数据总线17、存储器18、振荡器19、比率乘法器20、计数器21、CPU(Central Processing Unit;中央处理单元)23、PWM(Pulse Width Modulation;脉冲宽度调制)电路24及驱动器25。

数据总线17与A/D转换器14~16、存储器18、比率乘法器20、CPU 23、PWM电路24及驱动器25连接,在它们之间进行信息的交换。

电压检测器11检测从商用交流电源5供给的三相交流电压VIu、VIv、VIw的瞬时值,输出表示其检测值的三相交流信号。A/D转换器14将从电压检测器11输出的三相交流信号转换为数字信号,经由数据总线17提供给CPU 23。

电压检测器12检测从不间断电源装置向负载6供给的三相交流电压VOu、VOv、VOw的瞬时值,输出表示其检测值的三相交流信号。A/D转换器15将从电压检测器12输出的三相交流信号转换为数字信号,经由数据总线17提供给CPU 23。

电压检测器13检测电池电压VB,输出表示其检测值的直流信号。A/D转换器16将从电压检测器13输出的直流信号转换为数字信号,经由数据总线17提供给CPU 23。存储器18与数据总线17连接,存储各种信息及程序。

振荡器19生成基准频率fa的时钟信号CLK1(第1副时钟信号)。比率乘法器20将时钟信号CLK1分频,生成时钟信号CLK2(第2副时钟信号)。比率乘法器20的分频比通过从CPU23供给的分频指令值n控制。

图3是表示比率乘法器20的输入输出特性的图。在图3中,横轴表示分频指令值n,纵轴表示比率乘法器20的输出时钟信号CLK2的频率fb。分频指令值n设定为上限值N1与下限值N2之间的某个值。n是整数。N1>0>N2。如果n从N2增大到N1,则频率fb与n成正比例而增大。

当n是N2时,频率fb为最小值F2,当n是N1时,频率fb为最大值F1。当n=0时,频率fb为F0。频率F0称作固有频率,设定为从商用交流电源5供给的三相交流电压VIu、VIv、VIw的额定频率。

回到图2,计数器21是升降计数器,对比率乘法器20的输出时钟信号CLK2的脉冲进行计数,基于计数结果输出时钟信号CLK3。计数器21的计数值与时钟信号CLK2同步增大,如果计数值成为最大值,则计数值与时钟信号CLK2同步减小,如果计数值成为最小值,则计数值与时钟信号CLK2同步增大。因而,计数值以三角波状变化。计数器21在计数值成为最大值及最小值时输出脉冲。

计数器21的输出时钟信号CLK3是将比率乘法器20的输出时钟信号CLK2以一定的分频比分频出的信号。振荡器19、比率乘法器20及计数器21构成时钟产生部22,生成可变频率的时钟信号CLK3。

图4是表示时钟产生部22的动作的时序图。在图4中,(A)表示振荡器19的输出时钟信号CLK1的波形,(B)表示比率乘法器20的输出时钟信号CLK2的波形,(C)(D)分别表示计数器21的计数值CV,(E)表示计数器21的输出时钟信号CLK3的波形。(C)是将(D)的时间轴放大的图。

例如在由CPU 23将比率乘法器20的分频比K设定为1/2的情况下,比率乘法器20的输出时钟信号CLK2的频率fb成为振荡器19的输出时钟信号CLK1的频率fa的1/2(fb=fa/2)。计数器21的计数值CV与时钟信号CLK2同步以三角波状变化。计数器21在计数值CV成为最小值及最大值时输出脉冲。从计数器21输出的脉冲列成为计数器21的输出时钟信号CLK3。计数器21的输出时钟信号CLK3的各脉冲作为对CPU 23请求中断处理的中断请求信号使用。

另外,三角波状的计数值CV可以作为PWM电路24的载波信号使用。现在,如果假设三角波载波信号的解析力是8bit(=256),其频率是6kHz,双向转换器3的输出频率是60Hz,则控制双向转换器3的定时为6kHz×2÷60Hz=200次。

此外,比率乘法器20的输出时钟信号CLK2的频率fb为6kHz×2×256=3.072MHz。因而,如果设比率乘法器20的动态范围为2倍,稳态的分频比K为1/2,则振荡器19的输出时钟信号CLK1的频率fa为3.072MHz×2=6.144MHz。这里,在通过数字控制实施双向转换器3的输出电压控制的情况下,需要载波用的计数器、振荡器等,所以实际上仅追加比率乘法器20就能够实现本实施方式的同步控制。

在中断处理每1循环是200次的情况下,CPU 23针对每个中断处理将相位信息θ提前2π/200,求出该相位信息θ与从商用交流电源5供给的三相交流电压VIu、VIv、VIw的相位差dθ,以使该相位差dθ消失的方式控制对于比率乘法器20的分频指令值n。

此外,CPU 23基于相位信息θ生成三相的电压指令值VCu、VCv、VCw,将该电压指令值VCu、VCv、VCw提供给PWM电路24。PWM电路24基于从CPU 23提供的电压指令值VCu、VCv、VCw,对双向转换器3进行PWM控制。

此外,CPU 23基于从A/D转换器14供给的数字信号,判定商用交流电源5是否正常工作。CPU 23在商用交流电源5正常工作时将控制信号CNT设为“H”电平,在商用交流电源5停电时将控制信号CNT设为“L”电平。驱动器25在控制信号CNT是“H”电平的情况下将高速开关1接通,在控制信号CNT是“L”电平的情况下将高速开关1断开。

CPU 23在商用交流电源5从停电状态恢复为正常工作状态的情况下,使相位信息θ与从商用交流电源5供给的三相交流电压VIu、VIv、VIw的相位一致,在使由双向转换器3及变压器2生成的三相交流电压VOu、VOv、VOw的相位及频率与三相交流电压VIu、VIv、VIw的相位及频率一致后,使高速开关1接通。

图2的电压检测器11、A/D转换器14、数据总线17、存储器18、时钟产生部22及CPU23,构成生成与从商用交流电源5供给的三相交流电压VIu、VIv、VIw(三相交流信号)同相位的相位信息θ的同步控制电路30。同步控制电路30基于保存在存储器18中的程序而动作。

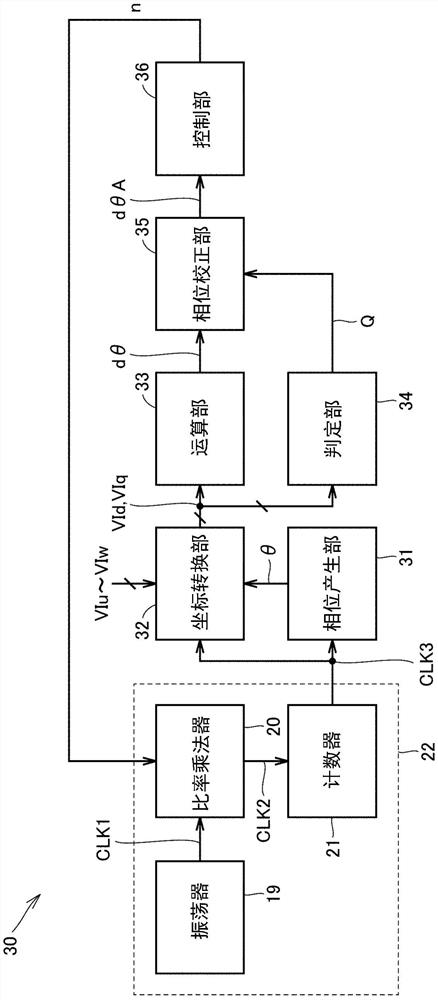

图5是表示同步控制电路30的结构的框图。在图5中,同步控制电路30包括时钟产生部22、相位产生部31、坐标转换部32、运算部33、判定部34、相位校正部35及控制部36。

相位产生部31响应时钟产生部22的输出时钟信号CLK3的各脉冲,将相位信息θ提前规定角度Δθ。例如在每1个循环进行200次中断的情况下,Δθ=2π/200。

相位产生部31包括相位计数器。相位计数器的计数值存储在存储器18中。相位产生部31响应时钟信号CLK3的各脉冲,将相位计数器的计数值增加。例如在每1个循环进行200次中断的情况下,相位计数器是反复从0计数到199的模计数器。相位信息θ是对Δθ乘以相位计数器的计数值C而得到的值(θ=Δθ×C)。

坐标转换部32响应时钟产生部22的输出时钟信号CLK3的各脉冲,采样从商用交流电源5供给的三相交流电压VIu、VIv、VIw,将采样出的三相交流电压VIu、VIv、VIw以相位信息θ为基准,转换为旋转坐标上的向量VE。坐标转换部32的功能由电压检测器11、A/D转换器14、CPU 23及存储器18实现。在存储器18中保存有正弦波的数据表。

即,坐标转换部32响应时钟产生部22的输出时钟信号CLK3的各脉冲,采样从商用交流电源5供给的三相交流电压VIu、VIv、VIw,对采样出的三相交流电压VIu、VIv、VIw进行A/D转换。此外,坐标转换部32使用相位计数器的计数值C,根据正弦波的数据表,读取由下式(1)~(6)表示的sin值及cos值。

sinU=sin(2πC/C0) …(1)

sinV=sin(2πC/C0-2π/3) …(2)

sinW=sin(2πC/C0+2π/3) …(3)

cosU=cos(2πC/C0) …(4)

cosV=cos(2πC/C0-2π/3) …(5)

cosW=cos(2πC/C0+2π/3) …(6)

这里,C0是每1个循环的中断数,例如是200。此外,2πC/C0是相位信息θ。

接着,坐标转换部32基于上述数据信号DIu、DIv、DIw及下式(7),将三相交流电压VIu、VIv、VIw转换为旋转坐标上的向量VE。

[数式1]

在三相交流电压VIu、VIv、VIw的频率fv与相位计数器的频率fc相等、并且三相交流电压VIu、VIv、VIw的相位比相位信息θ提前了dθ的情况下,下式(8)~(10)成立。

VIu=VI1·sin(2πfv+dθ) ...(8)

VIv=VI1·sin(2πfv-2π/3+dθ) ...(9)

VIw=VI1·sin(2πfv+2π/3+dθ) ...(10)

在此情况下,向量VE的d轴成分VId及q轴成分VIq由下式(11)(12)表示。

VId=(3/2)

VIq=(3/2)

图6是表示旋转坐标上的向量VE的图。在图6中,旋转坐标具有d轴及q轴。向量VE由以原点为起点的箭头表示。向量VE的长度是(3/2)

运算部33基于向量VE的d轴成分VId及q轴成分VIq,求出向量VE与旋转坐标的d轴(基准轴)之间的相位差dθ。运算部33基于下式(13),求出相位差dθ。

dθ=sin

判定部34基于向量VE的d轴成分VId及q轴成分VIq,判定向量位于旋转坐标的第1副象限Q1~第8副象限Q8中的哪个副象限Q。

图7是表示设定于旋转坐标的第1副象限Q1~第8副象限Q8的图。在图7中,旋转坐标中的0~π/2的区域设为第I象限,π/2~π的区域设为第II象限,0~(-π/2)的区域设为第III象限,(-π/2)~(-π)的区域设为第IV象限。

此外,第I象限在左旋转方向上被等分为第1副象限Q1、第2副象限Q2及第3副象限Q3,将第II象限设为第4副象限Q4,将第III象限设为第5副象限Q5,第IV象限在左旋转方向上被等分为第6副象限Q6、第7副象限Q7及第8副象限Q8。

换言之,将旋转坐标中的0~π/6的区域设为第1副象限Q1,π/6~π/3的区域设为第2副象限Q2,π/3~π/2的区域设为第3副象限Q3,π/2~π的区域设为第4副象限Q4。此外,将0~(-π/6)的区域设为第8副象限Q8,(-π/6)~(-π/3)的区域设为第7副象限Q7,(-π/3)~(-π/2)的区域设为第6副象限Q6,(-π/2)~(-π)的区域设为第5副象限Q5。

例如,判定部34基于向量VE的d轴成分VId及q轴成分VIq的比及各自的极性,判定向量VE位于第1副象限Q1~第8副象限Q8中的哪个副象限Q。

例如,在VId及VIq的比是1.0、VId及VIq的极性都为正的情况下,向量VE存在于第2副象限Q2。此外,在VId及VIq的比是-1.0、VId及VIq的极性分别是正及负的情况下,向量VE存在于第7副象限Q7。

相位校正部35基于判定部34的判定结果,校正由运算部33求出的相位差dθ而生成相位差dθA。这里,对校正相位差dθ的理由进行说明。在图8中,表示了处于第I象限的向量VE1和处于第II象限的向量VE2。设向量VE1与d轴之间的相位差为dθ1,设向量VE2与d轴之间的相位差为dθ2。dθ1是0~π/2,dθ2是π/2~π。

这里,如果运算部33基于上式(13)求出向量VE1、VE2的相位差dθ,则虽然第I象限的向量VE1的相位差dθ1能正确地求出,但第II象限的向量VE2的相位差dθ2不能正确地求出,向量VE2的相位差作为(π-dθ2)求出。因而,如果在第II象限中使向量VE的相位差dθ逐渐增大,则由运算部33得到的dθ的计算值逐渐减小,如果将向量VE的相位差dθ设为π,则由运算部33得到的dθ的计算值为0度。

在同步控制电路30,由于以使向量VE的相位差dθ成为0度的方式控制对于比率乘法器20的分频指令值n,所以如果不将dθ校正,则不仅在dθ=0的情况、在dθ=π的情况下同步控制动作也锁定。所以,相位校正部35在由判定部34判定为向量VE处于第II象限的情况下,将由运算部33求出的相位差dθ校正为正的限制值PLM(例如π/2)。

同样,虽然第IV象限的向量VE的相位差dθ能正确地求出,但第III象限的向量VE的相位差dθ不能正确地求出,作为(-π-dθ)求出。因而,如果在第III象限中使向量VE的相位差dθ向负侧逐渐增大,则由运算部33得到的dθ的运算值向正侧逐渐增大,如果设向量VE的相位差dθ为-π,则由运算部33得到的dθ的计算值为0度。

在同步控制电路30,由于以使向量VE的相位差dθ成为0度的方式控制对于比率乘法器20的分频指令值n,所以如果不将dθ校正,则不仅在dθ=0的情况、在dθ=-π的情况下同步控制动作也锁定。所以,相位校正部35在由判定部34判定为向量VE处于第III象限的情况下,将由运算部33求出的相位差dθ校正为负的限制值NLM(例如-π/2)。

此外,如图9所示,在向量VE处于第II象限的情况下,不知道向量VE是以d轴为基准提前了相位差dθ1还是滞后了相位差dθ2。如果对于向量VE是提前相位还是滞后相位进行了误检测,则后级的控制部36会使向量VE与相位信息θ的相位差dθ扩大。

所以,在本实施方式中,对响应此次的脉冲(中断请求信号)而生成的向量VEn所处的副象限Qn与响应上次的脉冲(中断请求信号)而生成的向量VEp所处的副象限Qp进行比较,基于比较结果判定此次的向量VEn是提前相位还是滞后相位,基于判定结果校正相位差θ。

此外,在本实施方式中,为了迅速地判定向量VE是提前相位还是滞后相位,将第I象限划分为第1副象限Q1~第3副象限Q3,将第IV象限划分为第6副象限Q6~第8副象限Q8。

进而,在本实施方式中,为了使向量VE的相位差dθ迅速地收敛为0,在相位差dθ的大小成为规定值(例如π/2)以下的情况下,通过从此次的向量VEn的相位差dθ减去上次的向量VEp的相位差dθp,从而生成校正后的相位差dθA(dθA=dθ-dθp)。由此,相位差dθ的极性逆转,并且相位差dθ的大小减小。

图10是表示相位校正部35的动作的一部分的流程图,图11是表示相位校正部35的动作的其他部分的流程图。在图10的步骤ST1中,相位校正部35从判定部34读取响应此次的脉冲(中断请求信号)而生成的向量VEn所处的副象限Qn。

在步骤ST2中,相位校正部35判定存储在存储器18的相位差标志Fp是否是“H”电平。在响应上次的脉冲(中断请求信号)而生成的向量VEp是提前相位的情况下,相位差标志Fp成为“H”电平(Fp=H)。在上次的向量VEp是滞后相位的情况下,相位差标志Fp成为“L”电平(Fp=L)。

在步骤ST2中相位差标志Fp是“H”电平的情况下,在步骤ST3中,相位校正部35判定此次的向量VEn所处的副象限Qn和存储在存储器18的上次的向量VEp所处的副象限Qp是否满足图12的条件[1]。

满足条件[1]的情况有3个。第1情况是此次的向量VEn位于第6副象限Q6,上次的向量VEp位于第7副象限Q7、第8副象限Q8、第1副象限Q1、第2副象限Q2或第3副象限Q3的情况。第2情况是此次的向量VEn位于第7副象限Q7,上次的向量VEp位于第8副象限Q8、第1副象限Q1、第2副象限Q2或第3副象限Q3的情况。第3情况是此次的向量VEn位于第8副象限Q8,上次的向量VEp位于第1副象限Q1、第2副象限Q2或第3副象限Q3的情况。

即,满足条件[1]的情况是此次的向量VEn位于副象限Q6~Q8中的某个副象限Qn,上次的向量VEp位于副象限Q7、Q8、Q1~Q3中的比副象限Qn靠近左旋转侧的副象限Qp的情况。

在步骤ST3中判定为满足条件[1]的情况下,相位校正部35判定为向量VE向右进行了旋转,即此次的向量VEn相位滞后,在步骤ST4中,将相位差标志Fp设置为“L”电平,在步骤ST5中将此次的相位差dθ保持原状设为校正后的相位差dθA(dθA=dθ),向步骤ST19前进。

在步骤ST3中判定为不满足条件[1]的情况下,相位校正部35判定为此次的向量VEn相位提前,在步骤ST6中判定是否满足条件[2]。满足条件[2]的情况是此次的向量VEn位于副象限Q1~Q3、Q6~Q8中的某个副象限Qn的情况。换言之,满足条件[2]的情况是此次的向量VEn位于第I象限或第IV象限的情况。

在步骤ST6中判定为满足条件[2]的情况下,在步骤ST7中,相位校正部35判定是否满足条件[3]。满足条件[3]的情况是此次的向量VEn位于副象限Q1~Q3中的某个副象限Qn的情况。换言之,满足条件[3]的情况是此次的向量VEn位于第I象限的情况,是相位差dθ的大小比规定值(π/2)小的情况。

在步骤ST7中判定为满足条件[3]的情况下,相位校正部35判定为此次的向量VEn的相位差dθ正在接近0度,在步骤ST8中,将此次的向量VEn的相位差dθ与上次的向量VEp的相位差dθp的差(dθ-dθp)设为校正后的相位差dθA(dθA=dθ-dθp),向步骤ST19前进。由此,生成与此次的向量VEn的相位差dθ极性相反、小的相位差dθA,相位差dθA迅速地收敛为0度。

在步骤ST7中判定为不满足条件[3]的情况下,在步骤ST9中,相位校正部35将此次的向量VEn的相位差dθ保持原状设为校正后的相位差dθA(dθA=dθ),向步骤ST19前进。

在步骤ST6中判定为不满足条件[2]的情况下,相位校正部35判定为此次的向量VEn位于第4副象限Q4(即第II象限),在步骤ST10中,将此次的向量VEn的相位差dθ校正为正的限制值PLM(dθA=PLM),向步骤ST19前进。

在步骤ST2中,在相位差标志Fp不是“H”电平的情况下,在图11的步骤ST11中,相位校正部35判定此次的向量VEn所处的副象限Qn和存储在存储器18的上次的向量VEp所处的副象限Qp是否满足图13的条件[4]。

满足条件[4]的情况有3个。第1情况是此次的向量VEn位于第3副象限Q3,上次的向量VEp位于第2副象限Q2、第1副象限Q1、第8副象限Q8、第7副象限Q7或第6副象限Q6的情况。第2情况是此次的向量VEn位于第2副象限Q2,上次的向量VEp位于第1副象限Q1、第8副象限Q8、第7副象限Q7或第6副象限Q6的情况。第3情况是此次的向量VEn位于第1副象限Q1,上次的向量VEp位于第8副象限Q8、第7副象限Q7或第6副象限Q6的情况。

即,满足条件[4]的情况是此次的向量VEn位于副象限Q1~Q3中的某个副象限Qn,上次的向量VEp位于副象限Q6~Q8、Q1、Q2中的比副象限Qn靠近右旋转侧的副象限Qp的情况。

在步骤ST11中判定为满足条件[4]的情况下,相位校正部35判定为向量VE向左进行了旋转,即此次的向量VEn相位提前,在步骤ST12中将相位差标志Fp设置为“H”电平,在步骤ST13中将此次的相位差dθ保持原状设为校正后的相位差dθA(dθA=dθ),向步骤ST19前进。

在步骤ST11中判定为不满足条件[4]的情况下,判定为此次的向量VEn相位滞后,在步骤ST14中,相位校正部35判定是否满足条件[5]。满足条件[5]的情况是此次的向量VEn位于副象限Q1~Q3、Q6~Q8中的某个副象限Qn的情况。换言之,满足条件[5]的情况是此次的向量VEn位于第I象限或第IV象限的情况。

在步骤ST14中判定为满足条件[5]的情况下,在步骤ST15中,相位校正部35判定是否满足条件[6]。满足条件[6]的情况是此次的向量VEn位于副象限Q6~Q8中的某个副象限Qn的情况。换言之,满足条件[6]的情况是此次的向量VEn位于第IV象限的情况,是相位差dθ的大小比规定值(π/2)小的情况。

在步骤ST15中判定为满足条件[6]的情况下,判定为此次的向量VEn的相位差dθ正在接近0度,在步骤ST16中,相位校正部35将此次的向量VEn的相位差dθ与上次的向量VEp的相位差dθp的差(dθ-dθp)设为校正后的相位差dθA(dθA=dθ-dθp),向步骤ST19前进。由此,生成与此次的向量VEn的相位差dθ极性相反且小的相位差dθA,相位差dθA迅速地收敛为0度。

在步骤ST15中判定为不满足条件[6]的情况下,在步骤ST17中,相位校正部35将此次的向量VEn的相位差dθ保持原状设为校正后的相位差dθA(dθA=dθ),向步骤ST19前进。

在步骤ST14中判定为不满足条件[5]的情况下,判定为此次的向量VEn位于第5副象限Q5(即第III象限),在步骤ST18中,相位校正部35将此次的向量VEn的相位差dθ校正为负的限制值NLM(dθA=NLM),向步骤ST19前进。

在步骤ST19中,相位校正部35将此次的向量VEn所处的副象限Qn设为上次的向量VEp所处的副象限Qp而向存储器18存储,并且将此次的向量VEn的相位差dθ作为上次的向量VEp的相位差dθp向存储器18存储。由此,与1个中断请求信号对应的相位校正处理结束。

回到图5,控制部36以使校正后的相位差dθA成为0度的方式生成分频指令值n而对比率乘法器20的分频比进行控制,对时钟产生部22的输出时钟信号CLK3的频率fc进行控制。

即,控制部36按照下式(14),对校正后的相位差dθA进行PI(ProportionalIntegral,比例积分)运算。

U(S)=Kp(1+Ki/S)×dθA …(14)

这里,U(S)是操作量,Kp是比例增益,Ki是积分增益,S是拉普拉斯算子。

控制部36基于操作量U(S)生成分频指令值n。即,控制部36以使与相位差dθA成正比例的值和与相位差dθA的积分值成正比例的值的和成为0的方式对分频指令值n进行控制。

在相位差dθA是提前相位的情况下,将分频指令值n向正方向调整而比率乘法器20的输出时钟信号CLK2的频率fb增大(图3),计数器21的输出时钟信号CLK3的频率fc增大。由此,中断周期变短,程序的相位计数器快速地增加计数,稳态下相位信息θ的相位与从商用交流电源5供给的三相交流电压VIu、VIv、VIw的相位一致。

相反,在相位差dθA是滞后相位的情况下,将分频指令值n向负方向调整而比率乘法器20的输出时钟信号CLK2的频率fb减小(图3),计数器21的输出时钟信号CLK3的频率fc减小。由此,中断周期变长,程序的相位计数器缓慢地增加计数,稳态下相位信息θ的相位与从商用交流电源5供给的三相交流电压VIu、VIv、VIw的相位一致。

图14是表示图5~图13所示的同步控制电路30的动作的流程图。在图14的步骤ST21中,坐标转换部32将从商用交流电源5供给的三相交流电压VIu、VIv、VIw转换为数字信号。在步骤ST22中,相位产生部31将相位计数器的计数值C增加,生成相位信息θ=2πC/C0。

在步骤ST23中,坐标转换部32使用相位信息θ,从正弦波的数据表读取由数式(1)~(6)表示的sin值及cos值。在步骤ST24中,坐标转换部32对转换为数字信号的三相交流电压VIu、VIv、VIw基于数式(7)进行dq转换,求出d轴成分VId及q轴成分VIq。由此,三相交流电压VIu、VIv、VIw转换为旋转坐标上的向量VE。

在步骤ST25中,运算部33基于数式(13),求出向量VE与d轴之间的相位差dθ。在步骤ST26中,判定部34判定向量VE位于副象限Q1~Q8中的哪个副象限。在步骤S27中,相位校正部35执行步骤ST1~ST19(图10及图11),校正向量VE的相位差dθ而生成相位差dθA。

在步骤ST28中,控制部36对校正后的相位差dθA实施PI运算而求出操作量U(S),生成分频指令值n提供给比率乘法器20。步骤ST21~ST28响应时钟产生部22的输出时钟信号CLK3的各脉冲(中断请求信号)而执行。

图15是表示控制装置4中的与高速开关1及双向转换器3的控制相关联的部分的结构的框图。在图15中,控制装置4包括停电检测器40及控制部41。停电检测器40由电压检测器11、A/D转换器14及CPU 23(图2)构成。控制部41由电压检测器12、13、A/D转换器15、16及CPU 23(图2)构成。

停电检测器40基于从商用交流电源5供给的三相交流电压VIu、VIv、VIw,检测商用交流电源5是否发生了停电,输出表示检测结果的信号φ40。在商用交流电源5正常工作时,信号φ40设为“H”电平,在商用交流电源5停电时,信号φ40设为“L”电平。

在停电检测信号φ40是“H”电平的情况下,控制部41将控制信号CNT(图2)设为“H”电平而使高速开关1接通,并基于相位信息θ及电池电压VB,生成三相电压指令值VCu、VCv、VCw提供给PWM电路24(图2)。PWM电路24按照三相电压指令值VCu、VCv、VCw,对双向转换器3进行PWM控制。

在电池电压VB比参照电压VBr低的情况下,生成相位比相位信息θ滞后的三相电压指令值VCu、VCv、VCw。由此,电力从商用交流电源5经由高速开关1、变压器2及双向转换器3向电池7流动,电池7充电。

在电池电压VB比参照电压VBr高的情况下,生成相位比相位信息θ提前的三相电压指令值VCu、VCv、VCw。由此,电力从电池7经由双向转换器3及变压器2向负载6流动,电池7放电。

在电池电压VB等于参照电压VBr的情况下,生成与相位信息θ对应的相位的三相电压指令值VCu、VCv、VCw,将双向转换器3设为待机状态。

如果商用交流电源5发生停电而信号φ40从“H”电平降低至“L”电平,则控制部41将控制信号CNT设为“L”电平而使高速开关1断开,并且继续生成停电前最近的相位的三相电压指令值VCu、VCv、VCw。

如果商用交流电源5恢复而信号φ40从“L”电平升高至“H”电平,则控制部41以使新的相位信息θ和由双向转换器3生成的三相交流电压VOu、VOv、VOw相位相同的方式生成三相电压指令值VCu、VCv、VCw。

当新的相位信息θ和三相交流电压VOu、VOv、VOw成为同相位时,控制部41将控制信号CNT设为“H”电平而将高速开关1接通。此时,由于由双向转换器3生成的三相交流电压VOu、VOv、VOw和从商用交流电源5供给的三相交流电压VIu、VIv、VIw是同相位,所以能够将向负载6的电力供给源从双向转换器3顺畅地切换为商用交流电源5。

如以上这样,该实施方式中,求出向量VE与旋转坐标的d轴之间的相位差dθ,在相位差dθ的大小比规定值(例如π/2)大的情况下,将相位差dθ保持原状设为相位差dθA,在相位差dθ的大小比规定值小的情况下,生成与相位差dθ极性相反且小的相位差dθA,以使相位差dθA成为0度的方式控制时钟信号CLK3的频率fc。因而,能够防止时钟信号CLK3的频率fc上下变动,能够使相位信息θ迅速地与三相交流电压VIu、VIv、VIw同步。

此次公开的实施方式在全部的方面都是例示而不应被认为是限制性的。本发明不是由上述的说明、而是由权利要求书表示,意味着包含与权利要求书等价的意义及范围内的全部变更。

标号说明

T1输入端子;T2输出端子;T3电池端子;B1~B4断路器;1高速开关;2变压器;3双向转换器;4控制装置;11~13电压检测器;14~16A/D转换器;17数据总线;18存储器;19振荡器;20比率乘法器;21计数器;22时钟产生部;23CPU;24PWM电路;25驱动器;30同步控制电路;31相位产生部;32坐标转换部;33运算部;34判定部;35相位校正部;36、41控制部;40停电检测器。

- 同步控制电路及具备同步控制电路的不间断电源装置

- 同步整流管的关断控制电路及同步整流控制电路