封装结构以及半导体制造方法

文献发布时间:2024-01-17 01:15:20

技术领域

本发明是有关于一种封装结构以及半导体制造方法,特别是有关于一种将增强型晶体管以及空乏型III-V族晶体管(depletion-mode III-V transistor)共源共栅在一起的封装结构以及整合空乏型III-V族晶体管与二极管的半导体制造方法。

背景技术

III-V族晶体管,例如氮化镓场效应晶体管(GaN FET),由于其高效率的特性以及适合高电压操作,常常使用于高功率和高性能的电路应用。此外,III-V族晶体管往往会与其他晶体管(如,硅场效晶体管)组合而产生高性能的开关装置,例如共源共栅(cascoded)开关。

一般的封装设计可以将离散的器件并排放置于相同的支撑表面上,如放置于引线框架(lead frame)上的覆铜陶瓷基板(Direct Bonding Copper,DBC)或陶瓷基板。然而,仅仅将离散器件并排放置于支撑表面上往往会带来许多不可预期的非理想效应,因此有必要针对不可预期的非理想效应进行排除,以提高开关装置的效能。

发明内容

本发明提出封装结构以及功率晶体管,以有效率且具有成本效益的方式整合III-V族晶体管与其他场效晶体管,并且利用二极管排除当功率晶体管不导通时累积于III-V族晶体管的源极端的电荷,进而保护III-V族晶体管免于因III-V族晶体管的源极端累积电荷而造成损坏。本发明更提出半导体装置的制造方法,用以将III-V族晶体管以及二极管整合在一起,以进一步降低成本以及减少所需器件数。

有鉴于此,本发明提出一种封装结构,包括一第一引线框架、一第二引线框架、一第三引线框架、一第一衬底、一增强型晶体管、一空乏型III-V族晶体管以及一二极管。上述第一衬底放置于上述第一引线框架上,且与上述第一引线框架电隔离。上述增强型晶体管放置于上述第一衬底上,包括耦接至上述第二引线框架的第一栅极端、耦接至上述第一引线框架的第一源极端以及耦接至上述第一衬底的第一漏极端。上述空乏型III-V族晶体管放置于上述第一引线框架,包括耦接至上述第一引线框架的第二栅极端、耦接至上述第一衬底的第二源极端以及耦接至上述第三引线框架的第二漏极端。上述二极管包括耦接至上述第一引线框架的阳极端以及耦接至上述第二源极端的阴极端。

根据本发明的一实施例,上述空乏型III-V族晶体管更包括一基体端(substrate),其中上述基体端是与上述第一引线框架相互接触,其中上述增强型晶体管是为一垂直式晶体管,其中上述第一漏极端是通过一金属而与上述第一衬底相互接触。

根据本发明的一实施例,上述增强型晶体管以及上述空乏型III-V族晶体管是共源共栅连接而为一功率晶体管,其中上述功率晶体管包括一功率栅极端、一功率源极端以及一功率漏极端,其中上述第一引线框架是耦接至上述功率源极端,上述第二引线框架是耦接至上述功率栅极端,上述第三引线框架是耦接至上述功率漏极端。

根据本发明的一实施例,上述二极管的击穿电压是大于上述空乏型III-V族晶体管的导通阈值电压的1.5倍,且小于上述空乏型III-V族晶体管具有不小于十年寿命的栅极电压。

根据本发明的一实施例,上述二极管是放置于上述第一引线框架上。

根据本发明的另一实施例,上述二极管是放置于上述第一衬底上。

根据本发明的一实施例,上述二极管是内嵌于空乏型III-V族晶体管中。

本发明更提出一种半导体装置制造方法,包括提供一基板,其中上述基板具有一第一导电型;形成一第一III-V族化合物层于该基板上;形成一第二III-V族化合物层于上述第一III-V族化合物层上,使得一载流子通道形成于该第一III-V族化合物层与上述第二III-V族化合物层之间的一界面上;于上述第一III-V族化合物层以及上述第二III-V族化合物层形成一开口,并暴露出基板的一顶面;于上述开口下方之上述基板中形成一掺杂区,其中上述掺杂区具有一第二导电型;形成一栅极结构于上述第二III-V族化合物层之上;以及形成一源极区及一漏极区于该栅极结构的相对两侧,其中上述载流子通道延伸于上述源极区以及上述漏极区之间,上述源极区是位于上述开口以及上述漏极区之间。

根据本发明的一实施例,上述半导体制造方法更包括形成一内连结构,使得上述掺杂区以及上述源极区相互电耦接。

根据本发明的一实施例,上述第一III-V族化合物层具有一厚度,上述开口具有一宽度,其中上述宽度是为上述厚度的五至十倍。

根据本发明的一实施例,上述掺杂区以及上述基板是形成一二极管,上述栅极结构、上述源极区以及上述漏极区是形成一空乏型III-V族晶体管,其中上述二极管的击穿电压是大于上述空乏型III-V族晶体管的导通阈值电压的1.5倍。

根据本发明的一实施例,上述二极管的击穿电压是小于上述空乏型III-V族晶体管具有不小于十年寿命的栅极电压。

本发明提出封装结构以及功率晶体管,以有效率且具有成本效益的方式整合III-V族晶体管与其他场效晶体管,并且利用二极管排除当功率晶体管不导通时累积于III-V族晶体管的源极端的电荷,进而保护III-V族晶体管免于因III-V族晶体管的源极端累积电荷而造成损坏。

附图说明

图1A是显示根据本发明的一实施例所述的封装结构的俯视图;

图1B是显示根据本发明的一实施例所述的封装结构的剖面图;

图2是显示根据本发明的一实施例所述的功率晶体管的电路图;

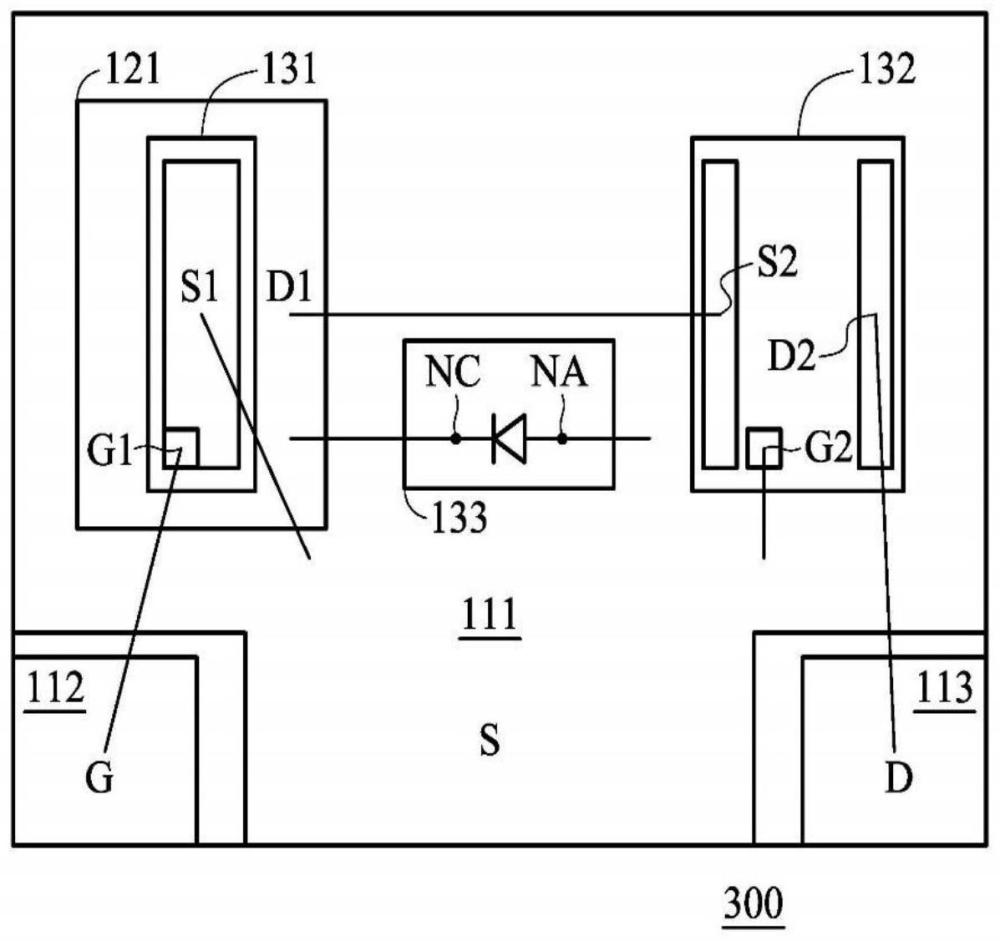

图3A是显示根据本发明的一实施例所述的封装结构的俯视图;

图3B是显示根据本发明的一实施例所述的封装结构的剖面图;

图4是显示根据本发明的一实施例所述的功率晶体管的电路图;

图5A-图5E是显示根据本发明的一实施例所述的半导体装置的制造方法的流程图。

附图标号

100,300:封装结构

111:第一引线框架

112:第二引线框架

113:第三引线框架

121:第一衬底

122:第二衬底

121A:第一金属层

122A:第二金属层

121B:第一绝缘层

122B:第二绝缘层

131:增强型晶体管

132:空乏型III-V族晶体管

133:二极管

200,400:功率晶体管

500:半导体装置

510:基板

520:第一III-V族化合物层

530:第二III-V族化合物层

540:掺杂区

550:栅极结构

560:源极区

570:漏极区

580:载流子通道

590:内连结构

G1:第一栅极端

G2:第二栅极端

S1:第一源极端

S2:第二源极端

D1:第一漏极端

D2:第二漏极端

NA:阳极端

NC:阴极端

G:功率栅极端

S:功率源极端

D:功率漏极端

B:基体端

OP:开口

W:宽度

S:顶面

Y:厚度

L1:第一距离

L2:第二距离

具体实施方式

以下说明为本发明的实施例。其目的是要举例说明本发明一般性的原则,不应视为本发明的限制,本发明的范围当以申请专利范围所界定者为准。

以下针对本揭露一些实施例的器件基底、半导体装置及半导体装置的制造方法作详细说明。应了解的是,以下的叙述提供许多不同的实施例或例子,用以实施本揭露一些实施例的不同样态。以下所述特定的器件基底及排列方式仅为简单清楚描述本揭露一些实施例。当然,这些仅用以举例而非本揭露的限定。此外,在不同实施例中可能使用重复的标号或标示。这些重复仅为了简单清楚地叙述本揭露一些实施例,不代表所讨论的不同实施例及/或结构之间具有任何关连性。再者,当述及一第一材料层位于一第二材料层上或之上时,包括第一材料层与第二材料层直接接触的情形。或者,亦可能间隔有一或更多其它材料层的情形,在此情形中,第一材料层与第二材料层之间可能不直接接触。

此外,实施例中可能使用相对性的用语,例如“较低”或“底部”及“较高”或“顶部”,以描述图式的一个器件对于另一器件的相对关系。能理解的是,如果将图式的装置翻转使其上下颠倒,则所叙述在“较低”侧的器件将会成为在“较高”侧的器件。

能理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种器件、组成成分、区域、层、及/或部分,这些器件、组成成分、区域、层、及/或部分不应被这些用语限定,且这些用语仅是用来区别不同的器件、组成成分、区域、层、及/或部分。因此,以下讨论的一第一器件、组成成分、区域、层、及/或部分可在不偏离本揭露一些实施例的教示的情况下被称为一第二器件、组成成分、区域、层、及/或部分。

除非另外定义,在此使用的全部用语(包括技术及科学用语)具有与本领域技术人员所通常理解的相同涵义。能理解的是,这些用语,例如在通常使用的字典中定义的用语,应被解读成具有与相关技术及本揭露的背景或上下文一致的意思,而不应以一理想化或过度正式的方式解读,除非在本揭露实施例有特别定义。

本揭露一些实施例可配合图式一并理解,本揭露实施例的图式亦被视为本揭露实施例说明的一部分。需了解的是,本揭露实施例的图式并未以实际装置及器件的比例绘示。在图式中可能夸大实施例的形状与厚度以便清楚表现出本揭露实施例的特征。此外,图式中的结构及装置是以示意的方式绘示,以便清楚表现出本揭露实施例的特征。

在本揭露一些实施例中,相对性的用语例如“下”、“上”、“水平”、“垂直”、“之下”、“之上”、“顶部”、“底部”等等应被理解为该段以及相关图式中所绘示的方位。此相对性的用语仅是为了方便说明之用,其并不代表其所叙述的装置需以特定方位来制造或运作。而关于接合、连接的用语例如“连接”、“互连”等,除非特别定义,否则可指两个结构是直接接触,或者亦可指两个结构并非直接接触,其中有其它结构设于此两个结构之间。且此关于接合、连接的用语亦可包括两个结构都可移动,或者两个结构都固定的情况。

图1A是显示根据本发明的一实施例所述的封装结构的俯视图,图1B是显示根据本发明的一实施例所述的封装结构的剖面图。如图1A所示,封装结构100包括第一引线框架111、第二引线框架112、第三引线框架113、第一衬底121、增强型晶体管131以及空乏型III-V族晶体管132。根据本发明的一实施例,第一引线框架111、第二引线框架112、第三引线框架113用以将增强型晶体管131以及空乏型III-V族晶体管132的电极耦接至封装结构100外的外部电路。

如图1A所示,第一衬底121以及第二衬底122皆放置于第一引线框架111之上,并且第一衬底121以及第二衬底122相互隔离。根据本发明的一实施例,第一衬底121以及第二衬底122是为覆铜陶瓷基板(Direct Bonding Copper,DBC)。

如图1B所示,第一衬底121包括第一金属层121A以及第一绝缘层121B,第二衬底122包括第二金属层122A以及第二绝缘层122B。由于第一金属层121A以及第二金属层122A分别通过第一绝缘层121B以及第二绝缘层122B而与第一引线框架111接触,因此第一金属层121A、第二金属层122A以及第一引线框架111之间是为相互电隔离。

如图1A所示,增强型晶体管131是放置于第一衬底121之上,空乏型III-V族晶体管132是放置于第二衬底122之上。如图1B所示,增强型晶体管131是与第一金属层121A相互接触,空乏型III-V族晶体管132是与第二金属层122A相互接触。

根据本发明的一实施例,增强型晶体管131以及空乏型III-V族晶体管132是通过金属,而分别与第一金属层121A以及第二金属层122A相互接触,并且分别固定于第一衬底121以及第二衬底122之上。由于第一金属层121A以及第二金属层122A相互电隔离,因此增强型晶体管131以及空乏型III-V族晶体管132亦相互电隔离。

如图1A所示,增强型晶体管131包括第一栅极端G1、第一源极端S1以及第一漏极端D1。第一栅极端G1是耦接至第二引线框架112,第一源极端S1是耦接至第一引线框架111,第一漏极端D1是耦接至第一衬底121。根据本发明的一实施例,第一栅极端G1以及第一源极端S1是通过键合线(bonding wire),分别电耦接至第二引线框架112以及第一引线框架111。根据本发明的一实施例,增强型晶体管131是为垂直式晶体管,因此增强型晶体管131的第一漏极端D1是与第一衬底121的第一金属层121A相互接触。根据本发明的一实施例,增强型晶体管131是为N型晶体管。

如图1A所示,空乏型III-V族晶体管132包括第二栅极端G2、第二源极端S2以及第二漏极端D2。第二栅极端G2是耦接至第一引线框架111,第二源极端S2是耦接至第一衬底121,第二漏极端D2是耦接至第三引线框架113。如图1B所示,第二源极端S2是耦接至第一金属层121A,使得第二源极端S2以及第一漏极端D1相互电耦接。根据本发明的一实施例,第二栅极端G2、第二源极端S2以及第二漏极端D2是通过键合线,分别电耦接至第一引线框架111、第一衬底121以及第三引线框架113。根据本发明的一实施例,空乏型III-V族晶体管132是为常开型氮化镓晶体管。

图2是显示根据本发明的一实施例所述的功率晶体管的电路图。如图2所示,功率晶体管200是显示图1A、图1B的增强型晶体管131以及空乏型III-V族晶体管132之间的连接关系,其中功率晶体管200是由增强型晶体管131以及空乏型III-V族晶体管132所组成的开关器件,包括功率栅极端G、功率源极端S以及功率漏极端D。将图1A与图2相互比对,第一引线框架111是对应至功率晶体管200的功率源极端S,第二引线框架112是对应至功率晶体管200的功率栅极端G,第三引线框架113是对应至功率晶体管200的功率漏极端D。

如图2所示,空乏型III-V族晶体管132更包括基体端B,其中基体端B是为浮接状态(Floating state)。如图1A、图1B所示,基体端B是位于空乏型III-V族晶体管132的背面而与第二衬底122的第二金属层122B相互接触,并且第二金属层122B是为浮接状态,故基体端B亦为浮接状态。

根据本发明的许多实施例,由于实际上发现当空乏型III-V族晶体管132的基体端B为浮接状态且功率晶体管200是为不导通(即,功率栅极端G至功率源极端S的跨压(Gate-to-source voltage)是为0V)时,累积在第二源极端S2(亦即,第一漏极端D1)电荷无法通过增强型晶体管131的通道放电至功率源极端S而发生第二源极端S2(亦即,第一漏极端D1)电压升高的现象,进而造成空乏型III-V族晶体管132的栅极介电层产生损伤。

图3A是显示根据本发明的一实施例所述的封装结构的俯视图。图3B是显示根据本发明的一实施例所述的封装结构的剖面图。将图3A与图1A相比,封装结构300相较于封装结构100省略了第二衬底122,更包括了二极管133。如图3B所示,空乏型III-V族晶体管132是放置于第一引线框架111之上。根据本发明的一实施例,空乏型III-V族晶体管132是通过金属而与第一引线框架111黏合,并且基体端B是通过金属而与第一引线框架111相互接触。

如图3A所示,二极管133包括阳极端NA以及阴极端NC,其中阳极端NA是耦接至第一引线框架111,阴极端NC是耦接至第一衬底121。如图1B所示,二极管133是耦接于第一漏极端D1(或第二源极端S2)以及第一引线框架111之间。根据本发明的一实施例,由于空乏型III-V族晶体管132的基体端B是与第一引线框架111相互接触,因此二极管133是耦接于空乏型III-V族晶体管132的第二源极端S2以及基体端B之间。根据本发明的一实施例,二极管133是为外部器件,且放置于第一引线框架111之上。根据本发明的另一实施例,二极管133是放置于第一衬底121之上。根据本发明的另一实施例,二极管133是与空乏型III-V族晶体管132整合在一起,下文中将详细描述如何将空乏型III-V族晶体管132以及二极管133整合在一起。

图4是显示根据本发明的一实施例所述的功率晶体管的电路图。如图4所示,功率晶体管400是显示图3A、图3B的增强型晶体管131、空乏型III-V族晶体管132以及二极管133之间的连接关系,其中功率晶体管400是由增强型晶体管131、空乏型III-V族晶体管132以及二极管133所组成的开关器件,包括功率栅极端G、功率源极端S以及功率漏极端D。将图3A与图4相互比对,第一引线框架111是对应至功率晶体管400的功率源极端S,第二引线框架112是对应至功率晶体管400的功率栅极端G,第三引线框架113是对应至功率晶体管400的功率漏极端D。

如图4所示,空乏型III-V族晶体管132的基体端B是电耦接至增强型晶体管131的第一源极端S1以及二极管133的阳极端NA,亦即基体端B、第一源极端S1以及阳极端NA皆电耦接至功率晶体管400的功率源极端S。如图3A、图3B所示,基体端B是位于空乏型III-V族晶体管132的背面,通过金属而与第一引线框架111相互接触。

当功率晶体管400不导通(即,功率栅极端G至功率源极端S的跨压是为0V)时,累积在第二源极端S2(亦即,第一漏极端D1)电荷可以通过逆偏的二极管133而将多余的电荷排除至功率源极端S,进而降低第二源极端S2(亦即,第一漏极端D1)的电压而延长空乏型III-V族晶体管132的寿命。此外,封装结构300相较于图1的封装结构100,更可省下第一衬底122的成本。

根据本发明的一实施例,二极管133的击穿电压是大于空乏型III-V族晶体管132的导通阈值电压的1.5倍,且小于空乏型III-V族晶体管132的时变介质击穿(time-dependent dielectric breakdown,TDDB)具有不小于十年寿命的栅极电压。根据本发明的其他实施例,二极管133可为其他用以排除多余电荷的常闭器件,如静电保护器件等。

图5A-图5E是显示根据本发明的一实施例所述的半导体制造方法的流程图。如图5A所示,半导体装置500包括基板510,其中半导体装置500是形成于基板510之上,且基板510是为具有第一导电型的硅基板。根据本发明的一实施例,第一导电型是为P型。

如图5A所示,半导体装置500更包括第一III-V族化合物层520以及第二III-V族化合物层530,其中第一III-V族化合物层520形成于基板510上,而第二III-V族化合物层530再形成于第一III-V族化合物层520上。根据本发明的一实施例,第一III-V族化合物层520及第二III-V族化合物层530是具有不同带隙(band gap)的材料层。根据本发明的一实施例,第一III-V族化合物层520及第二III-V族化合物层530是由周期表上第III-V族的元素所形成的化合物所构成,然而,第一III-V族化合物层520及第二III-V族化合物层530彼此在组成上是不同的。

根据本发明的一实施例,第一III-V族化合物层520包含GaN层,第二III-V族化合物层530包含AlxGa1-xN层,其中0 第一III-V族化合物层520与第二III-V族化合物层530之间的带隙不连续性(bandgap discontinuity)与压电效应(piezo-electric effect)在第一III-V族化合物层520与第二III-V族化合物层530之间的界面附近产生具有高移动传导电子的载流子通道(图中并未显示),此载流子通道称为二维电子气(two-dimensional electron gas,2-DEG),其形成载流子通道于第一III-V族化合物层520与第二III-V族化合物层530的界面上。 如图5B所示,于第一III-V族化合物层520以及第二III-V族化合物层530形成开口OP,并暴露出基板510的顶面S。根据本发明的一实施例,开口OP具有宽度W,第一III-V族化合物层520具有厚度Y,其中宽度W是大于厚度Y的十倍。根据本发明的一实施例,可利用图案化工艺于第一III-V族化合物层520以及第二III-V族化合物层530形成开口OP而暴露出机板510的顶面S,图案化工艺例如合适的光刻(photolithography)工艺及刻蚀工艺。 在一些实施例中,光刻工艺包括光刻胶(photoresist)涂布(例如:自旋涂布(spin-on coating))、软烤、掩膜对准、曝光、曝后烤、显影光刻胶、冲洗(rinsing)、干燥(例如:硬烤)。在其他实施例中,光刻工艺可藉由其他适当的方法来执行或取代,例如无掩膜光刻(maskless photolithography)、电子束写入(electron-beam writing)、以及离子束写入(ion-beam writing)。在一些实施例中,刻蚀工艺可包括干法刻蚀、湿法刻蚀、反应离子刻蚀(reactive ion etching,RIE)、及/或其他合适的工艺。 如图5C所示,半导体装置500更包括掺杂区540。掺杂区540是形成于开口OP下方的基板510中,其中掺杂区540具有第二导电型。掺杂区540形成方法可藉由离子注入(implantation)工艺,离子注入工艺可注入具有第二导电型的杂质至开口OP下方的基板510中,以形成掺杂区540。根据本发明的一实施例,第二导电型是为N型。 如图5D所示,半导体装置500更包括栅极结构550、源极区560以及漏极区570。栅极结构550是形成于第二III-V族化合物层530上,并且于栅极结构550的相对两侧形成源极区560以及漏极区570。在一些实施例中,源极区560与栅极区550相距第一距离L1,漏极区570与栅极区550相距第二距离L2,其中第二距离L2大于第一距离L1。 栅极结构550可包含栅极介电层和栅极电极(未绘示)。栅极介电层可包含一或多层介电材料,例如氧化硅、氮化硅、高介电常数介电材料或其他适合的介电材料。高介电常数介电材料的例子包含HfO 源极区560以及漏极区570包含一种或一种以上的导电材料,例如源极区560以及漏极区570包含金属,其是选自于由钛、铝、镍与金所组成的群组。源极区560以及漏极区570可藉由物理气相沉积法(physicalvapordeposition,PVD)、化学气相沉积法(chemicalvapordeposition,CVD)、原子层沉积法(atomiclayerdeposition,ALD)、涂布、溅射或其他适合的技术形成。在此实施例中,载流子通道580延伸于源极区560以及漏极区570之间,且形成于第一III-V族化合物层520与第二III-V族化合物层530的界面上。根据本发明的一实施例,源极区560是邻近掺杂区540。 如图5E所示,半导体装置500更形成内连结构590,其中内连结构590用以将掺杂区540电耦接至源极区560。根据本发明的一实施例,掺杂区540以及基板510是形成二极管,栅极结构550、源极区560以及漏极区570是形成空乏型III-V族晶体管。 换句话说,当图4的空乏型III-V族晶体管132以及二极管133整合在一起时,图5E的栅极结构550、源极区560以及漏极区570是形成图4的空乏型III-V族晶体管132,图5E的掺杂区540以及基板510是形成图4的二极管133。当空乏型III-V族晶体管132以及二极管133整合在一起时,有助于降低成本,并且二极管133提供了累积于第二源极端S2(亦即,第一漏极端D1)的电荷的排除路径,有助于降低对空乏型III-V族晶体管132的损害,进而提高空乏型III-V族晶体管132的寿命。 本发明提出封装结构以及功率晶体管,以有效率且具有成本效益的方式整合III-V族晶体管与其他场效晶体管,并且利用二极管排除当功率晶体管不导通时累积于III-V族晶体管的源极端的电荷,进而保护III-V族晶体管免于因III-V族晶体管的源极端累积电荷而造成损坏。本发明更提出半导体装置的制造方法,用以将III-V族晶体管以及二极管整合在一起,以进一步降低成本以及减少所需器件数。 虽然本揭露的实施例及其优点已揭露如上,但应该了解的是,任何本领域技术人员,在不脱离本揭露的精神和范围内,当可作更动、替代与润饰。此外,本揭露的保护范围并未局限于说明书内所述特定实施例中的工艺、机器、制造、物质组成、装置、方法及步骤,任何本领域技术人员可从本揭露一些实施例的揭示内容中理解现行或未来所发展出的工艺、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本揭露一些实施例使用。因此,本揭露的保护范围包括上述工艺、机器、制造、物质组成、装置、方法及步骤。另外,每一申请专利范围构成个别的实施例,且本揭露的保护范围也包括各个申请专利范围及实施例的组合。