单硅片上集成制造四种电化学敏感电极的MEMS芯片及制造方法

文献发布时间:2023-06-19 19:18:24

技术领域

本发明涉及MEMS传感器和低频振动信号检测领域,尤其涉及MEMS工艺制作领域,具体涉及一种单硅片上集成制造四种电化学敏感电极的MEMS芯片及制造方法。

背景技术

电化学式地震检波器是以液体为惯性质量块的振动传感器,具有灵敏度高、噪声低和低频信号检测性能好等特点。与传统的电容或电磁式的地震检波器相比,电化学式地震检波器的工作倾角较大。一般能达到10°~15°以上。

电化学振动传感器的核心单元由敏感电极、电解液等组成。敏感电极主要采用阳极阴极阴极阳极的排列方式。电解液由含有KI和I

目前MEMS工艺制作的敏感电极芯片主要使用ACCA电极排布形式。使用集成两种电极的AC敏感电极芯片,通过手动对准的粘连方式或者阳极键合工艺将这两种芯片组合起来,形成一块ACCA敏感电极芯片。手动对准的粘连方式,对准精度低,阳极键合工艺相对复杂,成品率不高,且都需要消耗多层硅片,电极集成度低。

发明内容

为解决上述技术问题,本发明提供一种单硅片上集成制造四种电化学敏感电极的MEMS芯片及制作方法,在电极结构保证高灵敏度的同时,实现单硅片集成四种电极,降低生产成本。

为达到上述目的,本发明采用如下技术方案:

一种单硅片上集成制造四种电化学敏感电极的MEMS芯片,包含硅基底、贯通硅基底的流孔、绝缘层、第一阳极、第一阴极、第二阳极、第二阴极;

所述硅基底厚度均匀,表面洁净;所述流孔贯通硅基底的上下表面;所述绝缘层形成于硅基底上下表面,分为上表面绝缘层和下表面绝缘层;所述绝缘层还形成于流孔内壁,可以分为上内壁绝缘层和下内壁绝缘层;

所述第一阳极形成于所述的上表面绝缘层;第一阳极包括多个第一阳极引线和第一阳极焊盘;所有的第一阳极引线等间隔排列,末端都汇聚于第一阳极焊盘;

所述第一阴极形成于所述的上表面绝缘层和上内壁绝缘层;第一阴极包括第一阴极引线、第一侧壁阴极和第一阴极焊盘;所述第一侧壁阴极通过第一阴极引线引出与第一阴极焊盘连接;

所述第二阳极形成于所述的下表面绝缘层,第二阳极包括多个第二阳极引线和第二阳极焊盘;所有的第二阳极引线等间隔排列,末端都汇聚于第二阳极焊盘;第二阴极形成于所述的下表面绝缘层和下内壁绝缘层,所述第二阴极包括第二阴极引线、第二侧壁阴极和第二阴极焊盘;所述第二侧壁阴极通过第二阴极引线引出与第二阴极焊盘连接;

通过调整溅射过程中金属靶材和圆片的相对角度,在流孔侧壁上的第一阴极和第二阴极之间的制作绝缘区域,实现电极绝缘。

进一步地,硅基底的材料是硅片,选择晶向为<100>的N型硅或者P型硅,厚度在400um-500um范围内。

进一步地,所述流孔采用BOSCH工艺在硅基底的硅片上进行双面刻蚀,流孔分布是圆形或者六边形。

进一步地,所述绝缘层的材料采用氧化硅或者氮化硅。

进一步地,所述四种电极的材料为金属铂。

进一步地,流孔以单元的形式存在,一单元包括一个或多个流孔;每一个单元被第一阴极或者第二阴极完全覆盖,单元与单元间通过阴极引线串联。

进一步地,相邻的第一阳极引线、第二阳极引线均包裹一组单元和它们之间起串联作用的阴极引线。

本发明提供一种单硅片上集成制造四种电化学敏感电极的MEMS芯片的制造方法,包括以下步骤:

步骤(1):选择并清洗硅基底;

步骤(2):使用正性光刻胶在硅基底上表面进行匀胶、前烘、曝光、显影,暴露通孔位置,形成流孔刻蚀光刻胶掩膜;

步骤(3):利用深硅刻蚀设备进行通孔的刻蚀,刻蚀深度略超过硅基底的一半厚度;刻蚀过后去除光刻胶掩膜,清洗硅基底;

步骤(4):使用正性光刻胶在硅基底下表面进行匀胶,、前烘、曝光、显影,暴露通孔位置,形成流孔刻蚀光刻胶掩膜;工艺参数同步骤(2);

步骤(5):利用深硅刻蚀设备进行通孔的刻蚀,刻蚀深度略超过硅基底的一半厚度,使两次刻蚀的通孔贯通,形成流孔;工艺参数同步骤(3);刻蚀过后去除光刻胶掩膜,清洗硅基底;

步骤(6):在硅基底的上下表面和流孔内壁生长绝缘层;

步骤(7):在上表面绝缘层上使用干膜,进行曝光、显影,暴露流孔、第一阳极引线和第一阴极引线的位置,形成电极溅射掩膜;

步骤(8):使用溅射工艺在上表面绝缘层和上内壁绝缘层上溅射金属;

步骤(9):去除干膜和其上的金属,形成电极图形;

步骤(10):在下表面绝缘层上使用干膜,进行曝光、显影,暴露流孔、第一阳极引线和第一阴极引线的位置,形成电极溅射掩膜;工艺参数同步骤(7);

步骤(11):使用溅射工艺在下表面绝缘层和下内壁绝缘层上溅射金属;工艺参数同步骤(8);

步骤(12);去除干膜和其上的金属,形成电极图形;

步骤(13):清洗制作完成的集成电极芯片。

本发明还提供另一种单硅片上集成制造四种电化学敏感电极的MEMS芯片的制造方法,包括以下步骤:

步骤(1):选择并清洗硅基底,所述基底为高电阻率硅;

步骤(2):在硅基底的上下表面生长绝缘层;

步骤(3):使用反转光刻胶在上表面绝缘层进行匀胶、前烘、曝光、后烘、泛曝光、显影,暴露电极引线位置,形成溅射光刻胶掩膜;

步骤(4):使用溅射工艺在上表面绝缘层溅射金属;

步骤(5):去除光刻胶及其上的金属,形成电极引线图形;

步骤(6):使用负性光刻胶在下表面绝缘层进行匀胶,前烘、曝光、后烘、泛曝光、显影,暴露电极引线位置,形成溅射光刻胶掩膜;工艺参数同步骤(3);

步骤(7):使用溅射工艺在下表面绝缘层溅射金属;工艺参数同步骤(4);

步骤(8):去除光刻胶及其上的金属,形成电极引线图形;

步骤(9):使用正性光刻胶在基底上表面进行匀胶、前烘、曝光、显影,暴露通孔位置,形成通孔刻蚀光刻胶掩膜;

步骤(10):利用深硅刻蚀设备进行通孔的刻蚀,刻蚀深度略超过基底的一半厚度;刻蚀过后去除光刻胶掩膜,清洗硅基底;

步骤(11):使用正性光刻胶在基底下表面进行匀胶、前烘、曝光、显影,暴露通孔位置,形成通孔刻蚀光刻胶掩膜;工艺参数同步骤(9);

步骤(12):利用深硅刻蚀设备进行通孔的刻蚀,刻蚀深度略超过基底的一半厚度;刻蚀过后去除光刻胶掩膜,清洗硅基底;使两次刻蚀的通孔贯通,形成流孔;

步骤(13):在上表面绝缘层上使用干膜,进行曝光、显影,暴露流孔的位置,形成电极溅射掩膜;

步骤(14):使用溅射工艺在流孔上内壁溅射金属;

步骤(15):去除干膜和其上的金属,形成侧壁电极图形;

步骤(16):在下表面绝缘层上使用干膜,进行曝光、显影,暴露流孔的位置,形成电极溅射掩膜;工艺参数同步骤(13);

步骤(17):使用溅射工艺在流孔下内壁溅射金属;工艺参数同步骤(14);

步骤(18);去除干膜和其上的金属,形成侧壁电极图形;

步骤(19):清洗制作完成的集成电极芯片。

有益效果:

(1)本发明在单片硅片上集成制作了四种电极,提升了敏感电极集成度,可以减少芯片的使用数量,提高生产效率,降低生产成本。

(2)本发明电极和流孔的一致性误差取决于光刻对准的误差,器件一致性好。

(3)本发明验证了倾斜溅射避免流孔内壁上下电极短接的可行性,为后面的集成电极芯片的设计提供一种参照方法。

附图说明

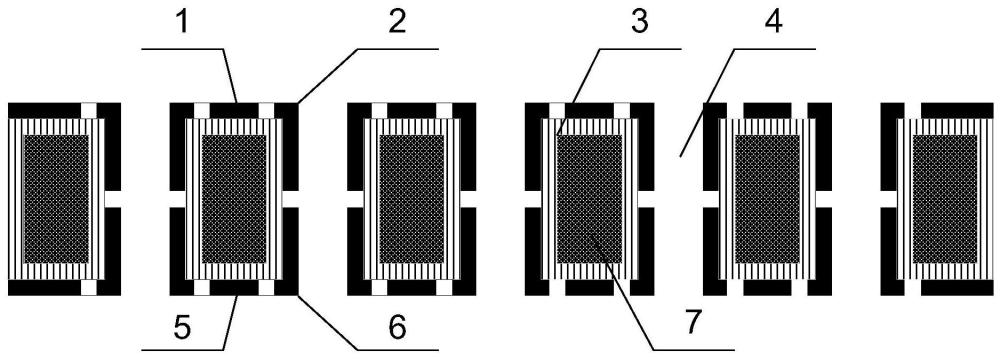

图1为本发明实施例集成四电极芯片的侧向剖视图;

图中数字代表:1第一阳极;2第一阴极;3绝缘层;4流孔;5第二阳极;6第二阴极;7硅基底。

图2为本发明实施例集成四电极芯片的上表面俯视图;

图3为本发明实施例集成四电极芯片最小流孔单元的排布方式示意图;其中流孔直径都相等;其中,图(A)为单孔单元,图(B)为双圈七孔单元,图(C)为三圈十九孔单元;

图4为本发明实施例倾斜溅射效果示意图;

图5为本发明实施例的单硅片上集成制造四种电化学敏感电极的MEMS芯片的制造方法工艺流程图;其中,图(1)为步骤(1)示意图,图(2)为步骤(2)示意图,图(3)为步骤(3)示意图,图(4)为步骤(4)示意图,图(5)为步骤(5)示意图,图(6)为步骤(6)示意图,图(7)为步骤(7)示意图,图(8)为步骤(8)示意图,图(9)为步骤(9)示意图,图(10)为步骤(10)示意图,图(11)为步骤(11)示意图,图(12)为步骤(12)示意图;

图6为本发明实施例的单硅片上集成制造四种电化学敏感电极的MEMS芯片的另一种制造方法工艺流程图;其中,图(1)为步骤(1)示意图,图(2)为步骤(2)示意图,图(3)为步骤(3)示意图,图(4)为步骤(4)示意图,图(5)为步骤(5)示意图,图(6)为步骤(6)示意图,图(7)为步骤(7)示意图,图(8)为步骤(8)示意图,图(9)为步骤(9)示意图,图(10)为步骤(10)示意图,图(11)为步骤(11)示意图,图(12)为步骤(12)示意图,图(13)为步骤(13)示意图,图(14)为步骤(14)示意图,图(15)为步骤(15)示意图,图(16)为步骤(16)示意图,图(17)为步骤(17)示意图,图(18)为步骤(18)示意图。

具体实施方式

下面结合附图及具体实施例详细介绍本发明。但以下的实施例仅限于解释本发明,本发明的保护范围应包括权利要求的全部内容,而且通过以下实施例的叙述,本领域的技术人员是可以完全实现本发明权利要求的全部内容。

图1是本发明所提出的单硅片上集成制造四种电化学敏感电极的MEMS芯片的侧向剖视图。如图1所示,本发明在单片硅片分布四种电极,包括第一阳极1、第一阴极2、绝缘层3、流孔4、第二阳极5、第二阴极6以及硅基底7。

流孔4贯通硅基底7的上下表面。绝缘层3形成于硅基底7上下表面,可以分为上表面绝缘层和下表面绝缘层;绝缘层3也形成于流孔4内壁,可以分为上内壁绝缘层和下内壁绝缘层。

如图2是本发明所提出的单硅片上集成制造四种电化学敏感电极的MEMS芯片的上表面俯视图。第一阳极1形成于所述的上表面绝缘层;第一阳极1可以分成第一阳极引线和第一阳极焊盘。所有的第一阳极引线等间隔排列,末端都汇聚于第一阳极焊盘。

第一阴极2形成于所述的上表面绝缘层和上内壁绝缘层;第一阴极2可以分成第一阴极引线、第一侧壁阴极和第一阴极焊盘。第一侧壁阴极通过第一阴极引线引出与第一阴极焊盘连接。

第二阳极5形成于所述的下表面绝缘层,和第一阳极1的分布类似;

第二阴极6形成于所述的下表面绝缘层和下内壁绝缘层,和第一阴极2的分布类似;

相邻阴极引线间的流孔排布并不局限于图3(A)中的单孔分布。如图3所示,流孔的排布还可以是图3的图(B)的双环六边形分布和图3的图(C)的三环六边形分布。图3所示三种排布方式的区别在于,相邻阳极引线内,有效阴极面积的不同。

通过调整溅射过程中金属靶材和圆片的相对角度,可以实现流孔侧壁上两个阴极的隔断,实现绝缘。如图4所示,如果靶材和与圆片的倾斜夹角为70°,要实现60μm的流孔内溅射电极,中间形成绝缘区域,硅片厚度要大于2*60*tan(70°),约等于320μm,所以硅片的厚度选择在400~500μm即可。硅片厚度越大,绝缘效果越好,但是增加流孔深刻蚀的时间。在溅射的过程中,圆片托盘以一定的角速度做匀速转动,保证溅射金属层的厚度均匀。

图5是本发明提出的单硅片上集成制造四种电化学敏感电极的MEMS芯片的制造方法工艺流程图。具体工艺步骤如下:

步骤(1):如图5的图(1)所示,选择电阻率大于10000Ω·cm,厚度为425μm的四英寸硅片,进行煮酸和煮水,清洁硅片表面的污染物。清理完后作为硅基底7。

步骤(2):如图5的图(2)所示,在硅片上表面旋涂一层AZ4620正性光刻胶,厚度要求达到6.5μm。通过前烘、曝光、显影暴露出通孔图形。

步骤(3):如图5的图(3)所示,使用步骤(2)中显影完的光刻胶作为刻蚀掩膜。使用DRIE(深反应离子刻蚀)工艺刻蚀硅,深度大概略超过硅基底厚度的一半。刻蚀完后,使用丙酮去除光刻胶。

步骤(4):如图5的图(4)所示,使用和步骤(2)同样的办法在硅片下表面制作同样的光刻胶掩膜。

步骤(5):如图5的图(5)所示,使用和步骤(3)同样的刻蚀参数,使通孔贯通形成流孔4;

步骤(6):如图5的图(6)所示,使用干氧、湿氧、干氧的交替热氧化工艺,在硅片表面快速生长绝缘层3,为600nm厚度的氧化硅,形成上表面绝缘层、下表面绝缘层、上内壁绝缘层、下内壁绝缘层。

步骤(7):如图5的图(7)所示,在上表面绝缘层上粘贴一层干膜光刻胶,通过曝光、显影、坚膜,暴露第一阳极和第一阴极的图形,制作干膜光刻胶掩模。干膜光刻胶为负性光刻胶,厚度一般大于15μm。

步骤(8):如图5的图(8)所示,使用倾斜溅射的方法,在步骤(7)中制作的干膜光刻胶掩膜上沉积一层金属60nm Ti/300nm Pt。

步骤(9):如图5的图(9)所示,用丙酮浸泡溅射后的圆片,去除干膜光刻胶和多余金属,形成第一阳极1和第一阴极2。其中第一阳极1可以分为第一阳极引线和第一阳极焊盘。第一阴极2可以分为第一阴极引线、第一侧壁阴极和第一阴极焊盘。

步骤(10):如图5的图(10)所示,同步骤(7),在下表面绝缘层上制作溅射干膜光刻胶掩膜。

步骤(11):如图5的图(11)所示,使用倾斜溅射的方法,同步骤(8),在步骤(7)中制作的干膜光刻胶掩膜上沉积一层金属60nm Ti/300nm Pt。

步骤(12):如图5的图(12)所示,用丙酮浸泡溅射后的圆片,去除干膜光刻胶,形成第二阳极5和第二阴极6。其中第二阳极5可以分为第二阳极引线和第二阳极焊盘。第二阴极6可以分为第二阴极引线、第二侧壁阴极和第二阴极焊盘。

步骤(13):清洗制作完成的集成电极芯片。

图6是本发明提出的集成四电极芯片的另一种MEMS工艺。由于使用干膜制作的掩膜线条尺寸有限,如果想要进一步缩小阴阳极引线宽度,减小阴阳极间距,增加流孔数以提升敏感电极的灵敏度可以采用此方法。具体工艺步骤如下:

步骤(1):如图6的图(1)所示,选择电阻率大于10000Ω·cm,厚度为425μm的四英寸硅片,进行煮酸和煮水,清洁硅片表面的污染物。清理完后作为基底007。

步骤(2):如图6的图(2)所示,使用干氧湿氧干氧的交替热氧化工艺,在硅片表面快速生长绝缘层003,为600nm厚度的氧化硅,形成上表面绝缘层、下表面绝缘层。

步骤(3):如图6的图(3)所示,在硅片上表面旋涂一层AZ5214E反转光刻胶,厚度要求达到1.5μm。通过前烘、曝光、反转烘、泛曝光、显影暴露出第一电极引线和第一电极焊盘图形。

步骤(4):如图6的图(4)所示,使用溅射工艺,在步骤(3)中制作的光刻胶掩膜上沉积一层金属60nm Ti/300nm Pt。

步骤(5):如图6的图(5)所示,用丙酮浸泡溅射后的圆片,去除光刻胶和多余金属,形成第一阳极001和第一阴极002。其中第一阳极可以分为第一阳极引线和第一阳极焊盘。第一阴极可以分为第一阴极引线和第一阴极焊盘,不包括第一侧壁阴极。

步骤(6):如图6的图(6)所示,同步骤(3)在下表面绝缘层上制作溅射光刻胶掩膜。

步骤(7):如图6的图(7)所示,使用溅射工艺,在步骤(6)中制作的光刻胶掩膜上沉积一层金属60nm Ti/300nm Pt。

步骤(8):如图6的图(8)所示,用丙酮浸泡溅射后的圆片,去除光刻胶,形成第二阳极005和第二阴极006。其中第二阳极可以分为第二阳极引线和第二阳极焊盘。第二阴极可以分为第二阴极引线和第二阴极焊盘,不包括第二侧壁阴极。

步骤(9):如图6的图(9)所示,在硅片上表面旋涂一层AZ4903正性光刻胶,厚度要求达到7.5μm。通过前烘、曝光、显影暴露出流孔图形。

步骤(10):如图6的图(10)所示,使用步骤(9)中显影完的光刻胶作为刻蚀掩膜。先使用RIE(反应离子刻蚀)去除暴露的上表面绝缘层。再使用DRIE(深反应离子刻蚀)工艺刻蚀硅,深度大概略超过基底厚度的一半。刻蚀完后,使用丙酮去除光刻胶。

步骤(11):如图6的图(11)所示,使用和步骤(9)同样的办法在硅片下表面制作同样的光刻胶掩膜。

步骤(12):如图6的图(12)所示,使用和步骤(10)同样的刻蚀参数,使流孔贯通形成通孔004;

步骤(13):如图6的图(13)所示,在上表面绝缘层上粘贴一层干膜光刻胶,通过曝光、显影、坚膜,暴露第一侧壁阴极的图形。干膜光刻胶为负性光刻胶,厚度一般大于15μm。

步骤(14):如图6的图(14)所示,使用倾斜溅射的方法,在步骤(7)中制作的光刻胶掩膜上沉积一层金属60nm Ti/300nm Pt。

步骤(15):如图6的图(15)所示,用丙酮浸泡溅射后的圆片,去除干膜光刻胶,形成第一侧壁阴极

步骤(16):如图6的图(16)所示,同步骤(13)在下表面绝缘层上制作溅射光刻胶掩膜。

步骤(17):如图6的图(17)所示,使用倾斜溅射的方法,同步骤(14)工艺参数,在步骤(16)中制作的光刻胶掩膜上沉积一层金属60nm Ti/300nm Pt。

步骤(18):如图6的图(18)所示,用丙酮浸泡溅射后的圆片,去除干膜光刻胶,形成第二侧壁阴极。

步骤(19):清洗制作完成的集成电极芯片。

在本发明的一些实施例中,绝缘层3的材料既可以是氧化硅,也可以是氮化硅等其他绝缘材料;

在本发明的一些实施例中,进行两次深硅刻蚀是受限于加工设备的刻蚀能力的妥协方法。如果工艺条件允许,可以只进行一次深硅刻蚀来制作通孔;

在本发明的一些实施例中,绝缘层3的氧化硅可以通过热氧化工艺制作,也可以使用CVD设备沉积制作;

在本发明的一些实施例中,硅片可用N型硅或者P型硅,电阻率没有固定值,但第二种方法必须使用高阻硅。

本发明未详细阐述部分属于本领域技术人员的公知技术。以上所述的实施例仅是对本发明的优选实施方式进行描述,优选实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施方式。在不脱离本发明设计精神的前提下,本领域普通技术人员对本发明的技术方案做出的各种变形和改进,均应落入本发明权利要求书确定的保护范围内。