一种基于飞秒激光直写的集成微纳电极及制备方法

文献发布时间:2024-01-17 01:14:25

技术领域

本发明涉及飞秒激光直写技术、反应离子刻蚀及湿法腐蚀技术领域,特别是一种利用金属膜及介质膜等材料结合飞秒激光直写、干法湿法刻蚀技术制备铌酸锂光子芯片上的集成微纳电极的方法。

背景技术

与电子集成回路不同,光子集成回路是以光子作为传输载体可实现更高传输速度、更大传输容量等特性,因此作为新一代技术平台已经被广泛应用于光学通讯、微波光子学、量子信息处理等领域。目前人们在硅、III-V族半导体材料、氮化硅等材料上已经取得了一系列进展也实现大规模应用。而铌酸锂被称作光子学中的“硅”,主要是由于其具备众多优异的特性,如:具有宽透光窗口、相对较大的折射率,高非线性系数以及较大的电光调制系数等等。相比于其它光子集成回路材料,电光效应是铌酸锂最典型也是最主要的特征之一,在电光调制器、微波光子学均具有广泛的应用。传统的铌酸锂光子芯片的集成微纳电极制备主要采用电子束直写或者紫外光刻的金属剥离工艺,此方式制备效率低而且成本较高,亟需发展一套基于飞秒激光直写的集成微纳电极制备工艺。

发明内容

本发明的目的旨在克服传统电子束直写制备成电极技术难以大规模制备大尺寸的光子芯片中微纳集成电极的问题,提供一种替代技术路线来制备低成本的微纳电极并且结构均匀性、方法便捷性均有提升。

实现本发明目的的具体技术方案是:

一种基于飞秒激光直写的集成微纳电极的制备方法,该制备方法包括以下步骤:

步骤1)准备铌酸锂光子芯片并镀铬膜、二氧化硅膜以及铬膜:

1.1)铌酸锂光子芯片(1)材料包括三层:从上至下依次为300nm-600nm厚铌酸锂薄膜(2)、2μm-8μm厚二氧化硅层(3)和500μm-1mm厚单晶硅衬底(4);其铌酸锂薄膜(2)上设有系列脊状光波导结构;

1.2)在所述的铌酸锂光子芯片表面通过磁控溅射镀600nm-1μm厚铬膜作为后续底层牺牲层;

1.3)用化学气象沉积的方法在上述结构上镀400nm-1μm二氧化硅层,作为电极结构顶层的限定层;

1.4)利用磁控溅射在上述结构上镀50nm-100nm铬膜,作为电极结构的掩膜层;

步骤2)飞秒激光直写电极铬掩膜图案:

2.1)将表面镀有上述三层膜的铌酸锂光子芯片通过吸盘固定在可计算机编程控制的三维运动平台上,通过显微物镜将飞秒激光聚焦到所述的电极结构掩膜层表面,通过计算机程序驱动运动平台利用飞秒激光直写所述铬膜层,形成电极掩模图案;

步骤3)反应离子刻蚀二氧化硅膜:

3.1)将上述芯片放置于反应离子刻蚀机的腔室中,将气腔抽至真空,设置气压、射频功率、偏压以及刻蚀时间等参数,实现对所述铌酸锂光子芯片的二氧化硅限定层进行刻蚀,用于控制结构线宽,被所述电极结构铬掩模图案保护下的二氧化硅层不被离子刻蚀,其它未被所述电极铬掩模图案保护下的二氧化硅膜被高密度等离子源轰击而被刻蚀,将二氧化硅层完全刻蚀,刻蚀深度为400nm-1μm,由于最底层存在一层铬膜牺牲层可以阻挡离子刻蚀的过刻问题,保护铌酸锂薄膜;

步骤4)化学腐蚀底层铬膜牺牲层:

4.1)将所述刻蚀二氧化硅层后的芯片放置于商业铬腐蚀液中,控制腐蚀时间,将刻蚀后剩余的顶上铬掩膜层去掉,所述底层铬膜牺牲层且未被二氧化硅保护下的部分完全腐蚀干净,由于湿法腐蚀金属是各向同性的,向下腐蚀的同时也会向四周腐蚀,在这个作用下,底层铬膜牺牲层与顶上二氧化硅电极结构限定层可以行成底切结构方便后续工艺;

步骤5)电子束蒸发镀钛-金电极:

5.1)将所述湿法腐蚀结束后芯片放置于电子蒸发腔室中,将气腔抽至真空,设置镀膜参数,蒸镀10-100nm钛膜作为金膜的粘附层,然后再镀500nm-800nm金膜,确保底层铬膜牺牲层厚度至少是被剥离金属层厚度1.25倍;相比于溅射工艺,电子束蒸发金属膜以类似辐射的方式沉积至材料上,方向性,可避免后续剥离困难以及边缘不光滑毛刺等现象;

步骤6)湿法腐蚀剥离制备集成电极

6.1)将所述电子束蒸发镀完钛-金电极芯片放置于商业铬腐蚀液,控制腐蚀参数结合超声辅助将底层铬膜牺牲层剥离掉,由于上述在电极掩膜保护下的底层铬膜还存在将在剥离过程中被去除,同时将对应的金电极结构去除,上述激光刻写的结构由于底层铬膜在前述工艺中被去除,这里的金膜将直接与铌酸锂薄膜粘合,剥离结束后可制备预先设计好的电极结构。

一种上述方法制得的基于飞秒激光直写的集成微纳电极。

与现有技术相比较,本发明的优点在于:

本发明利用金属薄膜及介质膜代替传统光刻胶的方案,适用于飞秒激光直写技术及反应离子刻蚀方式,与使用紫外光刻技术或者电子束直写技术相比,成本低,效率高,无需额外制备掩膜版。

1)提供了一套可以与化学机械抛光技术兼容,可应对任意复杂大尺寸集成电极结构的制备路线。

2)提供了一种电极均一性,侧壁粗糙度,微波损耗等电极性能达到最佳的制备方法,对集成光子学中的电光、热光调控等特性有着重要的作用。

附图说明

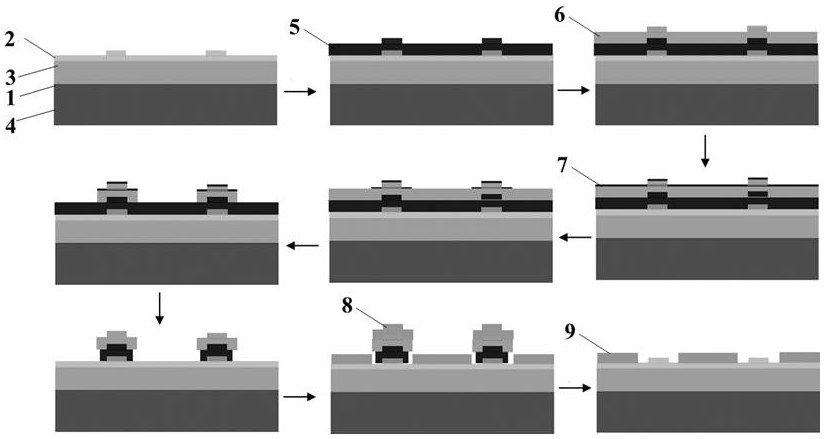

图1为本发明制备方法流程示意图;

图2和图3为利用本发明制备方法制得的集成微纳电极显微图。

具体实施方式

下面结合实施例和附图对本发明作进一步说明,但不应以此限制本发明的保护范围。

实施例1

参阅图1,本发明利用飞秒激光直写实现在铌酸锂光子芯片上制备集成微纳电极的方法,包括以下步骤:

(1)准备铌酸锂马赫-曾德尔干涉仪(MZI)芯片并在其表面镀铬膜、二氧化硅膜、铬膜:利用飞秒光刻辅助化学机械抛光的技术制备超高性能的MZI光子芯片1,所述MZI光子芯片由500nm厚铌酸锂薄膜2、4.7μm的二氧化硅层3以及0.5mm厚的单晶硅衬底4组成,于所述铌酸锂薄膜2表面上镀600nm厚铬膜层5、紧接着,再于所述铬膜层5上通过化学气相沉积的方法镀400nm厚二氧化硅膜6、然后再于所述二氧化硅膜6上磁控溅射50nm厚铬膜7;

(2)飞秒直写电极铬掩膜:将镀完三层膜后的所述MZI芯片固定于三维运动平台上,预先通过追焦系统扫描铬膜层7表面形貌,以保证在加工过程中不离焦,飞秒激光通过数值孔径0.7的物镜聚焦到所述铬膜7,结合软件编程控制下位机以及飞秒激光开关光刻写预先设计的电极铬掩膜图案;

(3)反应离子刻蚀:将所述MZI芯片放置于反应离子刻蚀机腔室中,设置刻蚀参数,将所述的400nm二氧化硅膜6完全刻蚀,所述铬掩膜7与二氧化硅膜6的深度刻蚀比为1:10至1:20左右,没有被所述铬掩膜7保护的二氧化硅膜6被刻蚀,后续用于控制电极结构线宽使用,同时在双层介质中充当顶层“屋檐”结构。

(4)湿法腐蚀底层铬膜:将刻蚀后的所述MZI芯片放置于商业铬腐蚀液中,将表面电极铬掩膜7与底层600nm厚铬膜5腐蚀干净,同时由于腐蚀的各向同性,在腐蚀底层铬膜5时除了向下腐蚀外还会向四周扩散,最终与所述二氧化硅膜6形成底切结构,便于后续剥离工艺。

(5)电子束蒸发金属电极:将湿法腐蚀后的所述MZI芯片放置于电子束蒸发设备中的腔室中,电子束蒸镀10nm钛-500nm金8,其中由于金与铌酸锂材料的粘附性不好,先镀上一层10nm钛作为金的粘附层,同时由于电子束蒸发方式镀膜方向性较好,边缘的包裹较少,后续更易于剥离;

(6)金属剥离:将镀完金属电极后的所述MZI芯片放置于商业铬腐蚀液中,同时用超声加以辅助,将剩余的底层铬膜5去除干净,同时将其上面的金属电极剥离掉,留下的金属9便是预先设计好的电极结构,即在铌酸锂光子芯片上制得集成微纳电极。

图2(a)是本发明在铌酸锂MZI光子芯片上制得的集成微纳金属电极的俯视显微图,图2(b)为图2(a)中虚线框标注位置的显微镜放大图;图3(a)是利用本发明在铌酸锂定向耦合(DC)分光芯片上制得的集成微纳金属电极的俯视显微图,图3(b)为图3(a)中虚线框标注位置的显微镜放大图;具体实施例结果表明本发明可以有效地在不同铌酸锂光子芯片上制备集成电极,并且电极均匀性较好,不存在剥离边缘毛刺问题,可高效低成本大规模应用于铌酸锂光子芯片上。