本地放大电路、数据读出方法和存储器

文献发布时间:2024-01-17 01:17:49

技术领域

本公开涉及半导体电路设计领域,特别涉及一种本地放大电路、数据读出方法和存储器。

背景技术

存储器在进行数据读出的过程中,数据依次由位线/互补位线传输至本地数据线/互补本地数据线,再传输至全局数据线/互补全局数据线,数据由本地数据线/互补本地数据线传输至全局数据线/互补全局数据线基于本地放大电路实现。

本地放大电路在进行读操作时,需要等待数据从位线/互补位线传输至本地数据线/互补本地数据线,之后在提供读使能信号,将数据进一步读出至全局数据线/互补全局数据线;若数据未完全传递到本地数据线/互补本地数据线而提供读使能信号,此时,本地数据线/互补本地数据线均为高电平,本地数据线/互补本地数据线会被同时放电,造成本地放大电路的读取错误或造成不必要的功耗损失,而列选择信号提供至读使能信号提供的时间间隔会影响存储器的性能。

因此,当下亟待设计一种信号的读出电路,以缩短列选择信号提供至读使能信号提供的时间间隔,从而优化存储器的性能。

发明内容

本公开实施例提供一种本地放大电路、数据读出方法和存储器,在数据读出阶段,缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

本公开实施例提供了一种本地放大电路,包括:写控制晶体管,被配置为,基于写使能信号,将全局数据线连接至本地数据线,并将互补全局数据线连接至互补本地数据线;列选择晶体管,被配置为,基于列选择信号,将位线连接至本地数据线,并将互补位线连接至互补本地数据线;第一控制NMOS管,栅极连接本地数据线,源极或漏极的其中一端连接全局数据线,另一端连接读控制晶体管;第二控制NMOS管,栅极连接互补本地数据线,源极或漏极的其中一端连接互补全局数据线,另一端连接读控制晶体管;预充电模块,连接本地数据线和互补本地数据线,用于将本地数据线和互补本地数据线预充电至第一预设电平,第一预设电平小于第一控制NMOS管的阈值电压,且小于第二控制NMOS管的阈值电压;读控制晶体管被配置为,基于读使能信号,将第一控制NMOS管和第二控制NMOS管与读控制晶体管相连的端子上拉/下拉至第二预设电平;第二预设电平与全局数据线和互补全局数据线的预充电电平相反。

基于本实施例提供的本地放大电路,通过预充电模块将本地数据线和互补本地数据线预充电至第一预设电平,且第一预设电平不足以开启第一控制NMOS管和第二控制NMOS管,在数据写入阶段,提供写使能信号,全局数据线和互补全局数据线上的数据传输至本地数据线和互补本地数据线,由于读控制晶体管无法导通,第一控制NMOS管和第二控制NMOS管的导通并不影响存储器的数据写入;在数据读出阶段,可以提前提供读使能信号,此时由于第一控制NMOS管和第二控制NMOS管无法导通,并不影响存储器的数据读出,当提供列选择信号后,位线和互补位线的数据被同步至本地数据线和互补本地数据线,第一控制NMOS管或第二控制NMOS管导通,从而导通相应的读出通路,将本地数据线和互补本地数据线上的数据传输至全局数据线和互补全局数据线;从而实现在数据读出阶段,缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

另外,第一预设电平为0。

另外,预充电模块包括预充电MOS管,预充电MOS管的栅极用于接收预充电信号,源极或漏极的其中一端连接本地数据线和互补本地数据线,另一端接地。

另外,全局数据线和互补全局数据线在数据读出前被预充的预充电电平为低电平,第二预设电平为高电平。

另外,全局数据线和互补全局数据线在数据读出前被预充的预充电电平为高电平,第二预设电平为低电平。

另外,写控制晶体管包括:第一写MOS管,栅极用于接收写使能信号,源极连接全局数据线,漏极连接本地数据线;第二写MOS管,栅极用于接收写使能信号,源极连接互补全局数据线,漏极连接互补本地数据线。

另外,第一写MOS管和第二写MOS管为PMOS。由于PMOS管比NMOS管的上拉能力强,第一写MOS管和第二写MOS管为PMOS管,能加速在提供读使能信号后,将本地数据线或互补本地数据线上拉至高电平。

另外,列选择晶体管包括:第一列选择MOS管,栅极用于接收列选择信号,源极连接本地数据线,漏极连接位线;第二列选择MOS管,栅极用于接收列选择信号,源极连接互补本地数据线,漏极连接互补位线。

另外,第一列选择MOS管和第二列选择MOS管为PMOS。由于PMOS管比NMOS管的上拉能力强,第一列选择晶体管和第二列选择晶体管为PMOS管,能加速在提供列选择信后,将本地数据线或互补本地数据线上拉至高电平。

另外,读控制晶体管包括:第一读MOS管,栅极用于接收读使能信号,源极连接第一控制NMOS管,漏极用于接收第一预设电平;第二读MOS管,栅极用于接收读使能信号,源极连接第二控制NMOS管,漏极用于接收第一预设电平。

本公开实施例还提供一种数据读出方法,应用于上述本地放大电路,包括:在读出阶段之前,将本地数据线和互补本地数据线预充电至第一预设电平,将全局数据线和互补全局数据线预充电至预充电电平;在读出阶段,提供读使能信号,当第一控制NMOS管导通,将全局数据线拉高/拉低至第二预设电平,当第二控制NMOS管导通,将互补全局数据线拉高/拉低至第二预设电平;提供列选择信号,将位线电平同步至本地数据线,并将互补位线电平同步至互补本地数据线;其中,读使能信号的提供时刻不迟于全局数据线或所述互补全局数据线基于列选择信号发生电位变化的时刻。

基于本实施例提供的本地放大电路,在数据读出阶段,缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

另外,读使能信号的提供时刻不迟于优先于列选择信号的提供时刻。

另外,读使能信号和列选择信号同时提供。

本公开实施例还提供一种存储器,应用上述本地放大电路进行数据的写入和读出。

另外,存储器包括:DRAM、SDRAM、DDR-SDRAM、DDR2-SDRAM、DDR3-SDRAM、DDR4-SDRAM、LPDDR4-SDRAM、DDR5-SDRAM、LPDDR5-SDRAM、GDDR5-SDRAM和GDDR6-SDRAM。

附图说明

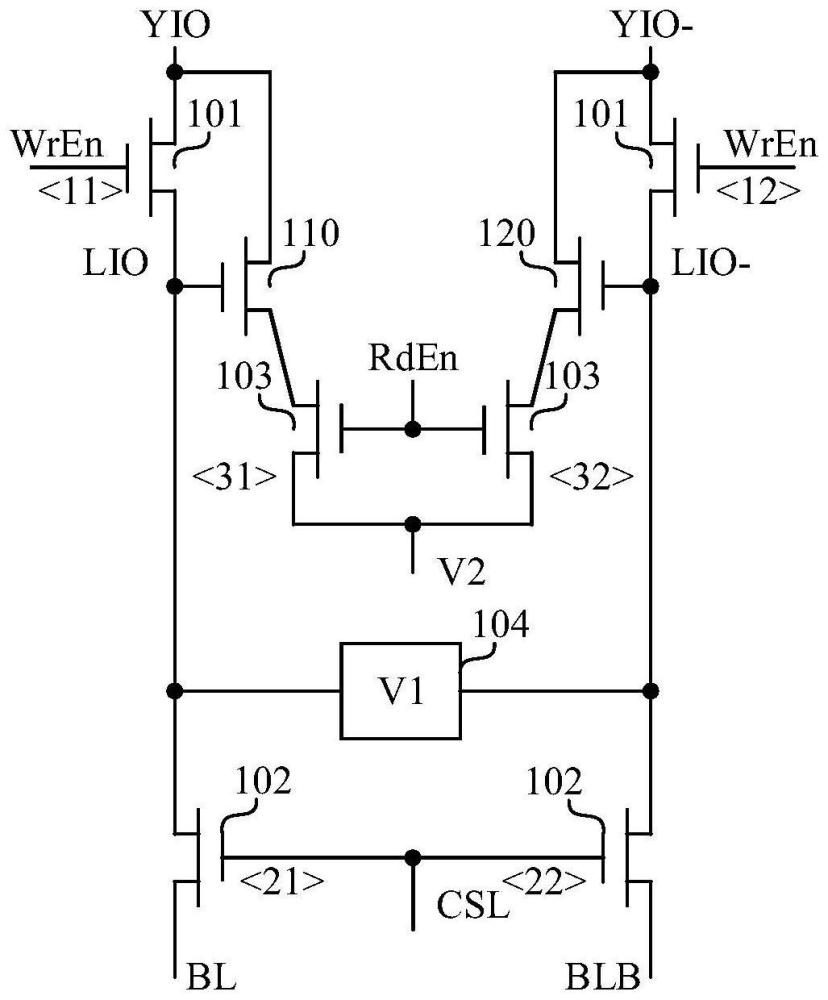

图1为本公开一实施例提供的本地放大电路的结构示意图;

图2为本公开一实施例提供的读使能信号和列选择信号的提供时序示意图;

图3和图4为本公开一实施例提供的将本地数据线/互补本地数据线上的数据读出至全局数据线/互补全局数据线时的信号提供时序示意图;

图5为本公开一实施例提供的预充电模块的结构示意图;

图6为本公开一实施例提供的另一种本地放大电路的结构示意图;

图7为本公开另一实施例提供的数据读出方法的流程示意图。

具体实施方式

存储器在进行数据读出的过程中,数据依次由位线/互补位线传输至本地数据线/互补本地数据线,再传输至全局数据线/互补全局数据线,数据由本地数据线/互补本地数据线传输至全局数据线/互补全局数据线基于本地放大电路实现。

本地放大电路在进行读操作时,需要等待数据从位线/互补位线传输至本地数据线/互补本地数据线,之后在提供读使能信号,将数据进一步读出至全局数据线/互补全局数据线;若数据未完全传递到本地数据线/互补本地数据线而提供读使能信号,此时,本地数据线/互补本地数据线均为高电平,本地数据线/互补本地数据线会被同时放电,造成本地放大电路的读取错误或造成不必要的功耗损失,而列选择信号提供至读使能信号提供的时间间隔会影响存储器的性能。

本公开实施例提供了一种本地放大电路,在数据读出阶段,缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

本领域的普通技术人员可以理解,在本公开各实施例中,为了使读者更好地理解本公开而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本公开所要求保护的技术方案。

图1为本实施例提供的本地放大电路的结构示意图,图2为本实施例提供的读使能信号和列选择信号的提供时序示意图,图3和图4为本实施例提供的将本地数据线/互补本地数据线上的数据读出至全局数据线/互补全局数据线时的信号提供时序示意图,图5为本实施例提供的预充电模块的结构示意图,图6为本实施例提供的另一种本地放大电路的结构示意图,以下结合附图对本实施例提供的本地放大电路作进一步详细说明,具体如下:

参考图1,本地放大电路,包括:

写控制晶体管101,被配置为,基于写使能信号WrEn,将全局数据线YIO连接至本地数据线LIO,并将互补全局数据线YIO-连接至互补本地数据线LIO-。

写使能信号WrEn用于导通写控制晶体管101;全局数据线YIO和互补全局数据线YIO-用于传输反相数据,即全局数据线YIO传输高电平数据,互补全局数据线YIO-传输低电平数据;全局数据线YIO传输低电平数据,互补全局数据线YIO-传输高电平数据;另外,本地数据线LIO和互补本地数据线LIO-也用于传输反相数据。

列选择晶体管102,被配置为,基于列选择信号CSL,将位线BL连接至本地数据线LIO,并将互补位线BLB连接至互补本地数据线。

列选择信号CSL用于导通列选择晶体管102;位线BL和互补位线BLB用于传输反相数据,且位线BL和互补位线BLB上连接有存储单元,当数据由本地数据线LIO向位线BL传输,或数据由互补本地数据线LIO-向互补位线BLB传输时,即存储器的数据存储阶段;当数据由位线BL向本地数据线LIO传输,或数由互补位线BLB向互补本地数据线LIO-传输时,即存储器的数据读取阶段。

第一控制NMOS管110,栅极连接本地数据线LIO,源极或漏极的其中一端连接全局数据线YIO,另一端连接读控制晶体管103。

第二控制NMOS管120,栅极连接互补本地数据线LIO-,源极或漏极的其中一端连接互补全局数据线YIO-,另一端连接读控制晶体管103。

第一控制NMOS管110通过本地数据线LIO的电平控制,当本地数据线LIO为高电平时,第一控制NMOS管110导通,读控制晶体管103中源漏的其中一个端子与全局数据线YIO连接;当本地数据线LIO为低电平时,第一控制NMOS管110断开;第二控制NMOS管120通过互补本地数据线LIO-的电平控制,当互补本地数据线LIO-为高电平时,第二控制NMOS管120导通,读控制晶体管103中源漏的其中一个端子与互补全局数据线YIO-连接;当互补本地数据线LIO-为低电平时,第二控制NMOS管120断开。

预充电模块104,连接本地数据线LIO和互补本地数据线LIO-,用于将本地数据线LIO和互补本地数据线LIO-预充电至第一预设电平V1,第一预设电平V1小于第一控制NMOS管的阈值电压,且小于第二控制NMOS管的阈值电压。

读控制晶体管103被配置为,基于读使能信号RdEn,将第一控制NMOS管和第二控制NMOS管与读控制晶体管103相连的端子上拉/下拉至第二预设电平V2,第二预设电平V2与全局数据线YIO和互补全局数据线YIO-的预充电电平相反。

读使能信号RdEn用于导通读控制晶体管103,当读控制晶体管103和第一控制NMOS管110导通时,读控制晶体管103将全局数据线YIO上拉/下拉至第二预设电平V2,当读控制晶体管103和第二控制NMOS管120导通时,读控制晶体管103将互补全局数据线YIO-上拉/下拉至第二预设电平V2,其中,第二预设电平V2与全局数据线YIO和互补全局数据线YIO-的预充电电平相反。

基于本实施例提供的本地放大电路,通过预充电模块104将本地数据线LIO和互补本地数据线LIO-预充电至第一预设电平V1,且第一预设电平V1不足以开启第一控制NMOS管110和第二控制NMOS管120,在数据写入阶段,提供写使能信号WrEn,全局数据线YIO和互补全局数据线YIO-上的数据传输至本地数据线LIO和互补本地数据线LIO-,由于读控制晶体管103无法导通,第一控制NMOS管110和第二控制NMOS管120的导通并不影响存储器的数据写入;在数据读出阶段,可以提前提供读使能信号RdEn,此时由于第一控制NMOS管110和第二控制NMOS管120无法导通,并不影响存储器的数据读出,当提供列选择信号CSL后,位线BL和互补位线BLB的数据被同步至本地数据线LIO和互补本地数据线LIO-,第一控制NMOS管110或第二控制NMOS管120导通,从而导通相应的读出通路,将本地数据线LIO和互补本地数据线LIO-上的数据传输至全局数据线YIO和互补全局数据线YIO-;从而实现在数据读出阶段,缩短列选择信号CSL和读使能信号RdEn之间的时间间隔,加快存储器的数据读出。

需要说明的是,参考图2,基于本实施例提供的本地放大电路,由于列选择信号CSL的提供至本地数据线LIO和互补本地数据线LIO-变化完毕存在t1时间的延时,仅需保证读使能信号RdEn在本地数据线LIO和互补本地数据线LIO-变化完毕前提供,同样可以加快存储器的数据读出,即在一些实施例中,读使能信号可以在t1时间段内提供。

在一些实施例中,参考图3,全局数据线YIO和互补全局数据线YIO-在数据读出前被预充的预充电电平为低电平,第二预设电平V2为高电平;此时,当读控制晶体管103和第一控制NMOS管110导通时,全局数据线YIO被上拉至高电平,当读控制晶体管103和第二控制NMOS管120导通时,互补全局数据线YIO-被上拉至高电平。

在一些实施例中,参考图4,全局数据线YIO和互补全局数据线YIO-在数据读出前被预充的预充电电平为高电平,第二预设电平V2为低电平;此时,当读控制晶体管103和第一控制NMOS管110导通时,全局数据线YIO被下拉至低电平,当读控制晶体管103和第二控制NMOS管120导通时,互补全局数据线YIO-被下拉至低电平。

在一些实施例中,第一预设电平为0,即在数据读出或数据写入阶段之前,对本地数据线LIO和互补本地数据线LIO-进行放电。

具体地,参考图5,预充电模块104包括预充电MOS管105,预充电MOS管105的栅极用于接收预充电信号PRE,源极或漏极的其中一端连接本地数据线LIO和互补本地数据线LIO-,另一端接地GND,从而实现通过预充电信号PRE控制对本地数据线LIO和互补本地数据线LIO-的放电。

在一些实施例中,继续参考图1,写控制晶体管101包括:

第一写MOS管<11>,栅极用于接收写使能信号WrEn,源极连接全局数据线YIO,漏极连接本地数据线LIO。

第二写MOS管<12>,栅极用于接收写使能信号WrEn,源极连接互补全局数据线YIO-,漏极连接互补本地数据线LIO-。

在本实施例中,第一写MOS管<11>和第二写MOS管<12>为NMOS管;由于PMOS管比NMOS管的上拉能力强,在一些实施例中,第一写MOS管<11>和第二写MOS管<12>为PMOS管,能加速在提供写使能信号WrEn后,将本地数据线LIO或互补本地数据线LIO-上拉至高电平。

在一些实施例中,继续参考图1,列选择晶体管102包括:

第一列选择晶体管<21>,栅极用于接收列选择信号CSL,源极连接本地数据线LIO,漏极连接位线BL。

第二列选择晶体管<22>,栅极用于接收列选择信号CSL,源极连接互补本地数据线LIO-,漏极连接互补位线BLB。

在本实施例中,第一列选择晶体管<21>和第二列选择晶体管<22>为NMOS管;由于PMOS管比NMOS管的上拉能力强,在一些实施例中,第一列选择晶体管<21>和第二列选择晶体管<22>为PMOS管,能加速在提供列选择信号CSL后,将本地数据线LIO或互补本地数据线LIO-上拉至高电平。

具体地,当第一写MOS管<11>和第二写MOS管<12>为PMOS管,第一列选择晶体管<21>和第二列选择晶体管<22>为PMOS管,对应的电路图参考图6。

在一些实施例中,继续参考图1,读控制晶体管103包括:

第一读MOS管<31>,栅极用于接收读使能信号RdEn,源极连接第一控制NMOS管110,漏极用于接收第一预设电平V1。

第二读MOS管<32>,栅极用于接收读使能信号RdEn,源极连接第二控制NMOS管120,漏极用于接收第一预设电平V1。

在本实施例中,第一读MOS管<31>和第二读MOS管<32>为NMOS管;由于PMOS管比NMOS管的上拉能力强,NMOS管子比PMOS管的下拉能力强,在一些实施例中,可以根据第一预设电平V1的大小灵活设置第一读MOS管<31>和第二读MOS管<32>的类型;例如,当第一预设电平V1为高电平,第一读MOS管<31>和第二读MOS管<32>为NMOS管,当第一预设电平V1为低电平,第一读MOS管<31>和第二读MOS管<32>为PMOS管。

需要说明的是,对于上述提到的各类MOS管,具体“源极”和“漏极”的连接方式,并不构成对本实施例的限定,在其他实施例中,可以采用“漏极”替换“源极”,“源极”替换“漏极”的连接方式。

需要说明的是,上述实施例所提供的监测电路中所揭露的特征,在不冲突的情况下可以任意组合,可以得到新的电路实施例。

基于本实施例提供的本地放大电路,通过预充电模块104将本地数据线LIO和互补本地数据线LIO-预充电至第一预设电平V1,且第一预设电平V1不足以开启第一控制NMOS管110和第二控制NMOS管120,在数据写入阶段,提供写使能信号WrEn,全局数据线YIO和互补全局数据线YIO-上的数据传输至本地数据线LIO和互补本地数据线LIO-,由于读控制晶体管103无法导通,第一控制NMOS管110和第二控制NMOS管120的导通并不影响存储器的数据写入;在数据读出阶段,可以提前提供读使能信号RdEn,此时由于第一控制NMOS管110和第二控制NMOS管120无法导通,并不影响存储器的数据读出,当提供列选择信号CSL后,位线BL和互补位线BLB的数据被同步至本地数据线LIO和互补本地数据线LIO-,第一控制NMOS管110或第二控制NMOS管120导通,从而导通相应的读出通路,将本地数据线LIO和互补本地数据线LIO-上的数据传输至全局数据线YIO和互补全局数据线YIO-;从而实现在数据读出阶段,缩短列选择信号CSL和读使能信号RdEn之间的时间间隔,加快存储器的数据读出。

本公开另一实施例提供一种数据读出方法,基于本实施例提供的本地放大电路,在数据读出阶段,缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

图7为本实施例提供的数据读出方法的流程示意图,以下结合附图对本实施例提供的数据读出方法作进一步详细说明,具体如下:

参考图7,数据读出方法,包括:

步骤201,将本地数据线和互补本地数据线预充电至第一预设电平,将全局数据线和互补全局数据线预充电至预充电电平。

具体地,在读出阶段之前,将本地和数据线和互补本地和数据线预充电至第一预设电平,将全局数据线和互补全局数据线预充电至预充电电平。

步骤202,提供读使能信号和列选择信号,读使能信号的提供时刻不迟于全局数据线或互补全局数据线基于列选择信号发生电位变化的时刻。

具体地,在读出阶段,提供读使能信号,当第一控制NMOS管导通,将全局数据线拉高/拉低至第二预设电平,当第二控制NMOS管导通,将互补全局数据线拉高/拉低至第二预设电平,提供列选择信号,将位线电平同步至本地数据线,并将互补位线电平同步至互补本地数据线,其中,读使能信号的提供时刻不迟于全局数据线或互补全局数据线基于列选择信号发生电位变化的时刻。

通过预充电模块将本地数据线和互补本地数据线预充电至第一预设电平,且第一预设电平不足以开启第一控制NMOS管和第二控制NMOS管,在数据写入阶段,提供写使能信号,全局数据线和互补全局数据线上的数据传输至本地数据线和互补本地数据线,由于读控制晶体管无法导通,第一控制NMOS管和第二控制NMOS管的导通并不影响存储器的数据写入;在数据读出阶段,可以提前提供读使能信号,此时由于第一控制NMOS管和第二控制NMOS管无法导通,并不影响存储器的数据读出,当提供列选择信号后,位线和互补位线的数据被同步至本地数据线和互补本地数据线,第一控制NMOS管或第二控制NMOS管导通,从而导通相应的读出通路,将本地数据线和互补本地数据线上的数据传输至全局数据线和互补全局数据线;从而实现在数据读出阶段,缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

结合图2,由于列选择信号CSL的提供至本地数据线LIO和互补本地数据线LIO-变化完毕存在t1时间的延时,仅需保证读使能信号RdEn在本地数据线LIO和互补本地数据线LIO-变化完毕前提供,同样可以加快存储器的数据读出,即在一些实施例中,读使能信号可以在t1时间段内提供;在一些实施例中,读使能信号的时刻不迟于列选择信号的提供时刻;在一些实施例中,读使能信号和列选择信号同时提供。

需要说明的是,以上数据读出方法的描述,与上述本地放大电路实施例的描述是类似的,具有同本地放大电路实施例相似的有益效果,因此不做赘述。对于本公开实施例数据读出方法中未披露的技术细节,请参照本公开实施例中本地放大电路的描述而理解。

上述各统计方法的阶段划分,只是为了描述清楚,实现时可以合并为一个统计阶段或者对某些统计阶段进行拆分,分解为多个统计阶段,只要统计方法的逻辑相同,都在本专利的保护范围内;另外,对上述统计方法中添加无关紧要的修改或者引入无关紧要的设计,但不改变上述统计方法的核心设计都在该专利的保护范围内。

本公开又一实施例提供一种存储器,应用上述实施例提供的本地放大电路进行数据的写入和读出,以缩短列选择信号和读使能信号之间的时间间隔,加快存储器的数据读出。

在一些实施例中,存储器为动态随机存取存储器DRAM芯片。

在一些实施例中,存储器为动态随机存取存储器SRAM芯片。

在一些实施例中,存储器为动态随机存取存储器SDRAM芯片,其中,动态随机存取存储器DRAM芯片的内存符合DDR内存规格。

在一些实施例中,存储器为动态随机存取存储器SDRAM芯片,其中,动态随机存取存储器DRAM芯片的内存符合DDR2内存规格。

在一些实施例中,存储器为动态随机存取存储器SDRAM芯片,其中,动态随机存取存储器DRAM芯片的内存符合DDR3内存规格。

在一些实施例中,存储器为动态随机存取存储器SDRAM芯片,其中,动态随机存取存储器DRAM芯片的内存符合DDR4或LPDDR4内存规格。

在一些实施例中,存储器为动态随机存取存储器SDRAM芯片,其中,动态随机存取存储器DRAM芯片的内存符合DDR5或LPDDR5内存规格。

在一些实施例中,存储器为动态随机存取存储器SDRAM芯片,其中,动态随机存取存储器DRAM芯片的内存符合GDDR5或GDDR6内存规格。

本领域的普通技术人员可以理解,上述各实施例是实现本公开的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本公开的精神和范围。