处理器中的写入流

文献发布时间:2023-06-19 13:46:35

技术领域

本描述大体上涉及可经形成为集成电路的一部分的处理装置,例如片上系统(SoC)。更明确来说,本描述涉及具有改进的写入操作的管理的此类系统。

背景技术

SOC是单个裸片上的具有多个功能块(例如一或多个处理器核心、存储器以及输入及输出)的集成电路。

层级式的存储器在具有针对相应处理器核心(例如中心处理单元(CPU)或数字信号处理器(DSP))的不同读取/写入响应时间的存储器块之间移动数据及指令。例如,对于相应处理器核心来说更为本地的存储器通常具有更低的响应时间。层级式的存储器包含具有多个级别(例如L1及L2)的高速缓存存储器系统,其中不同级别描述高速缓存存储器对相应的处理器核心的不同本地性程度或不同平均响应时间。在此,更本地或更低响应时间的高速缓存存储器(例如L1高速缓存)被称为比更不本地或更高响应时间的低级别高速缓存存储器(例如L2高速缓存或L3高速缓存)更高级别的高速缓存存储器。高速缓存的关联性是指高速缓存存储分离,其中组关联性将高速缓存划分为若干存储组,且每一此组存储若干(路)块,而完全关联高速缓存不受组限制的约束。因此,针对整数N,主存储器(系统存储器)中的每一位置可驻留在N路关联高速缓存中N个可能位置中的任一者中。

“受害者高速缓存”存储器高速缓存从高速缓存存储器(例如L1高速缓存)逐出的数据(例如高速缓存线)。如果L1高速缓存读取导致未命中(与主存储器的一部分对应的数据未存储在L1高速缓存中),那么在受害者高速缓存中发生查找。如果受害者高速缓存查找导致命中(与所请求的存储器地址对应的数据存在于受害者高速缓存中),那么交换产生命中的受害者高速缓存位置的内容与相应高速缓存(此实例中为L1高速缓存)中对应位置的内容。一些实例受害者高速缓存是完全关联的。与主存储器中的任何位置对应的数据可经映射到(存储在)完全关联高速缓存中的任何位置。

发明内容

在所描述的实例中,处理器系统包含产生存储器写入请求的处理器核心、高速缓存存储器及存储器控制器。所述存储器控制器具有存储器管线。所述存储器控制器经耦合以控制所述高速缓存存储器并通信地耦合到所述处理器核心。所述存储器控制器经配置以接收来自所述处理器核心的所述存储器写入请求;在所述存储器管线上调度所述存储器写入请求;及在所述存储器管线上调度所述存储器写入请求中的相应者的同时,将写入确认发送到所述处理器核心,所述写入确认证实所述相应存储器写入请求的数据有效负载到所述高速缓存存储器的写入已完成。

附图说明

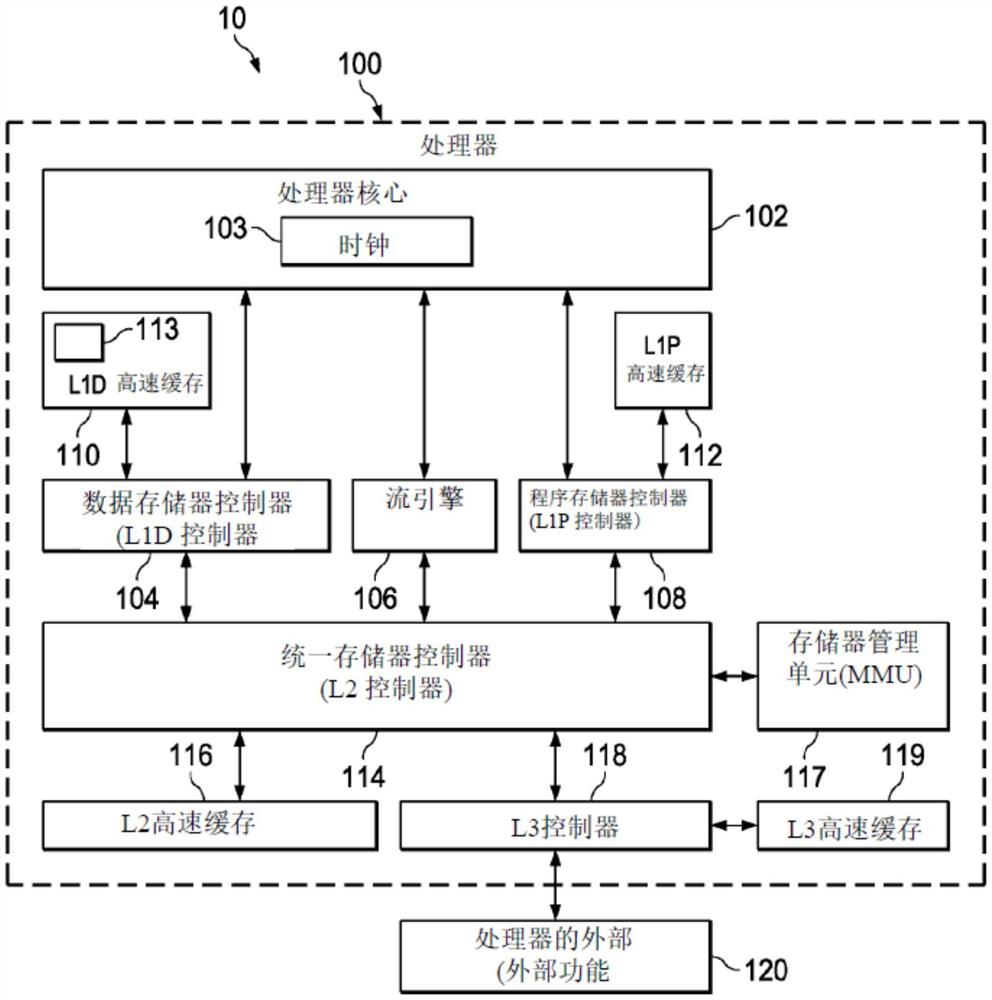

图1是作为SoC的一部分的实例处理器的框图。

图2是用于图1的SoC的实例存储器管线的框图。

图3是用于图1的SoC的存储器写入操作的过程的实例。

图4是用于图1的SoC的实例存储器管线的框图。

图5是用于图1的SoC的存储器写入操作的过程的实例。

具体实施方式

图1是作为SoC 10的一部分的实例处理器100的框图。SoC 10包含产生新数据的处理器核心102,例如CPU或DSP。处理器100可包含时钟103,时钟103可为处理器核心102的一部分,或也可与处理器核心102分离(未展示的单独的时钟)。处理器核心102还产生请求从数据存储器控制器104(DMC)及流引擎106读取的存储器读取请求以及请求写入到数据存储器控制器104(DMC)及流引擎106的存储器写入请求。在一些实施例中,处理器核心102每处理器核心时钟周期产生一个读取请求或写入请求。存储器控制器将写入确认返回到处理器核心102以证实所请求的存储器写入已执行。处理器核心102还经耦合以接收来自程序存储器控制器108(PMC)的指令。流引擎106有利于处理器核心102发送绕过DMC 104及PMC 108的某些存储器事务及其它存储器相关消息。

SoC 10具有层级式的存储器系统。每一级别处的每一高速缓存可经统一或划分为单独的数据及程序高速缓存。例如,DMC 104可经耦合到1级数据高速缓存110(L1D高速缓存)以控制到L1D高速缓存110的数据写入及从L1D高速缓存110的数据读取。类似地,PMC108可经耦合到1级程序高速缓存112(L1P高速缓存)以从L1P高速缓存112读取用于由处理器核心102执行的指令。(在此实例中,处理器核心102不产生到L1P高速缓存112的写入。)L1D高速缓存110可具有L1D受害者高速缓存113。用于二级高速缓存(L2高速缓存116,例如L2 SRAM)的统一存储器控制器114(UMC)经通信地耦合以接收来自DMC 104及PMC 108的读取及写入存储器存取请求,并接收来自流引擎106、PMC 108及存储器管理单元117(MMU)的读取请求。(实例L2控制器UMC 114在实例系统中被称为“统一”存储器控制器,因为UMC 114可在L2高速缓存116中存储指令及数据两者。)UMC 114经通信地耦合以将读取数据及写入确认(从1级高速缓存之外)传递到DMC 104、流引擎106及PMC 108,然后将其传递到处理器核心102。UMC 114还经耦合以控制到L2高速缓存116的写入及从L2高速缓存116的读取,并将存储器存取请求传递到三级高速缓存控制器118(L3控制器)。L3控制器118经耦合以控制到L3高速缓存119的写入及从L3高速缓存119的读取。UMC 114经耦合以接收(经由L3控制器118)从L2高速缓存116及L3高速缓存119读取的写入确认及数据。UMC 114经配置以控制用于程序内容及数据内容(指令的读取及写入请求、数据发射及写入确认)的存储器事务的管线化。L3控制器118经耦合以控制对L3高速缓存119的写入及从L3高速缓存119的读取,并使用外部功能120调解事务,所述外部功能120位于处理器100的外部,例如其它处理器核心、SOC 10的外围功能及/或其它SoC(且也用以控制窥探事务)。因此,L3控制器118是SoC 10的共享存储器控制器,且L3高速缓存119是SoC 10的共享高速缓存存储器。因此,与处理器100及外部功能120相关的存储器事务通过L3控制器118。

存储器事务由处理器核心102产生并向较低级别的高速缓存存储器传达,或由外部功能120产生并向较高级别的高速缓存存储器传达。例如,可由UMC 114响应于来自处理器核心102的在L2高速缓存116中产生未命中的读取事务而发起受害者写入事务。

MMU 117将地址转译及存储器属性信息提供到处理器核心102。其通过查找存储在存储器中的表中的信息来实现这一点(MMU 117与UMC 114之间的连接使MMU 117能够使用读取请求来存取含有表的存储器)。

图2是包含在图1UMC 114内的或与之相关联的实例存储器管线200的框图,因此为了说明,图2还重复来自图1的与UMC 114通信的各种块。存储器管线200包含耦合到整数M个管线库206的初始调度块202。每一管线库206包含整数P个级208,且经说明为初始调度块202下方的垂直列。DMC 104通过数目N

当处理器100的存储器控制器(例如DMC 104、流引擎106、PMC 108、MMU 117或L3控制器118)将对从由UMC 114介入的存储器(例如L2高速缓存116、L3高速缓存119或外部功能120中的存储器)的读取或写入到其的请求传达到UMC 114时,初始调度块202调度将由适当的管线库206针对特定请求处置的请求。因此,初始调度块202对读取及写入请求执行仲裁。仲裁确定哪个管线库206将接收在初始调度块202处排队的哪个存储器事务,及以什么顺序接收。通常,例如,取决于正被写入或请求的数据的存储器地址、管线库206的请求负载或伪随机函数,将读取或写入请求调度到管线库206中的对应一者中。初始调度块202通过在管线库206的第一级中选择来调度从DMC 104、流引擎106、PMC 108及L3控制器118接收的读取及写入请求。请求对L3高速缓存119(或外部功能120)执行的存储器事务在通过与L2高速缓存116对应的存储器管线200(管线库206及可能的总线窥探相关级,其未展示)之后,由L3控制器118(参见图4)中的L3高速缓存调度块404仲裁并调度到L3高速缓存管线中。

请求调度防止将由相同的管线库206处置的读取或写入请求之间的冲突,并保持存储器一致性(下文将进一步描述)。例如,请求调度维护由处理器100的不同存储器控制器或相同存储器控制器的不同总线放置到初始调度块202的存储器事务队列(存储器存取请求队列)中的存储器事务之间的顺序。

进一步来说,请求由DMC 104或PMC 108发送的管线存储器事务(读取或写入请求),因为存储器事务已通过对应的1级高速缓存管线(对于L1D高速缓存110来说在DMC 104中,且对于L1P高速缓存112来说在PMC 108中),且针对较低级别高速缓存或存储器端点(或外部功能120),或已在相应的1级高速缓存中产生未命中,或绕过L1D高速缓存110,因为写入请求的对应数据有效负载不可由L1D高速缓存110高速缓存。通常,引导到DMC 104或PMC108的产生1级高速缓存命中的存储器事务分别导致来自L1D高速缓存110的写入确认或具有从L1D高速缓存110或L1P高速缓存112读取的数据或指令的响应。因此,产生1级高速缓存命中的存储器事务通常不需要存取图2中所展示的管线库206,管线库206控制或介入对L2高速缓存116、L3高速缓存119及外部功能120的存储器存取(参见图1)。

图2中所展示的管线库206是UMC 114的一部分。L1D高速缓存110可保持由处理器核心102产生的数据。例如,外部功能120可通过将数据写入到L2高速缓存116或L3高速缓存119,或使用由L3控制器119控制并由UMC 114(L2控制器,作为代理)管理的窥探事务从L1D高速缓存110读取或逐出数据来存取L1D高速缓存110中的数据。

存储器一致性是系统中的存储器的内容(或至少被视为或指示为有效的内容)与由系统中的一或多个处理器基于读取及写入请求的有序流所期望的内容相同。防止影响特定数据的写入或特定存储器位置绕过影响相同数据或相同存储器位置的较早发出的写入或读取。此外,某些类型的事务具有优先级,例如受害者高速缓存事务及窥探事务。

总线窥探是由此高速缓存中的一致性控制器(窥探器)借以监测或窥探总线事务以保持分布式共享存储器系统(例如SoC 10)中的存储器一致性的方案。如果修改共享高速缓存块的事务出现在总线上,那么窥探器检查其相应的高速缓存是否具有共享块的相同副本。如果高速缓存具有共享块的副本,那么对应的窥探器执行动作以确保高速缓存中的存储器一致性。例如,根据总线上所检测到的事务,此操作可为刷新共享块、使共享块无效或更新共享块。

“写入流”是指装置(例如,处理器核心102)发出写入请求的流,例如每周期一个写入请求,而没有暂停。例如,写入流可能会因暂停而中断,所述暂停由于缓冲区已满或写入请求识别符数目不足而导致。致使写入请求尽可能快地从存储器事务队列中抽取的能力促进写入流。

为了使处理器核心102知晓写入已完成,其必须接收写入确认。为了保持一致性,处理器核心102可通过限制将超过限制的写入请求来自我限制到给定数目的未完成写入请求,直到接收到未完成写入请求的写入确认为止。因此,处理器核心102及L1D高速缓存110可等待写入确认(或“交握”)继续进行,同时暂停处理器核心102内的对应写入流过程。中断写入流的暂停也可由处理器核心102或DMC 104等待来自先前写入请求的写入确认导致。处理器核心102还可经配置以在等待关于某些操作(例如围栏操作)的写入确认时暂停。由DMC104(1级高速缓存110控制器)使用由UMC 114(2级高速缓存116控制器)转发的写入确认(交握)来检测较低级别高速缓存(例如L2高速缓存116或L3高速缓存119)中的写入完成。然而,由于包含仲裁、排序及一致性的各种管线要求,写入可能需要许多周期才能完成。

在由初始调度块202执行的第一级仲裁处,UMC 114(L2高速缓存116控制器,其包含初始调度块202)确定是否允许在存储器管线200中进行存储器事务,以及在哪个管线库206中进行。在(1)初始仲裁及调度与(2)写入完成之间,到L2高速缓存116的写入通常具有很少的操作。经调度的写入请求的剩余操作可包含,例如,检查错误(例如防火墙、寻址及超出范围的错误)、读取-修改-写入动作(更新写入请求的数据有效负载的错误校验码)及将写入请求的数据有效负载提交到存储器。通常,每一管线库206是独立的,使得管线库206上的写入事务(例如,从L1D高速缓存110到L2高速缓存116的数据写入)关于其它管线库206上的写入事务没有排序或一致性要求。在每一管线库内,对L2高速缓存116的写入按照其经调度的顺序进行。就引发读取-修改-写入事务的部分写入来说,维持相对排序。如果存储器事务导致寻址危险或违反排序要求,那么事务暂停,且不会被发出到管线库206。(部分写入是具有小于目的地高速缓存存储器的最小写入长度的数据有效负载的写入请求。部分写入触发读取-修改-写入事务,其中数据从目的地高速缓存存储器读取以将写入请求的数据有效负载填充到目的地高速缓存存储器的最小写入长度,且更新的错误校正码(ECC)从所产生的填充数据有效复载产生并附加到所述填充数据有效复载。具有更新的ECC的填充数据有效负载是写入到目的地高速缓存存储器的内容。)

由于存储器管线200的这些特性,一旦在管线库206内调度写入(例如,从L1D高速缓存110到L2高速缓存116的数据的写入),那么保证写入遵循所有排序要求且不违反一致性(因此,满足避免破坏排序及一致性需要满足的条件)。将写入操作提交到存储器可能需要(可变)的周期数,但在发出此写入操作之后发出的读取操作将“看到”写入操作。因此,如果读取请求数据或由写入修改的存储器位置,那么读取将检索数据的版本或由写入指定的存储器位置的内容,而不是先前的版本。写入-写入排序也被维持。L3高速缓存119写入请求还可由存储器管线200(由UMC 114)调度,使得L3高速缓存119的写入请求的有序完成得到保证。这些保证意味着可保证由存储器管线200(L2高速缓存管线)调度到管线库206中的写入请求符合排序及一致性要求,并在有限的时间量内完成。换种说法,此保证是保证将到特定地址且当前正被调度到管线库206上的写入事务将在到相同地址的先前调度的写入事务之后且在到相同地址的在后来调度的写入事务之前将其值“提交”到存储器(写入将完成并将对应的数据有效负载存储在存储器中)。这种保证可基于管线固有地是“有序的”,使得一旦命令进入管线,其就将按照其被调度的顺序写入到存储器(提交)。换句话说,管线内没有旁通路径。(处置下文所描述的旁通路径使得其不会破坏例如关于以相同存储器地址为目标的较旧事务的排序保证。)

“与……同时”在本文中界定为意味着同时或之后立即。因此,第一事件与第二事件“同时”发生可意味着两个事件在系统时钟的相同周期上发生。

UMC 114(L2控制器)将数据到L2高速缓存116或更高级别高速缓存(例如,来自L1D高速缓存110的数据)的写入的写入确认发送到DMC 104(L1控制器),同时初始调度块202(第一级仲裁)调度对应的写入请求。因此,指示写入完成的写入确认与正被调度的写入请求同时发送,而不是在存储器管线200完成对写入请求的处理之后发送。通过经调度的写入请求将按序完成并符合一致性要求的保证实现这种加速确认。UMC 114造成错觉,即写入请求是在其被调度的周期上完成的,而不是在对应数据被提交(写入)到存储器的周期上完成的。从处理器核心102或DMC 104的可观察性的角度来看,L2高速缓存116似乎在调度写入请求时立即完成了写入请求。这使DMC 104能够更快地解除处理器核心102的暂停(或防止处理器核心102暂停),且能够以更低的延迟(更快)从队列中抽取写入请求,从而改进总体性能。队列是UMC 114中的事务队列,这些事务是从相应“主控”(可将存储器事务发送到UMC114以进行排队的功能块)发送,例如DMC 104、流引擎106、PMC 108、MMU 117及L3控制器118。队列可经实施为保持阶段,其中存储器事务驻留同时等待由初始调度块202仲裁并调度到管线库206。

处理器核心102通常经配置以从存储器读取数据以对数据进行加工。这针对SoC10的其它处理器(例如处理器100)的其它处理器核心102关于可由那些其它处理器存取的存储器也成立。然而,SoC 10的其它处理器要求由处理器核心102产生的数据在数据产生处理器100外部可用以便能够存取所产生的数据。这意味着所产生的数据通过L3控制器118以便在共享存储器(L3高速缓存119)内或通过发射到外部功能120外部可存取。

图3是用于图1的SoC 10的存储器写入操作的过程300的实例。在步骤302中,初始调度块202将引导到L2高速缓存116的写入请求调度到管线库206。在步骤304中,在将写入请求调度到管线库之后,UMC 114(L2高速缓存控制器)直接将写入确认发送到处理器核心102。在步骤306中,响应于写入确认而解除处理器核心102的暂停。

图4是用于图1的SoC 10的实例存储器管线400的框图。如图4中所展示的存储器管线400与如图2中所展示的存储器管线200类似,但还包含旁通路径402。旁通路径402将初始调度块202耦合到L3高速缓存调度块404,因此跳过与高速缓存的至少一级对应的存储器管线。例如,旁通路径402使旁通写入能够绕过与L2高速缓存116相关的存储器管线400的部分,从而缩短旁通写入的总处理时间。因此,可将到某些存储器区域的写入写入到L3高速缓存119,而不是写入到L2高速缓存116(或其它较低级别高速缓存)。此类写入(旁通写入)可安全地执行,而无需存取与L2高速缓存116相关的存储器管线级,其包含管线库206及相关的总线窥探(未展示)。这简化了旁通写入的一致性要求。

为了允许旁通写入使用旁通路径402,存储器一致性施加排序要求。例如,写入不可绕过其它写入(写入-写入排序);写入不能绕过读取(读取-写入排序);写入不能绕过受害者高速缓存事务(例如,从L1D受害者高速缓存113到L1D高速缓存110的写入请求,这可由UMC 114在L1级别处通过受害者高速缓存相关写入请求的高速缓存未命中来处理);且写入不能绕过窥探响应(例如,当请求不是由高速缓存未命中引起时,与控制器请求从受害者高速缓存写入L1D高速缓存110对应的窥探响应)。受害者高速缓存事务及窥探响应具有高优先级,因为它们构成存储器同步事件。此外,L1D高速缓存110受害者通过完全管线,因为例如它们包含更新UMC 114中的内部状态。然而,直接在受害者高速缓存事务之后的旁通写入也可经优先化,从而确保旁通写入将不会被阻止或暂停(类似于滑动流)。此优先化状态仅适用于直接在受害者高速缓存事务之后的单个旁通写入,且在旁通写入被发送到L3控制器118以供进一步处理时结束。

初始调度块202可具有指定的旁通状态(或“旁通模式”),其中旁通写入可经调度以旁通路径402,而不是到完全存储器管线400(包含到管线库206)。当初始调度块202处于旁通模式时,旁通写入旁通中间级别高速缓存的整个管线,包含相关联的内部仲裁。当初始调度块202不处于旁通模式时,旁通写入通过完全存储器管线400。

图5是用于图1的SoC 10的存储器写入操作的过程500的实例。图5描述使初始调度块202进入并保持在旁通模式中的条件,使得允许旁通写入沿着图4旁通路径402继续。在步骤502中,初始调度块202确定队列中的下一存储器事务是否为旁通写入,携带数据或与保证不写入L2高速缓存116的存储器位置相关。(例如,数据有效负载太大而不适配L2高速缓存116,或含有未由L2高速缓存116存储的数据类型。)如果不是,那么根据步骤504使用正常(非旁通)处理(通过完整存储器管线400)处理下一存储器事务,且处理返回到步骤502。在步骤506中,初始调度块202确定对L1D受害者高速缓存的写入或从L1D受害者高速缓存的写入是否在管线中(在管线库206中)。如果是,那么受害者高速缓存写入作为存储器同步事件被优先化,且在步骤504中,不允许旁通写入沿着旁通路径402继续。相反,旁通写入接收正常(非旁通)处理(尽管使非旁通处理优先),且过程500返回到步骤502。在步骤508中,初始调度块202确定在管线库206(旁通写入将调度到的管线库206)中是否存在L1D写入(来自DMC 104的写入;在一些实施例中,在存储器管线200之外产生的任何写入请求)。如果是,那么在步骤510中,延迟旁通写入,直到L1D写入(对应的管线库206中的所有L1D写入;在一些实施例中,在存储器管线200之外产生的所有写入请求)从相应的管线库206中清除,(例如,相应的写入提交到存储器,或到达L3高速缓存调度块404以用于调度到L3控制器118的对应存储器管线中)。否则,在步骤512中,旁通写入进入旁通模式514,且旁通写入沿着旁通路径402发送到L3控制器118(并从那里发送到L3高速缓存119)。接下来,在步骤516中,初始调度块202检查其队列中的下一存储器事务是否为旁通写入。如果是,那么过程500通过返回到步骤512而保持在旁通模式中,且队列中的下一存储器事务(旁通写入)沿着旁通路径402发送到L3高速缓存调度404。因此,在旁通写入已满足使用旁通路径402的条件之后,按顺序排队的旁通写入也可经由旁通路径402发送到L3高速缓存调度404,而不必重新检查在步骤506及508中寻址的条件。如果初始调度块202的队列中的下一存储器事务不是旁通写入,那么在步骤518中,初始调度块202退出旁通模式,队列中的下一存储器事务接收正常(非旁通)处理,且过程500返回到步骤502。

在所描述的实施例中,修改是可能的,且在权利要求的范围内,其它实施例是可能的。

在一些实施例中,流引擎传递并返回对读取及写入请求两者的响应。

在一些实施例中,处理器可包含多个处理器核心(未展示具有多个处理器核心的实施例),其具有与在图1中所展示并关于其描述的那些类似的与DMC、流引擎及PMC的功能耦合。

在一些实施例中,实现并行读取或写入请求的总线可与不同类型的读取或写入请求对应,例如针对不同的存储器块或出于不同目的而做出。

在一些实施例中,流引擎使处理器核心能够直接与较低级别高速缓存(例如L2高速缓存)通信,跳过较高级别高速缓存(例如L1高速缓存),以避免数据同步问题。这可用来帮助保持存储器一致性。在一些此类实施例中,流引擎可经配置以仅发射读取请求,而不是发射读取及写入请求两者。

在一些实施例中,L3高速缓存或其它较低级别存储器可调度写入请求,使得可以在将写入请求调度到对应的存储器管线的同时将写入确认发送到DMC(或处理器核心或另一较低级别存储器控制器)。

在一些实施例中,不同的存储器存取管线库可具有不同数目的级。

在一些实施例中,外部功能中的处理器可存取存储在L2高速缓存中的数据;在一些此类实施例中,不保证存储在L2高速缓存中的内容与在外部功能中的其它处理器中高速缓存的内容之间的一致性。

在一些实施例中,如果所包含的数据对于较低级别的高速缓存(例如L1D高速缓存或L2高速缓存)来说太大,那么写入可为旁通写入。

在一些实施例中,如果页面属性将写入标记为与未由UMC(L2高速缓存控制器)高速缓存的装置类型存储器区域对应,那么写入可为旁通写入。

在一些实施例中,L1D高速缓存(或其它较低级别高速缓存)可高速缓存旁通写入的数据有效负载。

在一些实施例中,处理器的存储器一致性规则禁止旁通除了L1D受害者高速缓存写入及L1D写入之外的存储器事务(存储器读取请求或存储器写入请求)。

在一些实施例中,在经调度进入L3高速缓存(未展示)的存储器管线库之前,旁通路径将旁通写入跳转到最终仲裁阶段。

在一些实施例中,存储器写入永远不会引导到L2高速缓存(与旁通写入对应)的保证包含这是永远不会改变的选择,或此类到L2高速缓存的写入是不可能的保证。

在一些实施例中,存储器写入永远不会引导到L2高速缓存的保证包含L2高速缓存不具有对应数据的副本或散列。

在一些实施例中,存储器写入永远不会引导到L2高速缓存的保证可能会改变(如果保证最近未生效,那么被启动)。在此类实施例中,当一行正被写入到L2高速缓存时,新做出这个保证(例如,改变对应的模式寄存器以进行保证)可能需要刷新对应的L2高速缓存。在这种情况下,高速缓存刷新可避免现在被保证不会被写入到L2高速缓存的数据有效负载的高速缓存副本在做出保证后仍保留在L2高速缓存中。

在一些实施例中,高速缓存控制器仅响应于由处理器核心102或外部功能120发起的事务而发起存储器事务。

在一些实施例中,例如,取决于正在写入或请求的数据的存储器地址、管线库206的请求负载或伪随机函数,只能将读取或写入请求调度到管线库206中的对应一者中。

在所描述的实施例中修改是可能的,且在权利要求的范围内其它实施例是可能的。