一种高速低抖动数据同步鉴相器

文献发布时间:2023-06-19 09:27:35

技术领域

本发明涉及半导体集成电路领域,具体涉及一种高速低抖动数据同步鉴相器。

背景技术

在时钟数据恢复电路中鉴相器是其中最重要的单元之一,鉴相器的结构会限制时钟数据恢复电路的误码率与抖动容限,为了降低时钟数据恢复电路的的误码率并提高其抖动容限,需要尽可能改善鉴相器的数据接收速度与精度、降低因鉴相器结构产生的时钟及数据抖动。目前的鉴相器通常只是简单拥有数据采集和时钟比较两个过程,在数据采集时仅仅只考虑到传输数据内部存在的固有抖动因素。同时存在数据及时钟的同步精度不高等缺点。为了降低时钟数据恢复电路的误码率并提升其抖动容限,需要降低鉴相器的数据同步时间。于此同时,抖动是电路一个非常重要的指标,应设计低抖动的鉴相器来减小输入时钟和数据间的抖动。

发明内容

本发明的目的在于:针对上述存在的不足,本发明提供一种高速低抖动数据同步鉴相器。

为实现上述目的,本发明提供如下技术方案:

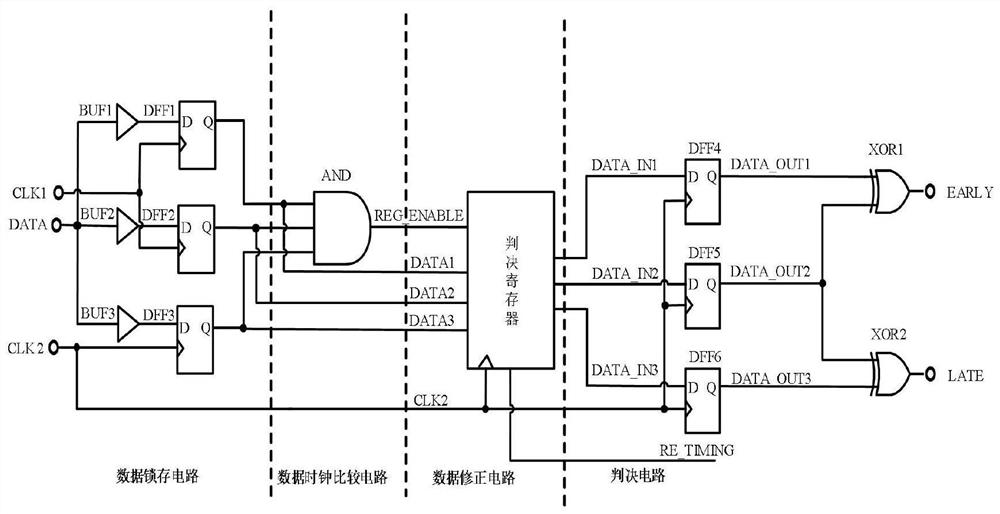

一种高速低抖动数据同步鉴相器,包括数据锁存电路、数据时钟比较电路、数据修正电路和判决电路;所述的数据锁存电路分别连接数据时钟比较电路、数据修正电路和判决电路,所述数据时钟比较电路连接数据修正电路,所述数据修正电路连接判决电路;

所述数据锁存电路包含:缓冲器BUF1、缓冲器BUF2、缓冲器BUF3、触发器DFF1、触发器DFF2、触发器DFF3、DATA端、CLK1端和CLK2端;所述CLK2端分别连接数据修正电路输入端和判决电路输入端,所述触发器DFF1、触发器DFF2和触发器DFF3的Q端分别连接数据时钟比较电路输入端和数据修正电路输入端,所述触发器DFF1、触发器DFF2和触发器DFF3的D端分别对应连接缓冲器BUF1、缓冲器BUF2和缓冲器BUF3的输出端,所述CLK1端分别连接触发器DFF1、触发器DFF2的时钟输入端,所述CLK2端连接触发器DFF3的时钟输入端,所述DATA端分别连接缓冲器BUF1、缓冲器BUF2、缓冲器BUF3的输入端。

通过缓冲器将输入数据中可能存在的毛刺和微小抖动除去;并根据加入的正交输入参考时钟利用触发器对输入数据进行锁存,完成短暂的数据锁存任务。

进一步地,所述数据时钟比较电路包含三输入与门AND;所述三输入与门AND的输出端连接数据修正电路输入端;所述三输入与门AND的三个输入端分别对应连接触发器DFF1、触发器DFF2和触发器DFF3的Q端。

通过采用三输入与门AND实现对不同数据的时钟进行时序比较和统一。

进一步地,所述数据修正电路包含判决寄存器;所述的判决寄存器的使能输入端REG_ENABLE连接数据时钟比较电路输出端,所述判决寄存器的数据输出端DATA_IN1、数据输出端DATA_IN2和数据输出端DATA_IN3分别连接判决电路输入端,所述判决寄存器的时钟输入端连接数据锁存电路,所述判决寄存器的数据输入端DATA1、数据输入端DATA2和数据输入端DATA3分别对应连接触发器DFF1、触发器DFF2和触发器DFF3的Q端,所述判决寄存器的时钟输出端输出RE_TIMING信号。

通过数据修正电路将前端锁存的数据信号与接收到的时钟信号进行校正,数据可以在输入时钟的上升沿被采集到,从而形成了最佳采样区间,减小了时钟抖动并提高了所恢复数据的精度。

进一步地,所述判决寄存器是一个带有数据选择端的先进先出存储器;利用判决寄存器实现较大位宽数据的连续存储任务,减小了时钟抖动并提高了所恢复数据的精度。

进一步地,所述判决电路包含触发器DFF4、触发器DFF5、触发器DFF6以及异或门XOR1和异或门XOR2;所述触发器DFF4、触发器DFF5和触发器DFF6的时钟输入端连接数据锁存电路,所述触发器DFF4、触发器DFF5和触发器DFF6的D端分别对应连接所述数据修正电路输出端,所述触发器DFF4的Q端连接异或门XOR1,所述触发器DFF5的Q端分别连接异或门XOR1和异或门XOR2,所述触发器DFF6的Q端连接异或门XOR2;所述异或门XOR1和异或门XOR2用于输出超前信号EARLY或滞后信号LATE。

通过将数据锁存进触发器进行判别,将电路中累积的数据和时钟的相位误差缩小到最低的水平,使数据的时序得到了极大的改善。

本发明的有益效果:本发明一种高速低抖动数据同步鉴相器内含六个数据触发器,可同时接收一组正交时钟,由时钟信号控制数据流动的速率,相比传统的鉴相器具有恢复时钟抖动小,调谐范围大,低功耗、结构简单等优点,并且可在集成电路设计中广泛应用。

附图说明

图1为本发明一种高速低抖动数据同步鉴相器总体电路图;

图2为本发明一种高速低抖动数据同步鉴相器数据传输波形图;

图3为本发明一种高速低抖动数据同步鉴相器最佳采样点示意图;

图4为本发明一种高速低抖动数据同步鉴相器数据时序调整示意图。

具体实施方式

如图1,一种高速低抖动数据同步鉴相器,包括数据锁存电路、数据时钟比较电路、数据修正电路和判决电路;所述的数据锁存电路连接数据时钟比较电路、数据修正电路和判决电路,所述数据时钟比较电路连接数据修正电路,所述数据修正电路连接判决电路。

所述数据锁存电路包含:缓冲器BUF1、缓冲器BUF2、缓冲器BUF3、触发器DFF1、触发器DFF2、触发器DFF3、DATA端、CLK1端和CLK2端;当CLK1与CLK2中存在一个时钟信号为高电平时,此时DATA端将数据DATA送入缓冲器BUF1、缓冲器BUF2、缓冲器BUF3,缓冲器BUF1、缓冲器BUF2、缓冲器BUF3将数据DATA传入对应连接的触发器DFF1、触发器DFF2、触发器DFF3的D端中,此时,通过CLK1端与CLK2端加入两组正交输入参考时钟CLK1、CLK2,分别将数据DATA锁存在不同的触发器中,等到下一时钟的上升沿到达时,触发器DFF1、触发器DFF2、触发器DFF3的Q端对应输出数据DATA1、数据DATA2、数据DATA3至数据时钟比较电路输入端,从而完成短暂的数据锁存任务。

通过缓冲器将输入数据中可能存在的毛刺和微小抖动除去;并根据加入的正交输入参考时钟利用触发器对输入数据进行锁存,完成短暂的数据锁存任务。

所述数据时钟比较电路包含三输入与门AND;触发器DFF1、触发器DFF2、触发器DFF3的Q端对应输出的数据DATA1、数据DATA2、数据DATA3通过三输入与门AND的三个输入端进入三输入与门AND中,当输出的数据DATA1、数据DATA2、数据DATA3都到达三输入与门AND的输出端,所述三输入与门AND的输出端会输出REG_ENABLE信号到数据修正电路输入端。

通过采用三输入与门AND实现对不同数据的时钟进行时序比较和统一。

所述数据修正电路包含判决寄存器;当判决寄存器的输入使能端REG_ENABLE接收到三输入与门AND的输出端输出的REG_ENABLE信号时,便将触发器DFF1的Q端、触发器DFF2的Q端、触发器DFF3的Q端对应输出的数据DATA1、数据DATA2和数据DATA3全部存入判决寄存器内;等到输入参考时钟CLK2的下一时钟的上升沿到达时,将锁存后的三路数据由判决寄存器的数据输出端DATA_IN1、数据输出端DATA_IN2和数据输出端DATA_IN3统一输出至判决电路;所述判决寄存器的时钟输出端输出RE_TIMING信号。所述判决寄存器是一个带有数据选择端的先进先出存储器;利用判决寄存器实现较大位宽数据的连续存储任务,减小了时钟抖动并提高了所恢复数据的精度。

通过数据修正电路将前端锁存的数据信号与接收到的时钟信号进行校正,数据可以在输入时钟的上升沿被采集到,从而形成了最佳采样区间,减小了时钟抖动并提高了所恢复数据的精度。

所述判决电路包含触发器DFF4、触发器DFF5、触发器DFF6以及异或门XOR1、异或门XOR2;经判决寄存器输出的数据DATA_IN1、数据DATA_IN2和数据DATA_IN3会流进入判决电路内对应触发器DFF4的D端、触发器DFF5的D端、触发器DFF6的D端;当输入参考时钟CLK2的下一时钟的上升沿来临时,统一将三路数据锁存进触发器DFF4、触发器DFF5、触发器DFF6中,随后,再经过一个时钟周期后,所述的数据DATA_IN1经触发器DFF4锁存后,通过触发器DFF4的Q端输出数据DATA_OUT1到异或门XOR1,数据DATA_IN2经触发器DFF5锁存后,通过触发器DFF5的Q端输出数据DATA_OUT2到异或门XOR1和XOR2,所述的数据DATA_IN3经触发器DFF6锁存后,通过触发器DFF6的Q端输出数据DATA_OUT3到异或门XOR2;异或门XOR1和XOR2的输出端既是判决电路的输出端,同时也是整个数据同步鉴相器的输出端。通过判断三组数据经过同一输入参考时钟CLK2后的超前滞后关系,进而产生对应的超前信号EARLY或滞后信号LATE。

通过判决电路将电路中累积的数据和时钟的相位误差缩小到最低的水平,极大的改善数据的时序。

本发明具体应用途径很多,以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以作出若干改进,这些改进也应视为本发明的保护范围。

- 一种高速低抖动数据同步鉴相器

- 一种高速低抖动的鉴频鉴相器及时钟数据恢复电路