摄像元件、摄像装置及电子设备

文献发布时间:2023-06-19 09:30:39

本发明申请是国际申请日为2016年9月27日、国际申请号为PCT/JP2016/078478、进入中国国家阶段的国家申请号为201680056855.3、发明名称为“摄像元件、摄像装置及电子设备”的发明申请的分案申请。

技术领域

本发明涉及摄像元件、摄像装置及电子设备。

背景技术

已知有如下的摄像装置:能够对从像素读出的信号按每个单位像素单元或者汇集多个像素而成的每个单元进行并行处理(专利文献1)。

现有技术文献

专利文献

专利文献1:日本国特开2012-244331号公报

发明内容

根据第1方式,摄像元件具备:读出电路,其将根据经光电转换得到的电荷生成的信号读出到信号线;保持电路,其保持基于来自电源电路的电流的电压;以及电流源,其包括晶体管,该晶体管具有与所述信号线连接的漏极部、和与所述保持电路及所述漏极部连接的栅极部,所述电源部将根据在所述保持电路保持的电压生成的电流供给到所述信号线。

根据第2方式,摄像元件具备:第1读出电路,其将根据经光电转换得到的电荷生成的第1信号读出到第1信号线;第2读出电路,其将根据经光电转换得到的电荷生成的第2信号读出到第2信号线;第1保持电路,其保持基于来自电源电路的电流的电压;第2保持电路,其保持基于来自所述电源电路的电流的电压;第1电流源,其包括第1晶体管,该第1晶体管具有与所述第1信号线连接的第1漏极部、和与所述第1保持电路及所述第1漏极部连接的第1栅极部,所述第1电流源将根据在所述第1保持电路保持的电压生成的电流供给到所述第1信号线;以及第2电流源,该第2电流源包括第2晶体管,该第2晶体管具有与所述第2信号线连接的第2漏极部、和与所述第2保持电路及所述第2漏极部连接的第2栅极部,所述第2电流源将根据在所述第2保持电路保持的电压生成的电流供给到所述第2信号线。

根据第3方式,电子设备具备:电子电路,其具有多个电子零部件;保持电路,其保持基于来自电源电路的电流的电压;以及电流源,其包括晶体管,该晶体管具有与所述电子电路连接的漏极部、和与所述保持电路及所述漏极部连接的栅极部,所述电流源将根据在所述保持电路保持的电压生成的电流供给到所述电子电路。

附图说明

图1是表示第1实施方式的摄像装置1的结构的框图。

图2是表示第1实施方式的像素10的结构的电路图。

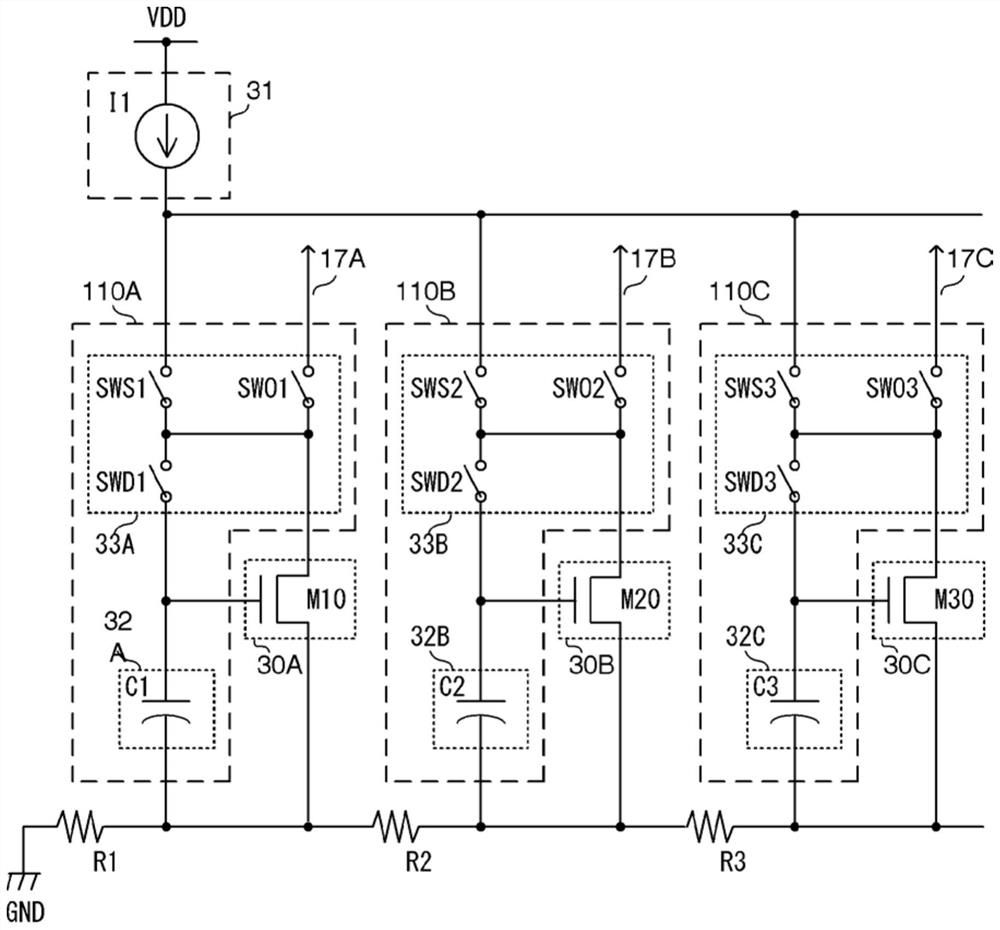

图3是表示第1实施方式的电流源30和存储电路110的结构的电路图。

图4是表示第1实施方式的控制部33的动作例的时序图。

图5是表示第1实施方式的电流源30的适用例的电路图。

图6是表示第1实施方式的电流源30的另一适用例的电路图。

图7的(a)是表示第2实施方式的像素电路150的一部分、电流源电路50和基准电流源电路31的电路图。图7的(b)是表示第2实施方式的像素电路150的一部分、电流源电路50和基准电流源电路31的连接关系的图。

图8是表示第3实施方式的电流源30和存储电路110的结构的电路图。

图9的(a)是表示变形例1的电流源电路50和其周边电路的结构的图。图9的(b)及(c)是表示变形例1的电流源电路50和其周边电路的动作例的时序图。

图10的(a)是表示变形例2的电流源电路50和其周边电路的结构的图。图10的(b)及(c)是表示变形例2的电流源电路50和其周边电路的动作例的时序图。

图11的(a)是表示变形例3的电流源电路50和其周边电路的结构的图。图11的(b)是表示变形例3的电流源电路50和其周边电路的动作例的时序图。

图12的(a)是表示变形例4的电流源电路50和其周边电路的结构的图。图12的(b)是表示变形例4的像素10的一部分的结构例的图。图12的(c)是表示变形例4的电流源电路50和其周边电路的动作例的时序图。

图13的(a)-(d)是表示变形例5的电流源30和其周边电路的结构的图。

图14的(a)-(c)是表示变形例5的电流源30和其周边电路的动作例的时序图。

具体实施方式

(第1实施方式)

图1是表示第1实施方式的摄像装置1的结构的框图。摄像装置1具备:光学系统2、摄像元件3以及控制部4。光学系统2向摄像元件3射出来自被摄体的光。摄像元件3对从光学系统2射出的光进行拍摄而例如生成图像数据。控制部4对从摄像元件3输出的图像数据进行各种图像处理。另外,控制部4将用于对摄像元件3的动作进行控制的控制信号输出到摄像元件3。此外,光学系统2也可以相对于摄像装置1能够装拆。

图2是表示第1实施方式的像素10的结构的电路图。摄像元件3具有多个像素10。像素10具有光电转换部12及读出电路100。光电转换部12在摄像元件3的拍摄区域例如配置成矩阵状。光电转换部12具有将入射的光转换为电荷的光电转换功能。光电转换部12蓄存经光电转换得到的电荷。光电转换部12例如由光电二极管构成。读出电路100将根据由光电转换部12光电转换得到的电荷所生成的像素信号读出到信号线17。像素信号例如构成图像数据。读出电路100具有转送部13、排出部14、浮置扩散部15和输出部16。

转送部13将由光电转换部12光电转换得到的电荷转送到浮置扩散部15。即,转送部13在光电转换部12与浮置扩散部15之间形成电荷转送路径。输出部16将根据转送部13从光电转换部12转送到浮置扩散部15的电荷所生成的像素信号输出到信号线17。输出部16是漏极端子、栅极端子及源极端子分别与电源VDD、浮置扩散部15及信号线17连接的晶体管。排出部14排出浮置扩散部15的电荷。浮置扩散部15通过由排出部14排出电荷而重置为基准电位。

电流源30通过信号线17与读出电路100连接。电流源30供给用于供读出电路100读出由光电转换部12光电转换得到的电荷所生成的像素信号的电流。电流源30具体而言是漏极端子、栅极端子及源极端子分别与信号线17、基准电流源电路31及接地(GND)连接的晶体管。电流源30向读出电路100的输出部16供给电流。即,输出部16将电流源30作为负载电流源而构成源极跟随器电路。电流源30基于来自基准电流源电路31的电流生成供给到信号线17的电流。另外,电流源30的漏极端子和栅极端子经由开关连接。

图3是表示第1实施方式的电流源30和存储电路(也称为保持电路)110的结构的电路图,存储电路110用于生成由电流源30供给到信号线17的电流。在图3所示的例子中,为了简化说明,电流源30仅图示了3个(电流源30A-电流源30C)。

基准电流源电路31具有基准电流源I1。基准电流源I1与电源VDD连接,输出基准电流i1。电流源30将与从基准电流源I1输出的基准电流i1相应的电流供给到信号线17。

存储电路110具有存储部32和控制部33。存储电路110(存储电路110A-存储电路110C)存储基于从基准电流源I1输出的基准电流i1的电压。存储电路110通过存储部32存储(保持)基于从基准电流源I1输出的基准电流i1的电压。存储部32与电流源30的栅极端子连接,将存储(保持)的电压供给到电流源30。

电流源30将基于在存储部32存储的电压的电流供给到信号线17。存储部32例如由一个电极与电流源30的栅极端子连接、另一个电极接地的电容器等电容元件构成。存储部32(存储部32A-存储部32C)在图3所示的例子中分别由电容器C1-电容器C3构成。

控制部33对从基准电流源电路31向存储部32供给的电流进行控制。例如,在使存储部32A存储基于从基准电流源I1输出的电流的电压的情况下,以使从基准电流源I1向存储部32B及存储部32C供给的电流比从基准电流源I1向存储部32A供给的电流小的方式进行控制。

控制部33例如由连接基准电流源电路31和存储部32的开关构成。控制部33(控制部33A-控制部33C)分别具有开关SWS(SWS1-SWS3)、开关SWD(SWD1-SWD3)和开关SWO(SWO1-SWO3)。

开关SWS(SWS1-SWS3)、开关SWD(SWD1-SWD3)及开关SWO(SWO1-SWO3)例如分别由晶体管构成。开关SWS(SWS1-SWS3)、开关SWD(SWD1-SWD3)及开关SWO(SWO1-SWO3)通过由未图示的控制电路输出的控制信号而被控制。此外,电阻R1-电阻R3是接地的布线的布线电阻。

图4是表示第1实施方式的控制部33的动作例的时序图。图4中,SWS1-SWS3、SWD1-SWD3、SWO1-SWO3分别表示从未图示的控制电路向开关SWS(SWS1-SWS3)、开关SWD(SWD1-SWD3)及开关SWO(SWO1-SWO3)输入的控制信号。另外,纵轴表示从未图示的控制电路输出的控制信号的电压电平,横轴表示时刻。开关SWS(SWS1-SWS3)、开关SWD(SWD1-SWD3)及开关SWO(SWO1-SWO3)在所输入的控制信号为高电平的情况下接通,在为低电平的情况下断开。

在时刻t1,SWS1及SWD1成为高电平。开关SWD1被接通,由此电流源30A的栅极端子和漏极端子连接。由此,电流源30A成为二极管方式连接。而且,通过使开关SWS1接通,基准电流源I1与电流源30A及存储部32A之间连接。由此,向电流源30A及存储部32A供给来自基准电流源I1的基准电流i1。

电流源30A的栅极源极间电压Vgs成为基于基准电流i1及电流源30A的阈值电压Vth1的值。向电流源30A的栅极端子施加的电压Vg1成为与电流源30A的栅极源极间电压Vgs相应的值,成为基于基准电流i1和电流源30A的阈值电压Vth1的电压。存储部32A根据基准电流i1而存储电压Vg1。

在时刻t2,SWD1成为低电平。开关SWD1断开,由此基准电流源I1与存储部32A之间的连接被解除。在存储部32A存储电流源30A的栅极源极间电压Vgs。通过使开关SWD1先于开关SWS1断开,能够防止经由电流源30A使存储在存储部32A中的电压Vg1下降。

在时刻t3,SWS1成为低电平。开关SWS1断开,由此基准电流源I1与电流源30A之间的连接被解除。以下,同样地,通过使开关SWS2及开关SWD2接通,基准电流源I1与电流源30B及存储部32B之间连接。由此,向电流源30B及存储部32B供给来自基准电流源I1的基准电流i1。在时刻t4-时刻t5,开关SWD2及开关SWS2分别成为低电平。使开关SWD2及开关SWS2分别断开,由此基准电流源I1与存储部32B之间的连接被解除。在存储部32B存储电流源30B的栅极源极间电压Vgs。

在时刻t5,SWS3及SWD3成为高电平。开关SWS3及开关SWD3接通,由此基准电流源I1与电流源30C及存储部32C之间连接。由此,向电流源30C及存储部32C供给来自基准电流源I1的基准电流i1。在时刻t6-时刻t7,开关SWD3及开关SWS3分别成为低电平。开关SWD3及开关SWS3分别断开,由此基准电流源I1与存储部32C之间的连接被解除。在存储部32C存储电流源30C的栅极源极间电压Vgs。

在时刻t8,SWO1-SWO3成为高电平。开关SWO1-开关SWO3接通,由此电流源30A-电流源30C向信号线17A-信号线17C供给基于向各自的栅极端子施加的电压Vg1-电压Vg3的电流。

图5是表示第1实施方式的电流源30的适用例的电路图。电流源30A-30C分别经由信号线17向读出电路100A-100C的输出部16供给电流。

电流源30A-电流源30C通过控制部33A-控制部33C而被供给来自基准电流源I1的基准电流。电流源30A-电流源30C通过控制部33A-控制部33C的开关SWS1-开关SWS3、开关SWD1-开关SWD3及开关SWO1-开关SWO3按照电流源30A、电流源30B及电流源30C的顺序向电流源30A、电流源30B及电流源30C供给基准电流i1。由此,在存储部32A-存储部32C存储基于来自基准电流源I1的基准电流i1的电压。即,在存储部32A-存储部32C分别存储基于基准电流i1和电流源30A-电流源30C的阈值电压Vth1-阈值电压Vth3的电压Vg1-Vg3。

电流源30A-电流源30C将基于分别在存储部32A-存储部32C存储的、来自基准电流源I1的基准电流i1的电压所生成的电流供给到信号线17A-信号线17C。即,电流源30A-电流源30C将基于分别在存储部32A-存储部32C存储的、来自基准电流源I1的基准电流i1的电压Vg1-电压Vg3所生成的电流分别供给到读出电路100A-读出电路100C的各输出部16。

图6是表示第1实施方式的电流源30的其他适用例的电路图。图5中示出了电流源30A-电流源30C分别向读出电路100供给电流的适用例,但不限于此。图6中示出了比较器电路21A-比较器电路21C向电流源的适用例,该比较器电路21A-比较器电路21C与图5所示的信号线17A-信号线17C连接、且构成将由读出电路100读出的像素信号转换为数字信号的模拟/数字转换电路的一部分。

电流源30A-电流源30C分别向比较器电路21A-比较器电路21C供给电流。在图6所示的例子中,电流源30A-30C由PMOS晶体管M10-M30构成。比较器电路21构成为例如包含晶体管M6-M9。晶体管M6及M7共同地连接源极端子而构成差动对。晶体管M8及M9作为有源负载部发挥功能。从图5所示的信号线17A-17C直接或经由电容器等向晶体管M6及M7的一方的栅极端子输入像素信号,直接或经由电容器等向另一方的栅极端子输入基准信号。电流源30A-30C向晶体管M6及M7的源极端子供给电流,作为比较器电路21的尾电流源而发挥功能。

比较器电路21将对像素信号和基准信号进行比较而生成的输出信号向锁存电路输出。锁存电路基于比较器电路21的输出信号保持与开始比较时起的经过时间相应的计数值。

电流源30A-电流源30C通过控制部33A-控制部33C而供给来自基准电流源I1的基准电流。电流源30A-电流源30C通过控制部33A-控制部33C的开关SWS1-开关SWS3、开关SWD1-开关SWD3及开关SWO1-开关SWO3按照电流源30A、电流源30B及电流源30C的顺序向电流源30A、电流源30B及电流源30C供给基准电流i1。由此,在存储部32A-存储部32C存储基于来自基准电流源I1的基准电流i1的电压。即,在存储部32A-存储部32C分别存储基于基准电流i1和电流源30A-电流源30C的阈值电压Vth1-阈值电压Vth3的电压Vg1-Vg3。

电流源30A-电流源30C将基于分别在存储部32A-存储部32C存储的、来自基准电流源I1的基准电流i1的电压所生成的电流供给到比较器电路21A-比较器电路21C。即,电流源30A-电流源30C将基于分别存储在存储部32A-存储部32C的、来自基准电流源I1的基准电流i1的电压Vg1-电压Vg3所生成的电流分别供给到比较器电路21A-比较器电路21C。

上述实施方式中,示出了摄像元件3中包含的像素信号的读出电路100和将像素信号转换为数字信号的模拟/数字转换电路的比较器电路21的电流源,但不限于此。电流源30也能够适用为摄像元件3中包含的电子电路以外的其他源极跟随器电路的电流源。而且,电流源30还能够适用于源极跟随器电路以外的电子电路。

根据上述实施方式,能够得到如下的作用效果。

(1)摄像元件3具备:读出电路100,其将根据经光电转换得到的电荷所生成的信号读出到信号线17;存储电路110,其存储基于来自基准电流源I1的电流i1的电压;以及电流源30,其是将用于通过读出电路100读出信号的电流供给到信号线17的电流源,且将根据存储在存储电路110中的电压生成的电流供给到信号线17。在第1实施方式中,电流源30将根据存储在存储电路110中的电压所生成的电流供给到信号线17。因此,能够减小IR降的影响。

(2)在第1实施方式中,在使开关SWO断开之后,电流源30生成基于存储在存储部32中的电压的电流。由电流源30生成的电流经由布线电阻(R1-R3)而流到大地。在接地布线生成基于电流与电阻的IR积的电压下降(IR降),致使电流源30的源极电压上升。由于存储部32保持着电流源30的栅极源极间的相对电压,因此伴随着电流源30的源极电压上升而电压Vg上升,从而抑制了栅极源极间电压的变动。由于抑制了栅极源极间电压的变动,因此能够抑制通过电流源30供给的电流的变动。

(3)电流源30具有晶体管,该晶体管包括与信号线17连接的漏极部、与存储电路110及漏极部连接的栅极部。因此,存储电路110能够存储基于晶体管的阈值电压Vth和基准电流i1的电压。另外,电流源30能够供给因阈值电压Vth波动所带来的影响小的电流。

(4)摄像元件3具备:第1读出电路100A,其将根据经光电转换得到的电荷生成的第1信号读出到第1信号线17A;第2读出电路100B,其将根据经光电转换得到的电荷生成的第2信号读出到第2信号线17B;第1存储电路110A,其存储基于来自基准电流源I1的电流i1的电压;第2存储电路110B,其存储基于来自基准电流源I1的电流i1的电压;第1电流源30A,其是将用于由第1读出电路100A读出第1信号的电流供给到第1信号线17A的电流源,将根据存储在第1存储电路110A中的电压生成的电流供给到第1信号线17A;以及第2电流源30B,其是将用于由第2读出电路100B读出第2信号的电流供给到第2信号线17B的电流源,将根据存储在第2存储电路110B中的电压生成的电流供给到第2信号线17B。在第1实施方式中,第1电流源30A将根据存储在第1存储电路110A中的电压生成的电流供给到信号线17A,第2电流源30B将根据存储在第2存储电路110B中的电压生成的电流供给到信号线17B。因此,能够在多条信号线中减小IR降的影响。

(5)在第1存储电路110A中存储了基于来自基准电流源I1的电流i1的电压之后,第2存储电路110B存储基于来自基准电流源I1的电流i1的电压。因此,能够按顺序将基于来自基准电流源I1的电流i1的电压存储到多个存储电路110。

(6)第1存储电路110A具有第1控制部33A,该第1控制部33A进行控制,以使得与没有通过第1读出电路100A将第1信号读出到第1信号线17A时相比,在通过第1读出电路100A将第1信号读出到第1信号线17A时来自基准电流源I1的电流i1更小,第2存储电路110B具有第2控制部33B,该第2控制部33B进行控制,以使得与没有通过第2读出电路100B将第2信号读出到第2信号线17B时相比,通过第2读出电路100B将第2信号读出到第2信号线17B时来自基准电流源I1的电流i1更小。由此,读出电路100能够基于在存储电路110存储的电压所生成的电流来将像素信号读出到信号线17。另外,通过调整成使来自基准电流源I1的电流i1减小,能够降低耗电。

(7)第1电流源30A具有第1晶体管M10,该第1晶体管M10包括:与第1信号线17A连接的第1漏极部、和与第1存储电路110A及第1漏极部连接的第1栅极部,第2电流源30B具有第2晶体管M20,该第2晶体管M20包括与第2信号线17B连接的第2漏极部、和与第2存储电路110B及第2漏极部连接的第2栅极部。由此,存储电路110A能够存储基于晶体管M10的阈值电压Vth1和基准电流i1的电压,存储电路110B能够存储基于晶体管M20的阈值电压Vth2和基准电流i1的电压。另外,第1电流源30A及第2电流源30B能够供给由阈值电压Vth波动所带来的影响小的电流。

(第2实施方式)

参照图7,说明第2实施方式的摄像元件3。此外,图中,对与第1实施方式相同或相当的部分标注相同的附图标记,主要说明不同点。第2实施方式中,还具备电流源电路50,该电流源电路50具有:第1存储部32,其存储基于来自基准电流源I1的电流i1的电压;和供给部130,其供给根据在第1存储部32存储的电压生成的电流,电流源30根据来自电流源电路50的电流生成供给到读出电路100的电流。

图7的(a)是表示第2实施方式的像素电路150的一部分、电流源电路50和基准电流源电路31的电路图。图7的(b)是表示第2实施方式的像素电路150的一部分、电流源电路50和基准电流源电路3的连接关系的图。

在图7的(b)所示的例子中,示出了8行×10列的像素电路150。各像素电路150构成为包括像素10和按每个像素10配置的电流源30及存储电路110。多个像素电路150的数量与摄像元件3的像素10的数量相同。多个电流源电路50的数量与摄像元件3的像素电路150的列数相同。另外,多个电流源电路50的数量也可以多于摄像元件3的像素电路150的列数。例如,可以与2行×10列的像素电路150为相同数量。在图7的(b)中,像素电路150的列数为10,因此电流源电路50的数量示出为10(电流源电路50a-50j)。如图7的(a)所示,各电流源电路50包括供给部130、第1存储部32和开关SWS1、SWD1、SWO1。向各电流源电路50供给来自基准电流源电路31的基准电流源I1的基准电流i1。这样的多个电流源电路50及基准电流源电路31的结构与图3所示的电流源30及其周边电路的结构相同。此外,控制部33也可以由开关SWS1、开关SWD1、开关SWO1、开关SWS2、开关SWD2和开关SWO2构成。另外,存储电路110也可以由第1存储部32、第2存储部132、控制部33和供给部130构成。

接下来,对电流源电路50与像素电路150之间的连接关系进行说明。在图7的(b)中,位于左端的电流源电路50a与位于左端的多个像素电路150a1、150a2、150a3、150a4、150a5、150a6、150a7、150a8连接。即,左端的电流源电路50a与左端列的多个像素电路150的每一个连接。同样地,左端列的电流源电路50a的相邻的电流源电路50b与左端列的像素电路150a1-150a8的相邻列的多个像素电路150b1-150b8的每一个连接。以下同样地,位于右端的电流源电路50j与右端列的多个像素电路150j1、150j2、150j3、150j4、150j5、150j6、150j7、150j8连接。

如图7的(a)所示,电流源电路50与像素电路150之间的连接通过将像素电路150的开关SWS2和电流源电路50的开关SWO1连接来进行。通过该连接,像素电路150的第2存储部132的电容器C1经由开关SWD2、SWS2及开关SWO1与电流源电路50的供给部130连接。

图7的(b)所示的多个电流源电路50通过开关SWS1及SWD1的接通断开控制而例如从左端的电流源电路50a朝向右端的电流源电路50j依次将基于来自基准电流源I1的基准电流i1的电压存储到第1存储部32的电容器C1。此外,这些开关SWS1及SWD1的接通断开控制与图4所示的开关SWS1及SWD1的接通断开控制、开关SWS2及SWD2的接通断开控制和开关SWS3及SWD3的接通断开控制同样地进行。

当在所有的电流源电路50a-50j中基于基准电流i1的电压的存储结束后,所有的电流源电路50a-50j的开关SWO1与图4所示的开关SWO1-SWO3同样地同时接通。通过该开关SWO1,所有的电流源电路50a-50j的供给部130成为能够将基于基准电流i1的电流向像素电路150a-150j供给的状态。供给部130供给根据存储在第1存储部32中的电压所生成的电流。来自该电流源电路50的电流为与来自基准电流源I1的基准电流i1相同的电流、或大致相同的电流。像这样,各电流源电路50a-50j能够生成基于基准电流源I1的基准电流i1的电流,并供给到像素电路150a-150j。

接着,最下行的多个像素电路150a1-150j1的所有开关SWS2、SWD2同时接通。通过该接通,在最下行的多个像素电路150a1-150j1,第2存储部132的电容器C1根据来自各电流源电路50a-50j的供给部130的电流在第2存储部132存储电压。像这样,最下行的多个像素电路150a1-150j1的第2存储部132同时存储分别基于来自多个电流源电路50a-50j的电流的电压。

之后,下数第2行的多个像素电路150a2-150j2所有的开关SWS2、SWD2同时接通,根据各电流源电路50a-50j的电流同时存储第2存储部132的电压。以下同样地,在最上行的多个像素电路150a8-150j8的第2存储部132同时存储分别基于来自电流源电路50a-50j的电流的电压。在第2存储部132存储了电压之后,通过使开关SWO2接通,电流源30将基于在第2存储部132存储的电压的电流供给到信号线17。

此外,也可以是,存储电路110在通过读出电路100将信号读出到信号线17时,将基于来自基准电流源I1的基准电流i1的电压存储到第1存储部32。存储电路110例如在使开关SWS2及SWD2断开并且使开关SWO2接通而通过读出电路100将信号读出到信号线17时,使开关SWS1及SWD1接通而从基准电流源I1向第1存储部32供给基准电流i1。第1存储部32被供给基准电流i1,由此存储基于基准电流i1的电压。

在上述实施方式中,示出了摄像元件3中包含的像素信号的读出电路100的电流源,但不限于此。电流源30也能够适用为将像素信号转换为数字信号的模拟/数字转换电路的比较器电路21的电流源、摄像元件3中包含的电子电路以外的其他源极跟随器电路的电流源。而且,电流源30还能够适用于源极跟随器电路以外的电子电路。

根据上述实施方式,除了与第1实施方式相同的作用效果以外,还能够得到以下的作用效果。

(8)存储电路110具有:第1存储部32,其存储基于来自基准电流源I1的电流i1的电压;供给部130,其供给根据在第1存储部32存储的电压生成的电流;以及第2存储部132,其存储基于从供给部130供给的电流的电压,电流源30将根据存储在第2存储部132中的电压生成的电流供给到信号线17。由此,能够基于基准电流源I1的基准电流i1使供给部130生成电流,基于来自供给部130的电流使电流源30生成电流。

(9)存储电路110具有设置在供给部130及第2存储部132之间的控制部33,该控制部33进行控制,以使得与没有通过读出电路100将信号读出到信号线17时相比,在通过读出电路100将信号读出到信号线17时从基准电流源I1流到第1存储部32的电流更小。由此,读出电路100能够基于根据存储在存储电路110中的电压所生成的电流,将像素信号读出到信号线17。另外,能够通过调整为使来自基准电流源I1的电流i1减小来降低耗电。

(第3实施方式)

图8是表示第3实施方式的电流源30和存储电路110的结构的电路图。此外,图中,对与第1实施方式相同或相当的部分标注相同的附图标记,主要说明不同点。在图3所示的第1实施方式中对如下例子进行了说明:基准电流源电路31的基准电流源I1依次向存储电路110A-110C供给基准电流i1,并存储基于电流源30A-30C的阈值电压和基准电流i1的电压。与之相对,在第3实施方式中,基准电流源电路31的基准电流源I1向基准电压生成部60供给基准电流i1并生成基准电压Vb,且将基准电压Vb公用地存储到各存储电路110A-110C。

在第3实施方式中,基准电流源电路31在基准电流源I1的基础上还具备基准电压生成部60。基准电压生成部60构成为例如包含晶体管M70,并基于由基准电流源I1供给的基准电流i1和基准电压生成部60的阈值电压来生成基准电压Vb。第3实施方式的控制部33A-33C构成为分别包含开关SWS1-SWS3、开关SWO1-SWO3。

存储部32A及开关SWS1、存储部32B及开关SWS2、存储部32C及开关SWS3分别并联地连接于基准电压生成部60。在使开关SWS1-SWS3同时接通时,在存储部32A-32C中存储基准电压Vb。

如此,在第3实施方式中,由于使通过基准电压生成部60生成的基准电压Vb公用地存储于各存储部32A-32C,因此能够使开关SWS1-SWS3同时接通来存储基准电压Vb。

在使开关SWS1-SWS3断开时,分别构成存储部32A-32C的电容器C1-C3保持基准电压Vb。在使开关SWO1-SWO3接通时,电流源30A-30C分别基于存储在存储部32A-32C中的基准电压Vb生成电流,向作为供给目的地的读出电路100供给电流。

在上述实施方式中,示出了摄像元件3中包含的像素信号的读出电路100的电流源,但不限于此。电流源30也能够适用为将像素信号转换为数字信号的模拟/数字转换电路的比较器电路21的电流源、摄像元件3中包含的电子电路以外的其他源极跟随器电路的电流源。而且,电流源30也能够适用于源极跟随器电路以外的电子电路。

根据上述实施方式,除了与第1实施方式相同的作用效果,还能够得到如下的作用效果。

(10)在第3实施方式中,摄像元件3还具备基于基准电流i1生成基准电压Vb的基准电压生成部60。由此,能够使多个存储电路110A-110C同时存储基于基准电流i1的基准电压Vb。

以下的变形也在本发明的范围内,还能够将变形例的一个或多个与上述实施方式组合。

(变形例1)

图9的(a)是表示变形例1的电流源电路50和其周边电路的结构的图。变形例1的摄像元件3还具备预充电部70和开关SWSr。变形例1的电流源电路50(50A-50C)分别由与图3所示的电流源30A-30C及存储部32A-32C相同的电流源及存储部构成。

预充电部70构成为包含二极管方式连接的晶体管M80。电流源电路50A、电流源电路50B和电流源电路50C并列连接于预充电部70及开关SWSr。预充电部70在向各电流源电路50A-50C供给基准电流i1之前,经由开关SWSr将预充电电压供给到图9的(a)所示的节点80。

图9的(b)是表示变形例1的电流源电路50和其周边电路的动作例的时序图。此外,虽省略图示,但开关SWD1-开关SWD3分别与开关SWS1-开关SWS3同时接通而比开关SWS1-开关SWS3先断开。

在时刻t1,开关SWSr通过使其控制信号成为高电平而接通,向预充电部70供给基准电流i1。预充电部70的栅极源极间电压Vgs成为基于基准电流i1和预充电部70的阈值电压的规定值。预充电部70的栅极源极间电压Vgs作为预充电电压而被设定到节点80。

在时刻t2,开关SWSr的控制信号成为低电平,开关SWS1的控制信号成为高电平。开关SWS1接通,由此经由节点80向电流源电路50A供给基准电流i1,通过电流源电路50A的存储部32A存储电压。

在供给基准电流i1之前对节点80设定预充电电压,由此电流源电路50A的存储部32A根据预充电电压电平存储电压,因此能够缩短达到基于基准电流i1的电压为止的时间。

在时刻t3到时刻t5,使电流源电路50B-50C依次存储基于基准电流i1的电压。在时刻t6,使SWO1-SWO3接通,由此各电流源电路50将基于基准电流i1的电流供给到读出电路100。

图9的(c)是表示变形例1的电流源电路50和其周边电路的动作例的时序图。在上述图9的(b)中,开关SWS1-SWS3依次断开之后,才使开关SWO1-SWO3同时接通,但在图9的(c)所示的例子中,在开关SWS1的接通结束后立即使开关SWO1接通,同样地,在开关SWS2、SWS3的接通结束后立即分别使开关SWO2、SWO3接通。

此外,在第1及第2实施方式中,对使SWO1-SWO3同时接通的例子进行了说明,但也可以与图9的(c)所示的例子同样地,使SWO1-SWO3依次接通。

(变形例2)

图10的(a)是表示变形例2的电流源电路50和其周边电路的结构的图。在变形例2的摄像元件3中,相对于变形例1还具备开关SWX。

输入到基准电流源I1的EN信号是对基于基准电流源I1的基准电流i1的生成进行控制的信号。基准电流源I1在EN信号为高电平的情况下生成基准电流i1,在EN信号为低电平的情况下不生成基准电流i1。

图10的(b)是表示变形例2的电流源电路50和其周边电路的动作例的时序图。此外,虽省略图示,但开关SWD1-开关SWD3分别与开关SWS1-开关SWS3同时接通,并先于开关SWS1-开关SWS3断开。

在时刻t1,EN信号及开关SWX的控制信号成为高电平,开关SWSr的控制信号成为高电平。由于EN信号为高电平,由此成为基准电流源I1能够输出基准电流i1的状态。通过使开关SWX及开关SWSr接通,使预充电部70与基准电流源电路31之间连接。预充电部70生成基于基准电流i1的预充电电压,并对节点80施加预充电电压。

在时刻t2到时刻t5,与变形例1的情况同样地,使电流源电路50A-50C依次存储基于基准电流i1的电压。在时刻t5,EN信号及开关SWX的控制信号成为低电平。通过使EN信号为低电平,基准电流源I1不生成基准电流i1。通过使基准电流i1的生成停止,能够降低耗电。通过使开关SWX断开来解除基准电流源I1与节点80之间的连接,能够经由基准电流源I1防止节点80的电压下降。在时刻t6,使开关SWO1-SWO3接通,由此电流源电路50A-50C将基于基准电流i1的电流供给到读出电路100。

图10的(c)是表示变形例2的电流源电路50和其周边电路的动作例的时序图。在图10的(c)所示的例子中,在开关SWS1的接通结束后立即使开关SWO1接通,同样地,在开关SWS2、SWS3的接通结束后立即分别使开关SWO2、SWO3接通。

(变形例3)

图11的(a)是表示变形例3的电流源电路50和其周边电路的结构的图。在变形例3的摄像元件3中,具备基准电流源电路31A-31C。基准电流源电路31A-31C构成为分别包含基准电流源I1-I3。基准电流源I1-I3生成分别为不同的电流值的基准电流i1-i3。变形例3的电流源电路50由分别与图3所示的电流源30及存储部32相同的电流源及存储部构成。

在本变形例中,能够对向各电流源电路50供给的基准电流进行切换。在图11的(a)中,电流源电路50仅图示了3个(电流源电路50A-50C)。根据向构成各电流源电路50的开关SWD输入的控制信号的特性等来切换预先供给的基准电流,由此能够控制由各电流源电路50生成的电流的波动。

图11的(b)是表示变形例3的电流源电路50和其周边电路的动作例的时序图。此外,虽省略图示,但开关SWD与开关SWS同时接通,且先于开关SWS断开。

在时刻t1,ENa信号及SWXa的控制信号成为高电平,SWSr的控制信号成为高电平。通过使ENa信号为高电平,基准电流源I1成为能够输出基准电流i1的状态。通过使开关SWXa及开关SWSr接通,使预充电部70与基准电流源I1之间连接。预充电部70生成基于基准电流i1的预充电电压,对节点80施加预充电电压。

在时刻t2,SWSr的控制信号成为低电平,SWS1的控制信号成为高电平。通过使开关SWS1接通,经由节点80对电流源电路50A供给基准电流i1,存储基于基准电流i1的电压。同样地,在时刻t3到时刻t5,在电流源电路50B-50C依次存储基于基准电流i1的电压。

在时刻t5,ENa信号及SWXa的控制信号成为低电平,ENb信号及SWXb的控制信号成为高电平,SWSr的控制信号成为高电平。通过使ENb信号为高电平,基准电流源I2成为能够输出基准电流i2的状态。通过使SWXb及SWSr接通,使预充电部70与基准电流源I2之间连接。预充电部70生成基于基准电流i2的预充电电压,对节点80施加预充电电压。

在时刻t6到时刻t9,与时刻t2到t5同样地,在分别与SWS4-SWS6连接的电流源电路50D-50F(未图示)依次存储基于基准电流i2的电压。

在时刻t9,ENb信号及SWXb的控制信号成为低电平,ENc信号及SWXc的控制信号成为高电平,SWSr的控制信号成为高电平。通过使ENc的控制信号为高电平,基准电流源I3成为能够输出基准电流i3的状态。通过使SWXc及SWSr接通,使预充电部70与基准电流源I3之间连接。预充电部70生成基于基准电流i3的预充电电压,对节点80施加预充电电压。

在时刻t10到时刻t13,与时刻t2到t5同样地,在分别与SWS7-SWS9连接的电流源电路50G-50I(未图示)依次存储基于基准电流i3的电压。

在时刻t13,SWO1-SWO9的控制信号同时成为高电平。通过使开关SWO1-SWO9接通,电流源电路50A-50I分别将基于各自存储的电压的电流供给到连接目的地。

(变形例4)

图12的(a)是表示变形例4的电流源电路50和其周边电路的结构的图。变形例4的摄像元件3中还具备开关SWSb。开关SWSb通过其控制信号成为高电平而接通,由此将接地电平施加给各电流源电路50A-50C。变形例4的电流源电路50由分别与图3所示的电流源及存储部相同的电流源及存储部构成。

在仅从摄像元件3的全部像素10中的一部分像素10读出像素信号的情况下,使一部分像素10以外的像素10为非活性,即不使电流源30生成电流,由此能够降低耗电。在电流源30由PMOS晶体管构成的情况下施加电源VDD电平的电压,在电流源30由NMOS晶体管构成的情况下施加接地电平的电压,不使电流源30生成电流。在此,将使电流源30生成电流的像素10设为活性像素,将不使电流源30生成电流的像素10设为非活性像素。

图12的(b)是表示变形例4的像素10的一部分的结构例的图。图12的(b)中,施以阴影线的像素10表示非活性像素,白色的像素10表示活性像素。

例如,从第1帧图像决定成为关注区域的活性像素,在第2帧使非活性像素的存储部32存储成为非活性的电压,并且对活性像素的存储部32的电压进行重新设定,即进行电压的刷新。由于非活性像素的存储部32的电压不需要进行刷新,因此能够缩短电压刷新所需要的时间。例如,在图12的(b)所示的B-B’行中,能够在第3帧以不进行存储部32的电压的刷新。

图12的(c)是表示变形例4的电流源电路50和其周边电路的动作例的时序图。此外,虽省略图示,但开关SWD与开关SWS同时接通,并先于开关SWS断开。

在图12的(c)所示的例子中,从与图12的(b)所示的A-A’行左端的像素10连接的电流源电路(50A)朝向与右端的像素10连接的电流源电路(50J),依次存储基于基准电流i1的电压。在时刻t1,SWSb的控制信号成为高电平,SWS1的控制信号成为高电平。通过使开关SWSb及开关SWS1接通,在电流源电路50A的存储部32A存储接地电平(0V)。

在时刻t2,EN信号及SWX的控制信号成为高电平,SWSb的控制信号成为低电平,SWS2的控制信号成为高电平。通过使EN信号为高电平,基准电流源I1成为能够输出基准电流i1的状态。通过使SWX及SWS2接通,向电流源电路50B供给基准电流i1并存储基于基准电流i1的电压。同样地,在时刻t3到时刻t5,向电流源电路50C-50D(未图示)供给基准电流i1并存储基于基准电流i1的电压。

在时刻t5,EN信号及SWX的控制信号成为低电平,SWSb的控制信号成为高电平,SWS5的控制信号成为高电平。通过使EN信号成为低电平,基准电流源I1停止基准电流i1的生成。通过使SWSb及SWS5接通,在电流源电路50E(未图示)存储接地电平。同样地,在时刻t6到时刻t7,在电流源电路50F(未图示)存储接地电平。

在时刻t7,EN信号及SWX的控制信号成为高电平,SWSb的控制信号成为低电平,SWS7的控制信号成为高电平。通过使SWX及SWS7接通,向电流源电路50G(未图示)供给基准电流i1并存储基于基准电流i1的电压。同样地,在时刻t8到时刻t10,向电流源电路50H-50I(未图示)供给基准电流i1并设定基于基准电流i1的电压。

在时刻t10,EN信号及SWX的控制信号成为低电平,SWSb的控制信号成为高电平,SWS10的控制信号成为高电平。通过使SWSb及SWS10接通,在电流源电路50J(未图示)存储接地电平。

在时刻t12,使开关SWO1-SWO10接通,由此电流源电路50A-50J生成基于各自的存储部32中存储的电压的电流并供给到连接目的地。

(变形例5)

在上述实施方式中,说明了各电流源30由1个晶体管构成的例子。但是,也可以如图13的(a)-(d)所示的例子那样,通过多个晶体管M10及M20的级联(cascode)连接而构成。通过使电流源30为晶体管的级联结构,由此能够提高电流源30的输出阻抗,能够抑制电流源30供给的电流的变动。

图13的(a)-(d)是表示变形例5的电流源30和其周边电路的结构的图。图14的(a)-(c)是表示变形例5的电流源30和其周边电路的动作例的时序图。在图13的(a)所示的例子中,电流源30及其周边电路由基准电流源I1及I2、晶体管M10、M20、M70、开关SWS、SWD、SWO、SWC、电容器C1及C2构成。晶体管M70被供给基于基准电流源I2的基准电流i2,并生成基于基准电流i2和晶体管M70的阈值电压的电压V2。

如图14的(a)所示,在时刻t1,SWC接通,由此向电容器C2和晶体管M20的栅极端子供给电压V2。而且,通过使SWS及SWD接通,由此在电容器C1存储基于由基准电流源I1产生的基准电流i1和晶体管M10的阈值电压的电压V1。在时刻t2,开关SWD断开,由此在电容器C1保持电压V1。在时刻t3,开关SWC及SWS断开,在电容器C2保持电压V2。在时刻t4,开关SWO接通,电流源30将电流供给到连接目的地。

在图13的(b)所示的例子中,相对于图13的(a)则电容器C2的连接目的地不同。如图14的(b)所示,在时刻t1,与图13的(a)同样地,在电容器C2和晶体管M20的栅极端子设定电压V2。在电容器C2将电容器C1的电位和晶体管M10的栅极端子的电位作为基准来存储电压V2。而且,与图13的(a)同样地,在电容器C1存储电压V1。

在时刻t2,开关SWD断开,由此在电容器C1保持电压V1。在时刻t3,开关SWS断开,在时刻t4,开关SWC断开,由此在电容器C2保持电压V2。在时刻t5,电流源30将电流供给到连接目的地。

在图13的(c)-(d)所示的例子中,电流源30及其周边电路由基准电流源I1、晶体管M10、M20、开关SWS、SWD、SWO、SWC和电容器C1及C2构成。在电容器C1存储基于基准电流i1和晶体管M10的阈值电压的电压V1,在电容器C2存储基于基准电流i1和晶体管M20的阈值电压的电压V2。在图13的(c)所示的例子中,在电容器C2将接地的电位作为基准而存储电压V2。在图13的(d)所示的例子中,在电容器C2将电容器C1的电位和晶体管M10的栅极端子的电位作为基准而存储电压V2。图13的(c)、(d)所示的各开关的接通断开控制相同,输入图14的(c)所示的控制信号。

如图14的(c)所示,在时刻t1,在电容器C2存储电压V2,在电容器C1存储电压V1。在时刻t2,开关SWD断开,由此在电容器C1保持电压V1。在时刻t3,开关SWC断开,从而在电容器C2保持电压V2。在时刻t4,开关SWS断开,在时刻t5开关SWO接通,由此电流源30将电流供给到连接目的地。

(变形例6)

摄像元件3可以由1个半导体衬底构成,也可以为将多个半导体衬底层叠的结构。摄像元件3例如具备:设有读出电路100的第1半导体衬底、和设有第1存储部32及供给部130的第2半导体衬底。

在上述实施方式及变形例中,示出了摄像元件3中包含的像素信号的读出电路100和将像素信号转换为数字信号的模拟/数字转换电路的比较器电路21的电流源,但不限于此。电流源30也能够适用为摄像元件3中包含的电子电路以外的其他源极跟随器电路的电流源。而且,电流源30还能够适用于源极跟随器电路以外的电子电路。

在上述说明中,说明了各种实施方式及变形例,但本发明不限定于这些内容。在本发明技术思想的范围内所考虑到的其他方式也包含在本发明的范围内。

上述实施方式及变形例还包含以下那样的摄像元件及电流源电路。

(1)一种摄像元件,具备:读出电路,其将根据经光电转换得到的电荷所生成的信号读出到信号线;保持电路,其保持基于来自电源电路的电流的电压;以及电流源,其包括晶体管,该晶体管具有与上述信号线连接的漏极部、和与上述保持电路及上述漏极部连接的栅极部,电流源将根据上述保持电路保持的电压所生成的电流供给到上述信号线。

(2)在(1)的摄像元件中,上述保持电路具有:第1保持部,其保持基于来自上述电源电路的电流的电压;供给部,其供给根据被上述第1保持部保持的电压所生成的电流;以及第2保持部,其保持基于从上述供给部供给的电流的电压,上述电流源将根据被上述第2保持部保持的电压所生成的电流供给到上述信号线。

(3)在(2)的摄像元件中,上述保持电路具有设在上述供给部与上述第2保持部之间的控制部,该控制部进行控制,以使得与没有通过上述读出电路将上述信号读出到上述信号线时相比,在通过上述读出电路将上述信号读出到上述信号线时从上述电源电路流到上述第1保持部的电流更小。

(4)在(2)或(3)的摄像元件中,上述保持电路在通过上述读出电路将上述信号读出到上述信号线时,在上述第1保持部保持基于来自上述电源电路的电流的电压。

(5)在(2)或(3)的摄像元件中,上述第1保持部及上述供给部设在第2半导体衬底,所述第2半导体衬底是与设有上述读出电路的第1半导体衬底不同的衬底。

(6)在(5)的摄像元件中,上述第2半导体衬底层叠在上述第1半导体衬底层叠上。

(7)一种摄像装置,其具有(1)至(6)的摄像元件。

(8)摄像元件,具备:第1读出电路,其将根据经光电转换得到的电荷所生成的第1信号读出到第1信号线;第2读出电路,其将根据经光电转换得到的电荷所生成的第2信号读出到第2信号线;第1保持电路,其保持基于来自电源电路的电流的电压;第2保持电路,其保持基于来自上述电源电路的电流的电压;第1电流源,其包含第1晶体管,该第1晶体管具有与上述第1信号线连接的第1漏极部和与上述第1保持电路及上述第1漏极部连接的第1栅极部,该第1电流源将根据被上述第1保持电路保持的电压所生成的电流供给到上述第1信号线;以及第2电流源,其包括第2晶体管,该第2晶体管具有与上述第2信号线连接的第2漏极部、和与上述第2保持电路及上述第2漏极部连接的第2栅极部,该第2晶体管将根据被上述第2保持电路保持的电压所生成的电流供给到上述第2信号线。

(9)在(8)的摄像元件中,在上述第1保持电路中保持了基于来自上述电源电路的电流的电压之后,上述第2保持电路保持基于来自上述电源电路的电流的电压。

(10)在(8)或(9)的摄像元件中,上述第1保持电路具有第1控制部,该第1控制部进行控制,以使得与没有通过上述第1读出电路将上述第1信号读出到上述第1信号线时相比,在由上述第1读出电路将上述第1信号读出到上述第1信号线时来自上述电源电路的电流更小,上述第2保持电路具有第2控制部,该第2控制部进行控制,以使得与没有通过上述第2读出电路将上述第2信号读出到上述第2信号线时相比,在通过上述第2读出电路将上述第2信号读出到上述第2信号线时来自上述电源电路的电流更小。

(11)在(8)的摄像元件中,上述第1保持电路具有:第1保持部,其对基于来自上述电源电路的电流的电压进行保持;第1供给部,其输出根据在上述第1保持部中存储的电压生成的电流;以及第2保持部,其对基于从上述第1供给部供给的电流的电压进行保持,上述第2保持电路具有:第3保持部,其对基于来自上述电源电路的电流的电压进行保持;第2供给部,其输出由在上述第3保持部存储的电压所生成的电流;以及第4保持部,其对基于从上述第2供给部供给的电流的电压进行保持,上述第1电流源将根据被上述第2保持部保持的电压所生成的电流供给到上述第1信号线,上述第2电流源将根据被上述第4保持部保持的电压所生成的电流供给到上述第2信号线。

(12)在(11)的摄像元件中,上述第1保持电路具有设在上述第1供给部与上述第2保持部之间的第1控制部,该第1控制部进行控制,以使得与没有通过上述第1读出电路将上述第1信号读出到上述第1信号线时相比,在通过上述第1读出电路将上述第1信号读出到上述第1信号线时从上述电源电路流到上述第2保持部的电流更小,上述第2保持电路具有设在上述第2供给部与上述第4保持部之间的第2保持部,该第2保持部进行控制,以使得与没有通过上述第2读出电路将上述第2信号读出到上述第2信号线时相比,在通过上述第2读出电路将上述第2信号读出到上述第2信号线时从上述电源电路流到上述第4保持部的电流更小。

(13)在(11)或(12)的摄像元件中,上述第1保持电路在通过上述第1读出电路将上述第1信号读出到上述第1信号线时,在上述第1保持部保持基于来自上述电源电路的电流的电压,上述第2保持电路在通过上述第2读出电路将上述第2信号读出到上述第2信号线时,在上述第4保持部保持基于来自上述电源电路的电流的电压。

(14)在(11)至(13)的摄像元件中,在上述第1保持部中保持了基于来自上述电源电路的电流的电压之后,上述第3保持部保持基于来自上述电源电路的电流的电压。

(15)在(11)至(14)的摄像元件中,上述第1保持部、上述第2保持部、上述第1供给部及上述第2供给部设在第2半导体衬底,该第2半导体衬底是与设有上述第1读出电路及上述第2读出电路的第1半导体衬底不同的衬底。

(16)在(15)的摄像元件中,上述第2半导体衬底层叠在上述第1半导体衬底层叠上。

(17)一种摄像装置,具备(8)至(16)的摄像元件。

(18)一种电子设备,具备:具有多个电子零部件的电子电路;对基于来自电源电路的电流的电压进行保持的保持电路;以及电流源,其包括晶体管,该晶体管具有与所述电子电路连接的漏极部、和与所述保持电路及所述漏极部连接的栅极部,所述电流源将根据被所述保持电路保持的电压生成的电流供给到所述电子电路。

(19)在(18)的电子设备中,还具备设在所述电源电路与所述保持电路之间的第1控制部和第2控制部,该第1控制部和第2控制部对从所述电源电路到所述保持电路之间的电连接进行控制,所述保持电路及所述漏极部经由所述第1控制部连接,所述电源电路及所述第1控制部经由所述第2控制部连接。

(20)在(18)或(19)的电子设备中,所述保持电路具有:对基于来自所述电源电路的电流的电压进行保持的第1保持部;供给根据被所述第1保持部保持的电压生成的电流的供给部;对基于从所述供给部供给的电流的电压进行保持的第2保持部,所述电流源将根据被所述第2保持部保持的电压生成的电流供给到所述电子电路。

(21)在(20)的电子设备中,所述保持电路在所述电子电路进行动作时,在所述第1保持部保持基于来自所述电源电路的电流的电压。

(22)在(18)到(21)的电子设备中,所述电源电路包含供给电流值不同的电流的多个电流源电路,所述保持电路对基于来自所述多个电流源电路中的所选择的电流源电路的电流的电压进行保持。

(23)在(18)到(22)的电子设备中,还具备第3保持部,该第3保持部禁止所述电流源向所述电子电路的电流供给动作。

(24)在(23)的电子设备中,所述第3控制部接地。

(25)在(18)到(24)的电子设备中,所述电流源通过包含所述晶体管在内的多个晶体管以级联连接构成。

(26)在(20)到(21)的电子设备中,所述第1保持部及所述供给部设于第2半导体衬底,该第2半导体衬底是与设有所述电子电路的第1半导体衬底不同的衬底。

(27)在(26)的电子设备中,所述第2半导体衬底层叠在所述第1半导体衬底层叠上。

(28)在(18)到(27)的电子设备中,所述电子电路是读出根据经光电转换得到的电荷生成的信号的读出电路。

(29)在(18)到(27)的电子设备中,所述电子电路是构成将模拟信号转换为数字信号的转换部的比较器。

另外,上述实施方式及变形例还包括以下的摄像元件及摄像装置。

(1)一种摄像元件,具备:读出电路,其将根据经光电转换得到的电荷所生成的信号读出到信号线;存储电路,其存储基于来自基准电流源的电流的电压;以及电流源,其是将用于由上述读出电路读出上述信号的电流供给到上述信号线的电流源,该电流源将根据由上述存储电路存储的电压所生成的电流供给到上述信号线。

(2)在(1)的摄像元件中,上述存储电路具有:存储基于来自上述基准电流源的电流的电压的第1存储部;供给根据在上述第1存储部存储的电压生成的电流的供给部;以及存储基于从上述供给部供给的电流的电压的第2存储部,上述电流源将根据在上述第2存储部存储的电压所生成的电流供给到上述信号线。

(3)在(2)的摄像元件中,上述存储电路具有设在上述供给部与上述第2存储部之间的调节部,该调节部进行调节,以使得与没有通过上述读出电路将上述信号读出到上述信号线时相比,在通过上述读出电路将上述信号读出到上述信号线时从上述基准电流源流到上述第1存储部的电流更小。

(4)在(3)的摄像元件中,上述存储电路在通过上述读出电路将上述信号读出到上述信号线时将基于来自上述基准电流源的电流的电压存储到上述第1存储部。

(5)在(1)到(4)的摄像元件中,上述电流源具有晶体管,该晶体管包括与上述信号线连接的漏极部、和与上述存储电路及上述漏极部连接的栅极部。

(6)在(2)到(4)的摄像元件中,上述第1存储部及上述供给部设在第2半导体衬底,该第2半导体衬底是与设有上述读出电路的第1半导体衬底不同的衬底。

(7)在(6)的摄像元件中,上述第2半导体衬底层叠在上述第1半导体衬底上。

(8)一种摄像装置,其具备(1)至(7)的摄像元件。

(9)一种摄像元件,具备:第1读出电路,其将根据经光电转换得到的电荷生成的第1信号读出到第1信号线;第2读出电路,其将根据经光电转换得到的电荷生成的第2信号读出到第2信号线;第1存储电路,其存储基于来自基准电流源的电流的电压;第2存储电路,其存储基于来自上述基准电流源的电流的电压;第1电流源,其是将用于由上述第1读出电路读出上述第1信号的电流供给到上述第1信号线的电流源,该第1电流源将根据在上述第1存储电路存储的电压所生成的电流供给到上述第1信号线;第2电流源,其是将用于由上述第2读出电路读出上述第2信号的电流供给到上述第2信号线的电流源,该第2电流源将根据在上述第2存储电路存储的电压生成的电流供给到上述第2信号线。

(10)在(9)的摄像元件中,在上述第1存储电路中存储了基于来自上述基准电流源的电流的电压之后,上述第2存储电路存储基于来自上述基准电流源的电流的电压。

(11)在(9)或(10)的摄像元件中,上述第1存储电路具有第1调节部,该第1调节部进行调节,以使得与没有通过上述第1读出电路将上述第1信号读出到上述第1信号线时相比,在通过上述第1读出电路将上述第1信号读出到上述第1信号线时来自上述基准电流源的电流更小,上述第2存储电路具有第2调节部,该第2调节部进行调节,以使得与没有通过上述第2读出电路将上述第2信号读出到上述第2信号线时相比,在通过上述第2读出电路将上述第2信号读出到上述第2信号线时来自上述基准电流源的电流更小。

(12)在(9)的摄像元件中,上述第1存储电路具有:第1存储部,其存储基于来自上述基准电流源的电流的电压;第1供给部,其将根据在上述第1存储部存储的电压生成的电流输出;以及第2存储部,其存储基于从上述第1供给部供给的电流的电压,上述第2存储电路具有:第3存储部,其存储基于来自上述基准电流源的电流的电压;第2供给部,其将根据在上述第3存储部存储的电压生成的电流输出;以及第4存储部,其存储基于从上述第2供给部供给的电流的电压,上述第1电流源将根据在上述第2存储部存储的电压生成的电流供给到上述第1信号线,上述第2电流源将根据在上述第4存储部存储的电压生成的电流供给到上述第2信号线。

(13)在(12)的摄像元件中,上述第1存储电路具有设在上述第1供给部与上述第2存储部之间的第1调节部,该第1调节部进行调节,以使得与没有通过上述第1读出电路将上述第1信号读出到上述第1信号线时相比,在通过上述第1读出电路将上述第1信号读出到上述第1信号线时从上述基准电流源流到上述第2存储部的电流更小,上述第2存储电路具有设在上述第2供给部与上述第4存储部之间的第2调节部,该第2调节部进行调节,以使得在没有通过上述第2读出电路将上述第2信号读出到上述第2信号线时相比,在通过上述第2读出电路将上述第2信号读出到上述第2信号线时从上述基准电流源流到上述第4存储部的电流更小。

(14)在(12)或(13)的摄像元件中,上述第1存储电路在通过第1读出电路将上述第1信号读出到上述第1信号线时将基于来自上述基准电流源的电流的电压存储到上述第1存储部,上述第2存储电路在通过上述第2读出电路将上述第2信号读出到上述第2信号线时将基于来自上述基准电流源的电流的电压存到上述第4存储部。

(15)在(12)到(14)的摄像元件中,在上述第1存储部中存储了基于来自上述基准电流源的电流的电压之后,上述第3存储部存储基于来自上述基准电流源的电流的电压。

(16)在(9)到(15)的摄像元件中,上述第1电流源具有第1晶体管,该第1晶体管包括与上述第1信号线连接的第1漏极部、和与上述第1存储电路及上述第1漏极部连接的第1栅极部,上述第2电流源具有第2晶体管,该第2晶体管包括与上述第2信号线连接的第2漏极部、和与上述第2存储电路及上述第2漏极部连接的第2栅极部。

(17)在(12)到(15)的摄像元件中,上述第1存储部、上述第2存储部、上述第1供给部及上述第2供给部设在第2半导体衬底,该第2半导体衬底是与设有上述第1读出电路及上述第2读出电路的第1半导体衬底不同的衬底。

(18)在(17)的摄像元件中,上述第2半导体衬底层叠在上述第1半导体衬底层叠上。

(19)一种摄像装置,具备(9)到(18)的摄像元件。

下述的优先权基础申请的公开内容作为引用内容而组入到本说明书中。

日本国专利申请2015年第195279号(2015年9月30日申请)

附图标记说明

3摄像元件、17信号线、30电流源、100读出电路、110存储电路。

- 固态摄像元件、固态摄像元件的制造方法、光电转换元件、摄像装置和电子设备

- 摄像元件、摄像元件的控制方法、摄像装置和电子设备